用于低电压高速串行链路的判决反馈均衡器的制作方法

- 国知局

- 2024-08-02 15:34:28

本公开的方面总体上涉及均衡器,并且更具体地,涉及判决反馈均衡器。背景技术:在系统中,数据可通过串行链路从发射器发射到接收器。可使用码元来发射数据,其中每个码元携带数据比特。由于串行链路中的非理想性(例如,由于反射导致的串行链路的频率响应中的陷波),接收器处的传入码元失真。该失真可导致码元扩展到彼此中,从而导致接收器处的码元间干扰(isi)。接收器可采用判决反馈均衡来减少isi。

背景技术

0、背景

技术实现思路

1、以下内容呈现了对一个或多个具体实施的简要概括,以便提供对这样的具体实施的基本的理解。该概括不是对全部预期具体实施的详尽概述,并且不旨在于标识全部具体实施的关键或重要元素,也不旨在于描绘任何或全部具体实施的范围。其唯一的目的是以简化的形式介绍一个或多个具体实施的一些概念,作为随后介绍的更详细的描述的序言。

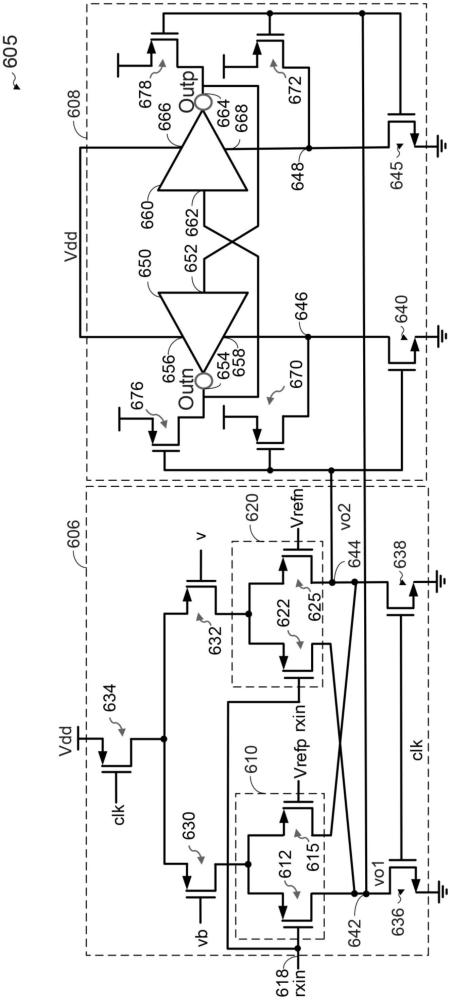

2、第一方面涉及一种比较器。该比较器包括输入级和再生级。该输入级包括:第一输入电路,该第一输入电路耦合到第一节点和第二节点;第一开关晶体管,该第一开关晶体管被配置为如果先前比特值为一,则启用第一输入电路;第二输入电路,该第二输入电路耦合到第一节点和第二节点;以及第二开关晶体管,该第二开关晶体管被配置为如果先前比特值为零,则启用第二输入电路。该再生级包括:第一反相器;与第一反相器交叉耦合的第二反相器;耦合到第一反相器的第一驱动晶体管,其中第一驱动晶体管的栅极耦合到第二节点;以及耦合到第二反相器的第二驱动晶体管,其中第二驱动晶体管的栅极耦合到第一节点。

3、第二方面涉及一种操作比较器的方法。该比较器包括输入级和再生级。该再生级包括第一反相器、与第一反相器交叉耦合的第二反相器、耦合到第一反相器的第一驱动晶体管,以及耦合到第二反相器的第二驱动晶体管,其中第二驱动晶体管的栅极耦合到输入级的第一节点,并且第一驱动晶体管的栅极耦合到输入级的第二节点。该方法包括:如果先前比特值为一,则将输入电压与第一比较电压进行比较,以及基于输入电压与第一比较电压的比较而在第一节点上生成第一电压并且在第二节点上生成第二电压。该方法还包括:如果先前比特值为零,则将输入电压与第二比较电压进行比较,以及基于输入电压与第二比较电压的比较而在第一节点上生成第一电压并且在第二节点上生成第二电压。

4、第三方面涉及一种系统。该系统包括比较器和锁存器。该比较器包括输入级和再生级。该输入级包括:第一输入电路,该第一输入电路耦合到第一节点和第二节点;第一开关晶体管,该第一开关晶体管被配置为如果先前比特值为一,则启用第一输入电路;第二输入电路,该第二输入电路耦合到第一节点和第二节点;以及第二开关晶体管,该第二开关晶体管被配置为如果先前比特值为零,则启用第二输入电路。该再生级包括第一反相器和与第一反相器交叉耦合的第二反相器,其中比较器的第一输出端耦合到第二反相器的输出端,并且比较器的第二输出端耦合到第一反相器的输出端。该再生级还包括:耦合到第一反相器的第一驱动晶体管,其中第一驱动晶体管的栅极耦合到第二节点;以及耦合到第二反相器的第二驱动晶体管,其中第二驱动晶体管的栅极耦合到第一节点。该锁存器具有第一输入端和第二输入端,其中锁存器的第一输入端耦合到比较器的第一输出端,并且锁存器的第二输入端耦合到比较器的第二输出端。

技术特征:1.一种比较器,所述比较器包括:

2.根据权利要求1所述的比较器,其中所述输入级和所述再生级并联布置在供电轨与地之间。

3.根据权利要求1所述的比较器,其中所述第一输入电路包括:

4.根据权利要求3所述的比较器,其中所述第一输入晶体管包括第一p型场效应晶体管(pfet),并且所述第二输入晶体管包括第二pfet。

5.根据权利要求4所述的比较器,其中:

6.根据权利要求3所述的比较器,其中所述第一输入晶体管包括第一n型场效应晶体管(nfet),并且所述第二输入晶体管包括第二nfet。

7.根据权利要求6所述的比较器,其中:

8.根据权利要求3所述的比较器,其中所述第二输入晶体管的所述栅极耦合到数模转换器(dac),其中所述dac被配置为生成所述第一比较电压。

9.根据权利要求3所述的比较器,其中所述第二输入电路包括:

10.根据9所述的比较器,其中:

11.根据权利要求9所述的比较器,其中:

12.根据权利要求11所述的比较器,所述比较器还包括偏移消除电路,其中所述偏移消除电路包括:

13.根据权利要求1所述的比较器,所述比较器还包括偏移消除电路,其中所述偏移消除电路包括:

14.根据权利要求13所述的比较器,其中:

15.根据权利要求1所述的比较器,所述比较器还包括第三开关晶体管,所述第三开关晶体管耦合在所述第一开关晶体管与地之间并且耦合在所述第二开关晶体管与所述地之间,其中所述第三开关晶体管的栅极被配置为接收时钟信号。

16.根据权利要求15所述的比较器,所述比较器还包括:

17.根据权利要求1所述的比较器,所述比较器还包括第三开关晶体管,所述第三开关晶体管耦合在所述第一开关晶体管与供电轨之间并且耦合在所述第二开关晶体管与所述供电轨之间,其中所述第三开关晶体管的栅极被配置为接收时钟信号。

18.根据权利要求17所述的比较器,所述比较器还包括:

19.根据权利要求1所述的比较器,其中所述先前比特值基于由所述比较器进行的先前比特判决。

20.根据权利要求1所述的比较器,其中所述先前比特值基于由与所述比较器时间交错的另一比较器进行的先前比特判决。

21.根据权利要求20所述的比较器,其中:

22.一种操作比较器的方法,所述比较器包括第一反相器、与所述第一反相器交叉耦合的第二反相器、耦合到所述第一反相器的第一驱动晶体管,以及耦合到所述第二反相器的第二驱动晶体管,其中所述第二驱动晶体管的栅极耦合到第一节点,并且所述第一驱动晶体管的栅极耦合到第二节点,所述方法包括:

23.根据权利要求22所述的方法,其中:

24.根据权利要求22所述的方法,其中所述比较器还包括耦合到所述第二节点的第一偏移晶体管和耦合到所述第一节点的第二偏移晶体管,并且所述方法还包括:

25.根据权利要求24所述的方法,其中:

26.根据权利要求22所述的方法,其中:

27.根据权利要求26所述的方法,其中所述第一输入晶体管和所述第二输入晶体管中的每一者包括相应的p型场效应晶体管(pfet),并且所述第一驱动晶体管和所述第二驱动晶体管中的每一者包括相应的n型场效应晶体管(nfet)。

28.根据权利要求26所述的方法,其中所述第一输入晶体管和所述第二输入晶体管中的每一者包括相应的n型场效应晶体管(nfet),并且所述第一驱动晶体管和所述第二驱动晶体管中的每一者包括相应的p型场效应晶体管(pfet)。

29.根据权利要求26所述的方法,其中:

30.根据权利要求22所述的方法,其中所述先前比特值基于由所述比较器进行的先前比特判决。

31.根据权利要求22所述的方法,其中所述先前比特值基于由与所述比较器时间交错的另一比较器进行的先前比特判决。

32.一种系统,所述系统包括:

33.根据权利要求32所述的系统,其中所述输入级和所述再生级并联布置在供电轨与地之间。

34.根据权利要求32所述的系统,其中所述第一输入电路包括:

35.根据权利要求34所述的系统,其中所述第二输入电路包括:

36.根据权利要求34所述的系统,所述系统还包括:

37.根据权利要求32所述的系统,其中所述锁存器包括置位-复位(sr)锁存器。

38.根据权利要求32所述的系统,所述系统还包括耦合到所述锁存器的解串器。

技术总结在某些方面中,一种比较器包括输入级和再生级。该输入级包括:第一输入电路,该第一输入电路耦合到第一节点和第二节点;第一开关晶体管,该第一开关晶体管被配置为如果先前比特值为一,则启用第一输入电路;第二输入电路,该第二输入电路耦合到第一节点和第二节点;以及第二开关晶体管,该第二开关晶体管被配置为如果先前比特值为零,则启用第二输入电路。该再生级包括:第一反相器;与第一反相器交叉耦合的第二反相器;耦合到第一反相器的第一驱动晶体管,其中第一驱动晶体管的栅极耦合到第二节点;以及耦合到第二反相器的第二驱动晶体管,其中第二驱动晶体管的栅极耦合到第一节点。技术研发人员:D·瓦莱,P·伊萨卡尼安受保护的技术使用者:高通股份有限公司技术研发日:技术公布日:2024/7/23本文地址:https://www.jishuxx.com/zhuanli/20240801/246699.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表