一种时钟恢复方法、相关装置以及系统与流程

- 国知局

- 2024-10-21 14:25:07

本技术涉及通信,尤其涉及一种时钟恢复方法、相关装置以及系统。

背景技术:

1、光传送网络(optical transport network,otn),是指为客户层信号提供光域处理的传送网络,主要的功能包括传送、复用、选路、监视和生存性功能。由于稳定性高且可用带宽大,光纤作为数字数据的传输媒介正变得越来越普及。例如,通过大约几百米的光纤进行短距互连在计算机系统、数据中心和园区网中广泛使用。因此,迫切需要用于长距离传输的高容量光收发器,其中,各种方案间的主要权衡包括性能、成本和功耗。许多长距光收发器以100g比特/秒(gigabit per second,gb/s)或更高的速率进行操作。

2、为了将数据传输比特率提高,可以同时提高信令速率和信道数量,其中一种方式为光纤中的光通道执行偏振复用(polarization division multiplex,pdm)技术,pdm技术是指利用光的偏振维度,同一波长信道中通过光的两个相互正交偏振态同时传输两路独立数据信息达到加倍系统总容量和频谱利用率。

3、在光模块中通过探测信号的高频时钟分量以及信道对称性方式实现确定时钟误差(或者称为定时误差),然后再根据得到的时钟误差控制对信号的采样,实现信号的时钟恢复。当前,一种常见的时钟恢复方法如下:在时钟环路中嵌入偏振解复用模块,偏振解复用模块用于执行消除偏振串扰处理。首先,将信号分为x偏振态信号(简称为x偏振信号)和y偏振态信号(简称为y偏振信号),x偏振态与y偏振态相互正交。其次,偏振解复用模块分别对x偏振信号和y偏振信号进行偏振解复用处理,得到两路偏振解复用信号。再次,根据偏振解复用信号,时钟误差检测模块(timing error detector,ted)确定时钟误差,模数转换器(analogy digital convertor,adc)根据该时钟误差控制对信号的采样。再次,偏振解复用模块对两路偏振解复用信号分别进行信道均衡处理,以补偿信道损伤,得到对应的两路均衡信号。最后,根据两路均衡信号计算均衡误差,该均衡误差反馈至偏振解复用模块,更新偏振解复用模块。

4、申请人研究发现,上述方法中偏振解复用模块的性能受限于均衡误差的准确性,而均衡误差的准确性由偏振解复用模块决定。换言之,当偏振解复用模块的性能较差时,均衡误差的准确性较差。由该准确性较差的均衡误差反馈调整偏振解复用模块,无法提升偏振解复用模块的性能。因此,上述方法存在时钟恢复效果差等问题。

技术实现思路

1、第一方面,本技术实施例提出一种时钟恢复方法,包括:

2、对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;

3、根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制对所述第一模拟信号的信号采样处理;

4、对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;

5、根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制对所述第二模拟信号的信号采样处理。

6、具体的,第一模拟信号可以来自集成相干光接收机(icr);第一模拟信号也可以来自振荡器。第一模拟信号为模拟电信号。第二模拟信号可以来自集成相干光接收机(icr);第二模拟信号也可以来自振荡器。第一模拟信号和第二模拟信号为模拟电信号。

7、一种可能的实现方式中,第一模拟信号属于x偏振信号,此时,第二模拟信号与第一模拟信号同属于x偏振信号。换言之,第一模拟信号的偏振态为x偏振态,第二模拟信号的偏振态为y偏振态。

8、又一种可能的实现方式中,第一模拟信号属于y偏振信号,此时,第二模拟信号与第一模拟信号同属于y偏振信号。换言之,第一模拟信号的偏振态为y偏振态,第二模拟信号的偏振态为y偏振态。

9、一种可能的实现方式中,第一模拟信号为i信号,此时,第二模拟信号为q信号。

10、又一种可能的实现方式中,第一模拟信号为q信号,此时,第二模拟信号为i信号。

11、本技术实施例中,通过上述方法,将同一偏正态的模拟信号分为同相i信号和正交q信号,然后分别对i信号和q信号进行信号采样处理得到两路数字信号。对两路数字信号分别进行处理得到相互独立的两个时钟误差,然后分别针对每个时钟误差生成一个控制信号。所生成的两个控制信号分别独立控制对i信号或q信号的信号采样处理。基于i信号和q信号分别独立进行时钟恢复,有效提升时钟恢复效果。降低器件的时延公差要求,消除i信号的时延和q信号的时延对系统性能影响,提高鲁棒性和稳定性。

12、结合第一方面,在第一方面的一种可能的实现方式中,根据所述第一数字信号和所述第二数字信号,生成第三数字信号,所述第三数字信号为i信号和q信号的复信号;根据所述第三数字信号和训练序列,确定目标时延,所述训练序列包括的信号作为确定所述目标时延的过程中所述第三数字信号的参考信号;根据所述目标时延对所述第一数字信号和所述第二数字信号进行时延校准。

13、具体的,将第一数字信号和第二数字信号进行相对±m位移得到2m+1个复信号,m为整数,该复信号称为第三数字信号。一种可能的实现方式中,通过以下方法生成第三数字信号,第三数字信号包括:mc=i1,n+c+jq1,n,c∈[-m,m];其中,i1,n+c为所述第一数字信号,q1,n为所述第二数字信号,n为信号采样时刻序号,m为整数。

14、训练序列包括的信号作为确定目标时延的过程中第三数字信号的参考信号。例如,训练序列为接收端生成的信号序列,接收端生成训练序列时的训练规则为预先配置的。该训练序列可以是接收端根据发送端的发送信号生成的信号序列。该训练序列也可以是接收端与发送端协商生成的信号序列,本技术实施例对此不作限制。

15、本技术实施例中,通过上述方法可有效补偿i信号和q信号因为独立进行信号采样处理造成的iq时延误差,保障系统稳定性和鲁棒性。

16、结合第一方面,在第一方面的一种可能的实现方式中,根据所述第三数字信号和所述训练序列,确定所述目标时延,包括:根据所述第三数字信号和所述训练序列进行互相关操作,得到互相关序列;根据所述互相关序列,计算得到所述互相关序列的峰均功率比;根据所述互相关序列的峰均功率比,确定所述目标时延,其中,所述目标时延为所述互相关序列的峰均功率比的最大值对应的位移量。

17、具体的,根据第三数字信号和训练序列进行互相关(cross-correlation)操作,得到互相关序列。互相关序列可表示为:xc=xccor(mc,ts);其中,mc为所述第三数字信号,ts为所述训练序号,xccor为互相关函数。得到互相关序列后,根据互相关序列计算得到互相关序列的峰均功率比(peak average power ratio,papr)。具体的,分别确定互相关序列的最大值和互相关序列的平均值,然后根据互相关序列的最大值和互相关序列的平均值,计算得到互相关序列的峰均功率比。示例性的,该互相关序列的峰均功率比可表示为:c∈[-m,m];其中,e(xc)为所述互相关序列的平均值,max(xc)所述互相关序列的最大值,m为整数。根据互相关序列的峰均功率比,确定目标时延。具体的,目标时延为互相关序列的峰均功率比的最大值对应的位移量。换言之,上述互相关序列的papr组成的papr序列中确定最大值,该papr序列的最大值对应的位移量作为目标时延。通过上述方法确定的目标时延,有效提升时延校准效果,提升系统稳定性和鲁棒性。

18、结合第一方面,在第一方面的一种可能的实现方式中,根据所述目标时延对所述第一数字信号和所述第二数字信号进行时延校准,包括:根据所述目标时延,确定第三控制信号,所述第三控制信号用于对所述第一数字信号进行时延校准;根据所述目标时延,确定第四控制信号,所述第四控制信号用于对所述第二数字信号进行时延校准。

19、本技术实施例中,根据目标时延可分别确定第三控制信号和第四控制信号,通过第三控制信号和第四控制信号分别对第一数字信号和第二数字信号进行时延校准,可有效补偿i信号和q信号因为独立进行信号采样处理造成的iq时延误差,保障系统稳定性和鲁棒性。

20、结合第一方面,在第一方面的一种可能的实现方式中,根据所述目标时延,确定所述第三控制信号,包括:当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;当所述目标时延为负数时,所述第三控制信号的电压值为0;根据所述目标时延,确定所述第四控制信号,包括:当所述目标时延为正数时,所述第四控制信号的电压值为0;当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延。

21、结合第一方面,在第一方面的一种可能的实现方式中,根据所述目标时延,确定所述第三控制信号,包括:当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;当所述目标时延为负数时,所述第三控制信号的电压值为0;根据所述目标时延,确定所述第四控制信号,包括:当所述目标时延为正数时,所述第四控制信号的电压值为0;当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延的绝对值。

22、结合第一方面,在第一方面的一种可能的实现方式中,根据所述互相关序列,计算得到所述互相关序列的峰均功率比,包括:确定所述互相关序列的最大值;确定所述互相关序列的平均值;根据所述互相关序列的最大值和所述互相关序列的平均值,计算得到所述互相关序列的峰均功率比。

23、结合第一方面,在第一方面的一种可能的实现方式中,所述对所述第一数字信号进行处理,得到所述第一时钟误差,包括:根据第一符号位置的所述第一数字信号,和,第二符号位置的所述第一数字信号,确定所述第一时钟误差,所述第一符号位置与所述第二符号位置之间相差z个符号,z为大于或等于1的整数;所述对所述第二数字信号进行处理,得到所述第二时钟误差,包括:根据所述第一符号位置的所述第二数字信号,和,所述第二符号位置的所述第二数字信号,确定所述第二时钟误差。

24、通过上述方法确定数字信号的时钟误差,进而通过反馈控制的方式根据该时钟误差确定adc的采样相位,从而消除adc采样对系统的影响。可提升所确定的时钟误差的准确度,进而提升时钟恢复效果。

25、结合第一方面,在第一方面的一种可能的实现方式中,所述第一时钟误差,包括:

26、ei=i1,n-zsign(i1,n)-i1,nsign(i1,n-z);

27、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n-z为所述第二符号位置的所述第一数字信号,sign为符号函数;

28、或者,所述第一时钟误差,包括:

29、ei=|i1,n+i1,n+z|(|i1,n|-|i1,n+z|);

30、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n+z为所述第二符号位置的所述第一数字信号。

31、结合第一方面,在第一方面的一种可能的实现方式中,所述第二时钟误差,包括:

32、eq=q1,n-zsign(q1,n)-q1,nsign(q1,n-z);

33、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n-z为所述第二符号位置的所述第二数字信号,sign为符号函数;

34、或者,所述第二时钟误差,包括:

35、eq=|q1,n+q1,n+z|(|q1,n|-|q1,n+z|);

36、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n+z为所述第二符号位置的所述第二数字信号。

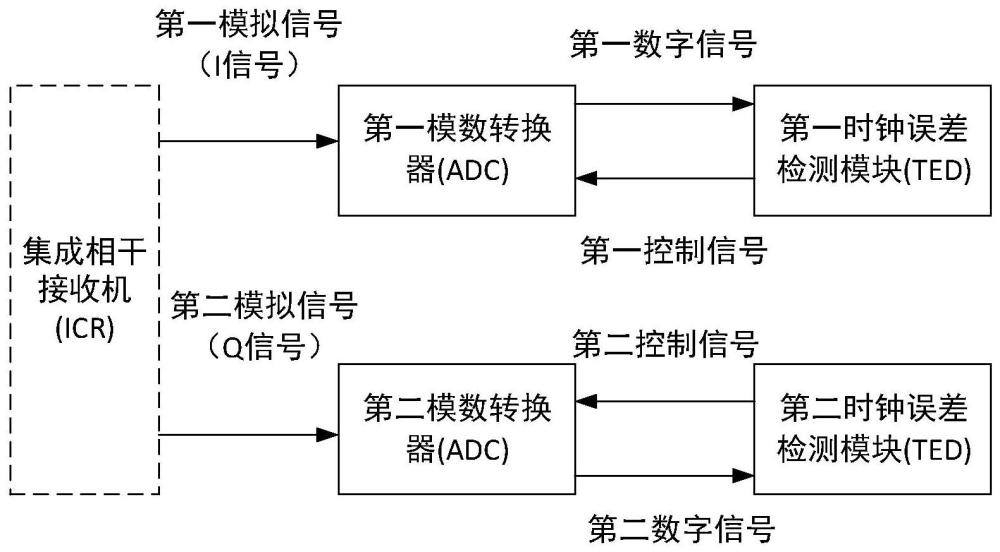

37、第二方面,本技术实施例提出一种时钟恢复装置,包括:第一模数转换器adc,第二adc,第一时钟误差检测模块ted,以及第二ted;所述第一ted对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由所述第一adc对第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;所述第一ted根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制所述第一adc对所述第一模拟信号的信号采样处理;所述第二ted对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由所述第二adc对第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;所述第二ted根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制所述第二ted对所述第二模拟信号的信号采样处理。

38、具体的,icr输出的两路模拟信号,分别是第一模拟信号和第二模拟信号,第一模拟信号和第二模拟信号同属一个偏振信号。例如,第一模拟信号和第二模拟信号同属于x偏振信号,或者,第一模拟信号和第二模拟信号同属于y偏振信号。

39、在一种可能的实现方式中,第一adc对第一模拟信号进行信号采样处理的速率为第一模拟信号的波特率,有效降低adc的采样率。第二adc对第二模拟信号进行信号采样处理的速率为第二模拟信号的波特率,有效降低adc的采样率。

40、在一种可能的实现方式中,第一ted和第二ted采用改进穆勒鉴相算法确定第一时钟误差和第二时钟误差。具体的,改进穆勒鉴相算法利用时域上相邻的两个模拟信号以及这两个模拟信号的符号信息,确定时钟误差。

41、在又一种可能的实现方式中,第一ted和第二ted采用绝对值时钟鉴相算法确定第一时钟误差和第二时钟误差。具体的,绝对值时钟鉴相算法利用时域上相邻的两个模拟信号的幅度和功率信息,确定时钟误差。

42、示例性的,第一ted和第二ted可以通过数字信号处理器(digital signalprocessing,dsp)实现。

43、本技术实施例中,通过上述时钟恢复装置将同一偏正态的模拟信号分为同相i信号和正交q信号,然后分别对i信号和q信号进行信号采样处理得到两路数字信号。对两路数字信号分别进行处理得到相互独立的两个时钟误差,然后分别针对每个时钟误差生成一个控制信号。所生成的两个控制信号分别独立控制对i信号或q信号的信号采样处理。基于i信号和q信号分别独立进行时钟恢复,有效提升时钟恢复效果。降低器件的时延公差要求,消除i信号的时延和q信号的时延对系统性能影响,提高鲁棒性和稳定性。

44、结合第二方面,在第二方面的一种可能的实现方式中,所述时钟恢复装置还包括:同步模块和时延模块;所述同步模块根据所述第一数字信号和所述第二数字信号,生成第三数字信号,所述第三数字信号为i信号和q信号的复信号;所述同步模块根据所述第三数字信号和训练序列,确定目标时延,所述训练序列包括的信号作为确定所述目标时延的过程中所述第三数字信号的参考信号;所述时延模块根据所述目标时延对所述第一数字信号和所述第二数字信号进行时延校准。

45、示例性的,同步模块和时延模块可以通过数字信号处理器(digital signalprocessing,dsp)实现,例如第一ted、第二ted、同步模块和时延模块通过dsp实现。

46、本技术实施例中,通过同步模块和时延模块,补偿i信号和q信号因为独立进行信号采样处理造成的iq时延误差,提升系统稳定性和鲁棒性。

47、结合第二方面,在第二方面的一种可能的实现方式中,所述同步模块根据所述第三数字信号和所述训练序列进行互相关操作,得到互相关序列;所述同步模块根据所述互相关序列,计算得到所述互相关序列的峰均功率比;所述同步模块根据所述互相关序列的峰均功率比,确定所述目标时延,其中,所述目标时延为所述互相关序列的峰均功率比的最大值对应的位移量。

48、本技术实施例中,同步模块通过上述方法确定的目标时延,有效提升时延校准效果,提升系统稳定性和鲁棒性。

49、结合第二方面,在第二方面的一种可能的实现方式中,所述时延模块包括第一时延模块和第二时延模块;所述同步模块根据所述目标时延,确定第三控制信号;所述第一时延模块根据所述第三控制信号对所述第一数字信号进行时延校准;所述同步模块根据所述目标时延,确定第四控制信号;所述第二时延模块所述第四控制信号用于对所述第二数字信号进行时延校准。

50、结合第二方面,在第二方面的一种可能的实现方式中,所述第三数字信号,包括:

51、mc=i1,n+c+jq1,n,c∈[-m,m];

52、其中,i1,n+c为所述第一数字信号,q1,n为所述第二数字信号,n为信号采样时刻序号,m为整数。

53、结合第二方面,在第二方面的一种可能的实现方式中,所述时延模块包括第一时延模块和第二时延模块;

54、所述同步模块根据所述目标时延,确定所述第三控制信号,包括:

55、当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;

56、当所述目标时延为负数时,所述第三控制信号的电压值为0;

57、所述第一时延模块根据所述第三控制信号对所述第一数字信号进行时延校准;

58、所述同步模块根据所述目标时延,确定所述第四控制信号,包括:

59、当所述目标时延为正数时,所述第四控制信号的电压值为0;

60、当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延;

61、所述第二时延模块根据所述第四控制信号用于对所述第二数字信号进行时延校准。

62、结合第二方面,在第二方面的一种可能的实现方式中,所述时延模块与所述第一adc合设,所述时延模块与所述第二adc合设;

63、所述同步模块根据所述目标时延,确定所述第三控制信号,包括:

64、当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;

65、当所述目标时延为负数时,所述第三控制信号的电压值为0;

66、所述第一adc根据所述第三控制信号对所述第一数字信号进行时延校准;

67、根据所述目标时延,确定所述第四控制信号,包括:

68、当所述目标时延为正数时,所述第四控制信号的电压值为0;

69、当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延的绝对值;

70、所述第二adc根据所述第四控制信号用于对所述第二数字信号进行时延校准。

71、结合第二方面,在第二方面的一种可能的实现方式中,所述互相关序列,包括:

72、xc=xccor(mc,ts);

73、其中,mc为所述第三数字信号,ts为所述训练序号,xccor为互相关函数。

74、结合第二方面,在第二方面的一种可能的实现方式中,所述同步模块确定所述互相关序列的最大值;

75、所述同步模块确定所述互相关序列的平均值;

76、所述同步模块根据所述互相关序列的最大值和所述互相关序列的平均值,计算得到所述互相关序列的峰均功率比。

77、结合第二方面,在第二方面的一种可能的实现方式中,所述互相关序列的峰均功率比,包括:

78、

79、其中,e(xc)为所述互相关序列的平均值,max(xc)所述互相关序列的最大值,m为整数。

80、结合第二方面,在第二方面的一种可能的实现方式中,所述第一ted根据第一符号位置的所述第一数字信号,和,第二符号位置的所述第一数字信号,确定所述第一时钟误差,所述第一符号位置与所述第二符号位置之间相差z个符号,z为大于或等于1的整数;

81、所述第二ted根据所述第一符号位置的所述第二数字信号,和,所述第二符号位置的所述第二数字信号,确定所述第二时钟误差。

82、结合第二方面,在第二方面的一种可能的实现方式中,所述第一时钟误差,包括:

83、ei=i1,n-zsign(i1,n)-i1,nsign(i1,n-z);

84、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n-z为所述第二符号位置的所述第一数字信号,sign为符号函数;

85、或者,所述第一时钟误差,包括:

86、ei=|i1,n+i1,n+z|(|i1,n|-|i1,n+z|);

87、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n+z为所述第二符号位置的所述第一数字信号。

88、结合第二方面,在第二方面的一种可能的实现方式中,所述第二时钟误差,包括:

89、eq=q1,n-zsign(q1,n)-q1,nsign(q1,n-z);

90、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n-z为所述第二符号位置的所述第二数字信号,sign为符号函数;

91、或者,所述第二时钟误差,包括:

92、eq=|q1,n+q1,n+z|(|q1,n|-|q1,n+z|);

93、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n+z为所述第二符号位置的所述第二数字信号。

94、第三方面,本技术实施例提出一种时钟恢复装置,该时钟恢复装置包括:

95、处理器,用于对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;

96、处理器,还用于根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制对所述第一模拟信号的信号采样处理;

97、处理器,还用于对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;

98、处理器,还用于根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制对所述第二模拟信号的信号采样处理。

99、在一种可能的实现方式中,

100、处理器,还用于根据所述第一数字信号和所述第二数字信号,生成第三数字信号,所述第三数字信号为i信号和q信号的复信号;

101、处理器,还用于根据所述第三数字信号和训练序列,确定目标时延,所述训练序列包括的信号作为确定所述目标时延的过程中所述第三数字信号的参考信号;

102、处理器,还用于根据所述目标时延对所述第一数字信号和所述第二数字信号进行时延校准。

103、在一种可能的实现方式中,

104、处理器,还用于根据所述第三数字信号和所述训练序列进行互相关操作,得到互相关序列;

105、处理器,还用于根据所述互相关序列,计算得到所述互相关序列的峰均功率比;

106、处理器,还用于根据所述互相关序列的峰均功率比,确定所述目标时延,其中,所述目标时延为所述互相关序列的峰均功率比的最大值对应的位移量。

107、在一种可能的实现方式中,

108、处理器,还用于根据所述目标时延,确定第三控制信号,所述第三控制信号用于对所述第一数字信号进行时延校准;

109、处理器,还用于根据所述目标时延,确定第四控制信号,所述第四控制信号用于对所述第二数字信号进行时延校准。

110、在一种可能的实现方式中,所述第三数字信号,包括:

111、mc=i1,n+c+jq1,n,c∈[-m,m];

112、其中,i1,n+c为所述第一数字信号,q1,n为所述第二数字信号,n为信号采样时刻序号,m为整数。

113、在一种可能的实现方式中,处理器,还用于根据所述目标时延,确定所述第三控制信号,包括:

114、当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;

115、当所述目标时延为负数时,所述第三控制信号的电压值为0;

116、处理器,还用于根据所述目标时延,确定所述第四控制信号,包括:

117、当所述目标时延为正数时,所述第四控制信号的电压值为0;

118、当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延。

119、在一种可能的实现方式中,处理器,还用于根据所述目标时延,确定所述第三控制信号,包括:

120、当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;

121、当所述目标时延为负数时,所述第三控制信号的电压值为0;

122、处理器,还用于根据所述目标时延,确定所述第四控制信号,包括:

123、当所述目标时延为正数时,所述第四控制信号的电压值为0;

124、当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延的绝对值。

125、在一种可能的实现方式中,所述互相关序列,包括:

126、xc=xccor(mc,ts);

127、其中,mc为所述第三数字信号,ts为所述训练序号,xccor为互相关函数。

128、在一种可能的实现方式中,处理器,还用于确定所述互相关序列的最大值;

129、处理器,还用于确定所述互相关序列的平均值;

130、处理器,还用于根据所述互相关序列的最大值和所述互相关序列的平均值,计算得到所述互相关序列的峰均功率比。

131、在一种可能的实现方式中,所述互相关序列的峰均功率比,包括:

132、

133、其中,e(xc)为所述互相关序列的平均值,max(xc)所述互相关序列的最大值,m为整数。

134、在一种可能的实现方式中,处理器,还用于根据第一符号位置的所述第一数字信号,和,第二符号位置的所述第一数字信号,确定所述第一时钟误差,所述第一符号位置与所述第二符号位置之间相差z个符号,z为大于或等于1的整数;

135、处理器,还用于根据所述第一符号位置的所述第二数字信号,和,所述第二符号位置的所述第二数字信号,确定所述第二时钟误差。

136、在一种可能的实现方式中,所述第一时钟误差,包括:

137、ei=i1,n-zsign(i1,n)-i1,nsign(i1,n-z);

138、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n-z为所述第二符号位置的所述第一数字信号,sign为符号函数;

139、或者,所述第一时钟误差,包括:

140、ei=|i1,n+i1,n+z|(|i1,n|-|i1,n+z|);

141、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n+z为所述第二符号位置的所述第一数字信号。

142、在一种可能的实现方式中,所述第二时钟误差,包括:

143、eq=q1,n-zsign(q1,n)-q1,nsign(q1,n-z);

144、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n-z为所述第二符号位置的所述第二数字信号,sign为符号函数;

145、或者,所述第二时钟误差,包括:

146、eq=|q1,n+q1,n+z|(|q1,n|-|q1,n+z|);

147、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n+z为所述第二符号位置的所述第二数字信号。

148、第四方面,本技术实施例提出一种时钟恢复装置,该时钟恢复装置包括:

149、处理模块,用于对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;

150、处理模块,还用于根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制对所述第一模拟信号的信号采样处理;

151、处理模块,还用于对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;

152、处理模块,还用于根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制对所述第二模拟信号的信号采样处理。

153、在一种可能的实现方式中,

154、处理模块,还用于根据所述第一数字信号和所述第二数字信号,生成第三数字信号,所述第三数字信号为i信号和q信号的复信号;

155、处理模块,还用于根据所述第三数字信号和训练序列,确定目标时延,所述训练序列包括的信号作为确定所述目标时延的过程中所述第三数字信号的参考信号;

156、处理模块,还用于根据所述目标时延对所述第一数字信号和所述第二数字信号进行时延校准。

157、在一种可能的实现方式中,

158、处理模块,还用于根据所述第三数字信号和所述训练序列进行互相关操作,得到互相关序列;

159、处理模块,还用于根据所述互相关序列,计算得到所述互相关序列的峰均功率比;

160、处理模块,还用于根据所述互相关序列的峰均功率比,确定所述目标时延,其中,所述目标时延为所述互相关序列的峰均功率比的最大值对应的位移量。

161、在一种可能的实现方式中,

162、处理模块,还用于根据所述目标时延,确定第三控制信号,所述第三控制信号用于对所述第一数字信号进行时延校准;

163、处理模块,还用于根据所述目标时延,确定第四控制信号,所述第四控制信号用于对所述第二数字信号进行时延校准。

164、在一种可能的实现方式中,所述第三数字信号,包括:

165、mc=i1,n+c+jq1,n,c∈[-m,m];

166、其中,i1,n+c为所述第一数字信号,q1,n为所述第二数字信号,n为信号采样时刻序号,m为整数。

167、在一种可能的实现方式中,处理模块,还用于根据所述目标时延,确定所述第三控制信号,包括:

168、当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;

169、当所述目标时延为负数时,所述第三控制信号的电压值为0;

170、处理模块,还用于根据所述目标时延,确定所述第四控制信号,包括:

171、当所述目标时延为正数时,所述第四控制信号的电压值为0;

172、当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延。

173、在一种可能的实现方式中,处理模块,还用于根据所述目标时延,确定所述第三控制信号,包括:

174、当所述目标时延为正数时,所述第三控制信号的电压值等于所述目标时延;

175、当所述目标时延为负数时,所述第三控制信号的电压值为0;

176、处理模块,还用于根据所述目标时延,确定所述第四控制信号,包括:

177、当所述目标时延为正数时,所述第四控制信号的电压值为0;

178、当所述目标时延为负数时,所述第四控制信号的电压值等于所述目标时延的绝对值。

179、在一种可能的实现方式中,所述互相关序列,包括:

180、xc=xccor(mc,ts);

181、其中,mc为所述第三数字信号,ts为所述训练序号,xccor为互相关函数。

182、在一种可能的实现方式中,处理模块,还用于确定所述互相关序列的最大值;

183、处理模块,还用于确定所述互相关序列的平均值;

184、处理模块,还用于根据所述互相关序列的最大值和所述互相关序列的平均值,计算得到所述互相关序列的峰均功率比。

185、在一种可能的实现方式中,所述互相关序列的峰均功率比,包括:

186、

187、其中,e(xc)为所述互相关序列的平均值,max(xc)所述互相关序列的最大值,m为整数。

188、在一种可能的实现方式中,处理模块,还用于根据第一符号位置的所述第一数字信号,和,第二符号位置的所述第一数字信号,确定所述第一时钟误差,所述第一符号位置与所述第二符号位置之间相差z个符号,z为大于或等于1的整数;

189、处理模块,还用于根据所述第一符号位置的所述第二数字信号,和,所述第二符号位置的所述第二数字信号,确定所述第二时钟误差。

190、在一种可能的实现方式中,所述第一时钟误差,包括:

191、ei=i1,n-zsign(i1,n)-i1,nsign(i1,n-z);

192、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n-z为所述第二符号位置的所述第一数字信号,sign为符号函数;

193、或者,所述第一时钟误差,包括:

194、ei=|i1,n+i1,n+z|(|i1,n|-|i1,n+z|);

195、其中,i1,n为所述第一符号位置的所述第一数字信号,i1,n+z为所述第二符号位置的所述第一数字信号。

196、在一种可能的实现方式中,所述第二时钟误差,包括:

197、eq=q1,n-zsign(q1,n)-q1,nsign(q1,n-z);

198、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n-z为所述第二符号位置的所述第二数字信号,sign为符号函数;

199、或者,所述第二时钟误差,包括:

200、eq=|q1,n+q1,n+z|(|q1,n|-|q1,n+z|);

201、其中,q1,n为所述第一符号位置的所述第二数字信号,q1,n+z为所述第二符号位置的所述第二数字信号。

202、第五方面,本技术实施例提出一种光模块,该光模块执行前述第一方面的中任一种可能的方法,或者,该光模块包括前述第二方面中任一种可能的时钟恢复装置。

203、第六方面,本技术实施例提出一种光接收机,该光接收机包括前述第五方面中的光模块。

204、第七方面,本技术实施例提供了一种存储一个或多个计算机执行指令的计算机可读存储介质,当该计算机执行指令被处理器执行时,该处理器执行如前述第一方面或第二方面中任意一种可能的实现方式。

205、第八方面,本技术实施例提供一种存储一个或多个计算机执行指令的计算机程序产品(或称计算机程序),当该计算机执行指令被该处理器执行时,该处理器执行前述第一方面任意一种可能的实现方式。

206、第九方面,本技术提供了一种芯片系统,该芯片系统包括处理器,用于支持计算机设备实现上述方面中所涉及的功能。在一种可能的设计中,该芯片系统还包括存储器,该存储器,用于保存计算机设备必要的程序指令和数据。该芯片系统,可以由芯片构成,也可以包括芯片和其他分立器件。

207、第十方面,本技术实施例提供了一种芯片系统,该芯片系统包括至少一个处理器和通信接口,通信接口和至少一个处理器通过线路互联,至少一个处理器用于运行计算机程序或指令,以进行第一方面的方法。

208、其中,芯片系统中的通信接口可以为输入/输出接口、管脚或电路等。

209、第十一方面,本技术实施例提出一种光系统,该光系统包括前述第六方面的光接收机。

210、第十二方面,本技术实施例提出一种时钟恢复方法,包括:

211、对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;

212、根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制对所述第一模拟信号的信号采样处理;

213、对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;

214、根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制对所述第二模拟信号的信号采样处理;

215、对所述第一数字信号进行色散补偿,得到第五数字信号;

216、对所述第二数字信号进行色散补偿,得到第六数字信号;

217、对所述第五数字信号和所述第六数字信号进行处理,得到第一色散补偿值和第二色散补偿值,所述第一色散补偿值用于对所述第一数字信号进行色散补偿,所述第二色散补偿值用于对所述第二数字信号进行色散补偿。

218、本技术实施例中,通过上述装置,将同一偏正态的模拟信号分为同相i信号和正交q信号,然后分别对i信号和q信号进行信号采样处理得到两路数字信号。对两路数字信号分别进行处理得到相互独立的两个时钟误差,然后分别针对每个时钟误差生成一个控制信号。所生成的两个控制信号分别独立控制对i信号或q信号的信号采样处理。基于i信号和q信号分别独立进行时钟恢复,有效提升时钟恢复效果。降低器件的时延公差要求,消除i信号的时延和q信号的时延对系统性能影响,提高鲁棒性和稳定性。分别对i信号和q信号进行色散补偿,提升色散容忍,提升装置所适用的信号波段范围,例如可适用c波段和o波段。通过色散补偿,消除色散对时钟算法恶化的影响,保障系统稳定性和鲁棒性。

219、在一种可能的实现方式中,对所述第一数字信号进行色散补偿,得到所述第五数字信号,包括:对所述第一数字信号进行时延补偿,得到第七数字信号;对所述第七数字信号进行色散补偿,得到所述第五数字信号;

220、对所述第二数字信号进行色散补偿,得到所述第六数字信号,包括:对所述第二数字信号进行时延补偿,得到第八数字信号;对所述第八数字信号进行色散补偿,得到所述第六数字信号;

221、对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值和所述第二色散补偿值,包括:对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值、所述第二色散补偿值、第三时钟误差和第四时钟误差,所述第三时钟误差用于对所述第一数字信号进行时延补偿得到所述第七数字信号,所述第四时钟误差用于对所述第二数字信号进行时延补偿得到所述第八数字信号。

222、本技术实施例中,通过i信号和q信号分别独立进行时钟误差补偿和色散补偿,时钟补偿与色散补偿采用级联架构,可同时消除色散和时延对时钟算法恶化的影响,提升系统的稳定性和鲁棒性。

223、在一种可能的实现方式中,对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差,包括:对所述第五数字信号进行时延操作,得到第一信号,所述第一信号为时延扫描信号;对所述第六数字信号进行时延操作,得到第二信号,所述第二信号为时延扫描信号;然后,分别对所述第一信号和所述第二信号进行色散补偿,根据经过色散补偿的第一信号和根据色散补偿的第二信号得到第三信号,所述第三信号为色散扫描信号;计算所述第三信号的峭度;根据所述第三信号的峭度,确定所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

224、本技术实施例中,根据经过色散补偿和时延补偿得到的第五数字信号和第六数字信号,经过处理得到第一信号和第二信号,第一信号和第二信号为时延扫描信号。然后根据第一信号,计算得到第三信号的峭度,第三信号为色散扫描信号。最后根据第三信号的峭度,提升系统的稳定性和鲁棒性。

225、在一种可能的实现方式中,根据所述第三信号的峭度最小值,确定所述峭度最小值对应的所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

226、本技术实施例中,得到多个第三信号的峭度后,每个第三信号的峭度分别与一组色散值和时延值对应。然后,从多个第三信号的峭度中,确定第三信号的峭度最小值。根据该第三信号的峭度最小值,确定对应的色散值和时延值,该色散值和时延值可认为是当前系统(该系统中应用本技术实施例提出的时钟恢复装置)中实际存在的时延值和色散至。因此,根据第三信号的峭度最小值所对应的色散值和时延值,确定对应的第一色散补偿值、第二色散补偿值、第三时钟误差以及第四时钟误差。然后将第一色散补偿值、第二色散补偿值、第三时钟误差以及第四时钟误差分别配置到对应的色散补偿模块以及时延补偿模块。

227、在一种可能的实现方式中,对所述第一数字信号进行处理,得到所述第一时钟误差,包括:对所述第五数字信号进行处理,得到所述第一时钟误差;对所述第二数字信号进行处理,得到所述第二时钟误差,包括:对所述第六数字信号进行处理,得到所述第二时钟误差。进一步提升第一时钟误差的精度和第二时钟误差的精度,提升系统的稳定性和鲁棒性。

228、在一种可能的实现方式中,对所述第五数字信号进行时延操作,得到所述第一信号,包括:

229、通过以下方法计算得到所述第一信号:

230、s1(k)=i2(k),其中,s1(k)为所述第一信号,i2为所述第五数字信号,k为信号序列;

231、对所述第六数字信号进行时延操作,得到所述第二信号,包括:

232、通过以下方法计算得到所述第二信号:

233、s2(k)=q2(k+t(n)),其中,s2(k)为所述第二信号,q2为所述第六数字信号,k为信号序列,t(n)为所述时延操作的时延扫描范围,n为正整数。

234、在一种可能的实现方式中,

235、对所述第一信号和所述第二信号进行色散补偿,得到所述第三信号,包括:

236、s3=i3+jq3,其中,s3为所述第三信号,i3为经过色散补偿的所述第一信号,q3为经过色散补偿的所述第二信号;

237、其中s1(w)为s1的频域表达式,s1为所述第一信号;

238、其中s2(w)为s2的频域表达式,s2为所述第二信号,d为色散系数,l为传输距离,λ为信号中心波长,w是频率分量,l∈(0,ds),ds是色散扫描的最大扫描距离,l(h)为预置参数。

239、在一种可能的实现方式中,计算所述第三信号的峭度,包括:

240、通过以下方法计算得到所述第三信号的峭度:

241、ks=(e((s3*s3*)2)-e(s3*s3)e(s3**s3*)-2e2(s3*s3*))/e2(s3*s3*),其中,s3为所述第三信号,s3*为所述第三信号的信号共轭,ks为所述第三信号的峭度。

242、第十三方面,本技术实施例提出一种时钟恢复装置,包括:第一模数转换器adc,第二adc,第一时钟误差检测模块ted,以及第二ted;

243、所述第一ted对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由所述第一adc对第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;

244、所述第一ted根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制所述第一adc对所述第一模拟信号的信号采样处理;

245、所述第二ted对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由所述第二adc对第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;

246、所述第二ted根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制所述第二ted对所述第二模拟信号的信号采样处理。

247、在一种可能的实现方式中,所述时钟恢复装置还包括第一色散补偿模块、第二色散补偿模块和峭度计算模块;

248、所述第一色散补偿模块对所述第一数字信号进行色散补偿,得到第五数字信号;

249、所述第二色散补偿模块对所述第二数字信号进行色散补偿,得到第六数字信号;

250、所述峭度计算模块对所述第五数字信号和所述第六数字信号进行处理,得到第一色散补偿值和第二色散补偿值,所述第一色散补偿值用于对所述第一数字信号进行色散补偿,所述第二色散补偿值用于对所述第二数字信号进行色散补偿。

251、在一种可能的实现方式中,所述第一色散补偿模块对所述第一数字信号进行色散补偿,得到所述第五数字信号,包括:

252、所述第一色散补偿模块对所述第一数字信号进行时延补偿,得到第七数字信号;

253、所述第一色散补偿模块对所述第七数字信号进行色散补偿,得到所述第五数字信号;

254、所述第二色散补偿模块对所述第二数字信号进行色散补偿,得到所述第六数字信号,包括:

255、所述第二色散补偿模块对对所述第二数字信号进行时延补偿,得到第八数字信号;

256、所述第二色散补偿模块对对所述第八数字信号进行色散补偿,得到所述第六数字信号;

257、所述峭度计算模块对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值和所述第二色散补偿值,包括:

258、所述峭度计算模块对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值、所述第二色散补偿值、第三时钟误差和第四时钟误差,所述第三时钟误差用于对所述第一数字信号进行时延补偿得到所述第七数字信号,所述第四时钟误差用于对所述第二数字信号进行时延补偿得到所述第八数字信号。

259、在一种可能的实现方式中,所述峭度计算模块对所述第五数字信号进行时延操作,得到第一信号,所述第一信号为时延扫描信号;

260、所述峭度计算模块对所述第六数字信号进行时延操作,得到第二信号,所述第二信号为时延扫描信号;

261、所述峭度计算模块对所述第一信号和所述第二信号进行色散补偿,得到第三信号,所述第三信号为色散扫描信号;

262、所述峭度计算模块计算所述第三信号的峭度;

263、所述峭度计算模块根据所述第三信号的峭度,确定所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

264、在一种可能的实现方式中,所述峭度计算模块根据所述第三信号的峭度最小值,确定所述峭度最小值对应的所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

265、在一种可能的实现方式中,所述第一ted对所述第一数字信号进行处理,得到所述第一时钟误差,包括:

266、所述第一ted对所述第五数字信号进行处理,得到所述第一时钟误差;

267、所述第二ted对所述第二数字信号进行处理,得到所述第二时钟误差,包括:

268、所述第二ted对所述第六数字信号进行处理,得到所述第二时钟误差。

269、在一种可能的实现方式中,所述峭度计算模块通过以下方法计算得到所述第一信号:

270、s1(k)=i2(k),其中,s1(k)为所述第一信号,i2为所述第五数字信号,k为信号序列;

271、所述峭度计算模块通过以下方法计算得到所述第二信号:

272、s2(k)=q2(k+t(n)),其中,s2(k)为所述第二信号,q2为所述第六数字信号,k为信号序列,t(n)为所述时延操作的时延扫描范围,n为正整数。

273、在一种可能的实现方式中,所述峭度计算模块通过以下方法计算得到所述第三信号:

274、s3=i3+jq3,其中,s3为所述第三信号,i3为经过色散补偿的所述第一信号,q3为经过色散补偿的所述第二信号;

275、其中s1(w)为s1的频域表达式,s1为所述第一信号;

276、其中s2(w)为s2的频域表达式,s2为所述第二信号,d为色散系数,l为传输距离,λ为信号中心波长,w是频率分量,l∈(0,ds),ds是色散扫描的最大扫描距离,l(h)为预置参数。

277、在一种可能的实现方式中,所述峭度计算模块通过以下方法计算得到所述第三信号的峭度:

278、ks=(e((s3*s3*)2)-e(s3*s3)e(s3**s3*)-2e2(s3*s3*))/e2(s3*s3*),其中,s3为所述第三信号,s3*为所述第三信号的信号共轭,ks为所述第三信号的峭度。

279、需要说明的是,第十三方面中时钟恢复装置的技术效果,请参见第十二方面中的时钟恢复方法的相关技术效果,此处不作赘述。

280、第十四方面,本技术实施例提出一种时钟恢复装置,包括:

281、处理器,还用于对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;

282、处理器,还用于根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制对所述第一模拟信号的信号采样处理;

283、处理器,还用于对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;

284、处理器,还用于根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制对所述第二模拟信号的信号采样处理。

285、在一种可能的实现方式中,

286、处理器,还用于对所述第一数字信号进行色散补偿,得到第五数字信号;

287、处理器,还用于对所述第二数字信号进行色散补偿,得到第六数字信号;

288、处理器,还用于对所述第五数字信号和所述第六数字信号进行处理,得到第一色散补偿值和第二色散补偿值,所述第一色散补偿值用于对所述第一数字信号进行色散补偿,所述第二色散补偿值用于对所述第二数字信号进行色散补偿。

289、在一种可能的实现方式中,

290、处理器,还用于对所述第一数字信号进行色散补偿,得到所述第五数字信号,包括:

291、处理器,还用于对所述第一数字信号进行时延补偿,得到第七数字信号;

292、处理器,还用于对所述第七数字信号进行色散补偿,得到所述第五数字信号;

293、处理器,还用于对所述第二数字信号进行色散补偿,得到所述第六数字信号,包括:

294、处理器,还用于对所述第二数字信号进行时延补偿,得到第八数字信号;

295、处理器,还用于对所述第八数字信号进行色散补偿,得到所述第六数字信号;

296、处理器,还用于对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值和所述第二色散补偿值,包括:

297、处理器,还用于对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值、所述第二色散补偿值、第三时钟误差和第四时钟误差,所述第三时钟误差用于对所述第一数字信号进行时延补偿得到所述第七数字信号,所述第四时钟误差用于对所述第二数字信号进行时延补偿得到所述第八数字信号。

298、在一种可能的实现方式中,

299、处理器,还用于对所述第五数字信号进行时延操作,得到第一信号,所述第一信号为时延扫描信号;

300、处理器,还用于对所述第六数字信号进行时延操作,得到第二信号,所述第二信号为时延扫描信号;

301、处理器,还用于对所述第一信号和所述第二信号进行色散补偿,得到第三信号,所述第三信号为色散扫描信号;

302、处理器,还用于计算所述第三信号的峭度;

303、处理器,还用于根据所述第三信号的峭度,确定所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

304、在一种可能的实现方式中,

305、处理器,还用于根据所述第三信号的峭度最小值,确定所述峭度最小值对应的所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

306、在一种可能的实现方式中,

307、处理器,还用于对所述第一数字信号进行处理,得到所述第一时钟误差,包括:

308、处理器,还用于对所述第五数字信号进行处理,得到所述第一时钟误差;

309、处理器,还用于对所述第二数字信号进行处理,得到所述第二时钟误差,包括:

310、处理器,还用于对所述第六数字信号进行处理,得到所述第二时钟误差。

311、在一种可能的实现方式中,

312、处理器,还用于通过以下方法计算得到所述第一信号:

313、s1(k)=i2(k),其中,s1(k)为所述第一信号,i2为所述第五数字信号,k为信号序列;

314、处理器,还用于通过以下方法计算得到所述第二信号:

315、s2(k)=q2(k+t(n)),其中,s2(k)为所述第二信号,q2为所述第六数字信号,k为信号序列,t(n)为所述时延操作的时延扫描范围,n为正整数。

316、在一种可能的实现方式中,

317、处理器,还用于通过以下方法计算得到所述第三信号:

318、s3=i3+jq3,其中,s3为所述第三信号,i3为经过色散补偿的所述第一信号,q3为经过色散补偿的所述第二信号;

319、其中s1(w)为s1的频域表达式,s1为所述第一信号;

320、其中s2(w)为s2的频域表达式,s2为所述第二信号,d为色散系数,l为传输距离,λ为信号中心波长,w是频率分量,l∈(0,ds),ds是色散扫描的最大扫描距离,l(h)为预置参数。

321、在一种可能的实现方式中,

322、处理器,还用于通过以下方法计算得到所述第三信号的峭度:

323、ks=(e((s3*s3*)2)-e(s3*s3)e(s3**s3*)-2e2(s3*s3*))/e2(s3*s3*),其中,s3为所述第三信号,s3*为所述第三信号的信号共轭,ks为所述第三信号的峭度。

324、第十五方面,本技术实施例提出一种时钟恢复装置,包括:

325、处理模块,还用于对第一数字信号进行处理,得到第一时钟误差,所述第一数字信号由第一模拟信号经过信号采样处理得到,所述第一模拟信号为同相i信号;

326、处理模块,还用于根据所述第一时钟误差,确定第一控制信号,所述第一控制信号用于控制对所述第一模拟信号的信号采样处理;

327、处理模块,还用于对第二数字信号进行处理,得到第二时钟误差,所述第二数字信号由第二模拟信号经过信号采样处理得到,所述第二模拟信号为正交q信号,所述第一模拟信号和所述第二模拟信号同属一个偏振信号;

328、处理模块,还用于根据所述第二时钟误差,确定第二控制信号,所述第二控制信号用于控制对所述第二模拟信号的信号采样处理。

329、在一种可能的实现方式中,

330、处理模块,还用于对所述第一数字信号进行色散补偿,得到第五数字信号;

331、处理模块,还用于对所述第二数字信号进行色散补偿,得到第六数字信号;

332、处理模块,还用于对所述第五数字信号和所述第六数字信号进行处理,得到第一色散补偿值和第二色散补偿值,所述第一色散补偿值用于对所述第一数字信号进行色散补偿,所述第二色散补偿值用于对所述第二数字信号进行色散补偿。

333、在一种可能的实现方式中,

334、处理模块,还用于对所述第一数字信号进行色散补偿,得到所述第五数字信号,包括:

335、处理模块,还用于对所述第一数字信号进行时延补偿,得到第七数字信号;

336、处理模块,还用于对所述第七数字信号进行色散补偿,得到所述第五数字信号;

337、处理模块,还用于对所述第二数字信号进行色散补偿,得到所述第六数字信号,包括:

338、处理模块,还用于对所述第二数字信号进行时延补偿,得到第八数字信号;

339、处理模块,还用于对所述第八数字信号进行色散补偿,得到所述第六数字信号;

340、处理模块,还用于对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值和所述第二色散补偿值,包括:

341、处理模块,还用于对所述第五数字信号和所述第六数字信号进行处理,得到所述第一色散补偿值、所述第二色散补偿值、第三时钟误差和第四时钟误差,所述第三时钟误差用于对所述第一数字信号进行时延补偿得到所述第七数字信号,所述第四时钟误差用于对所述第二数字信号进行时延补偿得到所述第八数字信号。

342、在一种可能的实现方式中,

343、处理模块,还用于对所述第五数字信号进行时延操作,得到第一信号,所述第一信号为时延扫描信号;

344、处理模块,还用于对所述第六数字信号进行时延操作,得到第二信号,所述第二信号为时延扫描信号;

345、处理模块,还用于对所述第一信号和所述第二信号进行色散补偿,得到第三信号,所述第三信号为色散扫描信号;

346、处理模块,还用于计算所述第三信号的峭度;

347、处理模块,还用于根据所述第三信号的峭度,确定所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

348、在一种可能的实现方式中,

349、处理模块,还用于根据所述第三信号的峭度最小值,确定所述峭度最小值对应的所述第一色散补偿值、所述第二色散补偿值、所述第三时钟误差和所述第四时钟误差。

350、在一种可能的实现方式中,

351、处理模块,还用于对所述第一数字信号进行处理,得到所述第一时钟误差,包括:

352、处理模块,还用于对所述第五数字信号进行处理,得到所述第一时钟误差;

353、处理模块,还用于对所述第二数字信号进行处理,得到所述第二时钟误差,包括:

354、处理模块,还用于对所述第六数字信号进行处理,得到所述第二时钟误差。

355、在一种可能的实现方式中,

356、处理模块,还用于通过以下方法计算得到所述第一信号:

357、s1(k)=i2(k),其中,s1(k)为所述第一信号,i2为所述第五数字信号,k为信号序列;

358、处理模块,还用于通过以下方法计算得到所述第二信号:

359、s2(k)=q2(k+t(n)),其中,s2(k)为所述第二信号,q2为所述第六数字信号,k为信号序列,t(n)为所述时延操作的时延扫描范围,n为正整数。

360、在一种可能的实现方式中,

361、处理模块,还用于通过以下方法计算得到所述第三信号:

362、s3=i3+jq3,其中,s3为所述第三信号,i3为经过色散补偿的所述第一信号,q3为经过色散补偿的所述第二信号;

363、其中s1(w)为s1的频域表达式,s1为所述第一信号;

364、其中s2(w)为s2的频域表达式,s2为所述第二信号,d为色散系数,l为传输距离,λ为信号中心波长,w是频率分量,l∈(0,ds),ds是色散扫描的最大扫描距离,l(h)为预置参数。

365、在一种可能的实现方式中,

366、处理模块,还用于通过以下方法计算得到所述第三信号的峭度:

367、ks=(e((s3*s3*)2)-e(s3*s3)e(s3**s3*)-2e2(s3*s3*))/e2(s3*s3*),其中,s3为所述第三信号,s3*为所述第三信号的信号共轭,ks为所述第三信号的峭度。

368、第十六方面,本技术实施例提出一种光模块,该光模块执行前述第十二方面的中任一种可能的方法,或者,该光模块包括前述第十三方面中任一种可能的时钟恢复装置。

369、第十七方面,本技术实施例提出一种光接收机,该光接收机包括前述第十六方面中的光模块。

370、第十八方面,本技术实施例提供了一种存储一个或多个计算机执行指令的计算机可读存储介质,当该计算机执行指令被处理器执行时,该处理器执行如前述第十二方面中任意一种可能的实现方式。

371、第十九方面,本技术实施例提供一种存储一个或多个计算机执行指令的计算机程序产品(或称计算机程序),当该计算机执行指令被该处理器执行时,该处理器执行前述第十二方面任意一种可能的实现方式。

372、第二十方面,本技术提供了一种芯片系统,该芯片系统包括处理器,用于支持计算机设备实现上述方面中所涉及的功能。在一种可能的设计中,该芯片系统还包括存储器,该存储器,用于保存计算机设备必要的程序指令和数据。该芯片系统,可以由芯片构成,也可以包括芯片和其他分立器件。

373、第二十一方面,本技术实施例提供了一种芯片系统,该芯片系统包括至少一个处理器和通信接口,通信接口和至少一个处理器通过线路互联,至少一个处理器用于运行计算机程序或指令,以进行第一方面的方法。

374、其中,芯片系统中的通信接口可以为输入/输出接口、管脚或电路等。

375、第二十二方面,本技术实施例提出一种光系统,该光系统包括前述第十七方面的光接收机。

本文地址:https://www.jishuxx.com/zhuanli/20241021/318075.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表