1.本实用新型涉及芯片测试技术领域,具体涉及一种自动测试验证装置。

背景技术:

2.新型型号为spd5的中转(hub)芯片,是指具有中转功能的规格为ddr5的串行状态检测的电可擦编程只读存储器(eeprom),主要用于内存条上。

3.根据电子元件工业联合会(jedec)下发的关于新型型号为spd5的hub芯片的最新标准,型号为spd5的hub芯片具有1024字节的非易失性内存,支持两线i2c和i3c总线串行接口,支持高达12.5mhz的通信速率,使用1.8v&1.0v电源供电,具有中转功能。

4.然而,用于该种型号为spd5的新型hub芯片测试的测试验证设备还尚未常熟,且该测试验证设备在i2c和i3c的总线串行接口的切换上操作困难,且测试效率低。

技术实现要素:

5.本实用新型的目的是提供一种自动测试验证装置。此装置旨在解决传统测试技术存在测试效率低,操作困难的问题,通过设置上位机自动编码测试脚本,实现自动化的高效测试,保证测试的产品质量和开发进度,方便试验可操作性。

6.为达到上述目的,本实用新型提供了一种自动测试验证装置,包括上位机、mcu模块、fpga模块和测试模块;mcu模块的第一输入端与上位机的输出端连接,用于对上位机发出的测试指令进行指令解析,生成第一解析信息或者第二解析信息;fpga模块的输入端与mcu模块的第一输出端连接,用于对第一解析信息进行指令封装,获得封装测试信息;测试模块内部放置待测芯片,且测试模块的第一输入端与fpga模块的输出端连接,第二输入端与mcu模块的第二输出端连接,输出端与mcu模块的第二输入端连接,根据封装测试信息或者第二解析信息,对待测芯片进行测试验证,生成测试结果,并传输至mcu模块进行解析;mcu模块的第三输出端与上位机的输入端连接,将解析后的测试结果反馈回上位机;上位机根据解析后的测试结果,生成测试报告并呈现给用户,完成待测芯片的自动测试验证。

7.最优选的,该自动测试验证装置还包括采集模块,设置于测试模块与mcu模块之间,用于采集测试结果并传输至mcu模块。

8.最优选的,该自动测试验证装置还包括电源模块,分别与上位机、mcu模块、fpga模块、测试模块和采集模块连接,为各个模块提供电源。

9.最优选的,该自动测试验证装置还包括电平转换模块,设置于fpga模块与测试模块之间,用于对封装测试信息的电平进行自动匹配,使得封装测试信息的电平符合测试模块的电平要求。

10.最优选的,该自动测试验证装置还包括pmu,输入端与电源模块连接,第一输出端与电平转换模块连接,第二输出端与测试模块连接,用于对电源模块提供的电源信息进行处理,分别生成第一电源信息和第二电源信息,并分别传输至电平转换模块和测试模块。

11.最优选的,mcu模块包括:

12.收发模块,第一输入端与上位机的输出端连接,第二输入端与测试模块的第一输出端连接,第一输出端与上位机的输入端连接,用于接收测试指令,并接收测试结果反馈回上位机;

13.adc,第一输入端与测试模块的第二输出端连接,第二输入端与收发模块的第一输出端连接,用于采集待测芯片的电压信息,并根据测试指令,对待测芯片的电压信息进行微调,获得供电电压信息;

14.解析模块,输入端与收发模块的第二输出端连接,对测试指令的指令类型进行解析判断,生成指令判定信息;

15.控制模块,第一输入端与adc的输出端连接,第二输入端与解析模块的输出端连接,第一输出端与fpga模块连接,第二输出端与测试模块的第二输入端连接,根据供电电压信息和指令判定信息,生成第一解析信息或者第二解析信息,并对应传输至fpga模块或者测试模块。

16.最优选的,测试指令的指令类型包括hardware指令、iic指令和i3c指令;当测试指令的指令类型为iic指令或者i3c指令时,指令判定信息为正,控制模块输出第一解析信息,并传输至fpga模块;当测试指令的指令类型为hardware指令,指令判定信息为负,控制模块输出第二解析信息,直接传输至测试模块。

17.最优选的,fpga模块内部包括:

18.iic处理核,与mcu模块的第一输出端连接,对指令类型为iic指令的第一解析信息进行数据封装;

19.i3c处理核,与mcu模块的第二输出端连接,对指令类型为i3c指令的第一解析信息进行数据封装。

20.最优选的,测试结果包括供电电压信息、运行速率、电流信息、温度信息以及湿度信息。

21.最优选的,该自动测试验证装置还包括寄存器,设置于mcu模块与fpga模块之间,用于测量两者之间的慢速静态的电气特性。

22.运用此实用新型,解决了传统测试技术存在测试效率低,操作困难的问题,通过设置上位机自动编码测试脚本,实现了自动化的高效测试,保证了测试的产品质量和开发进度,方便了试验可操作性。

23.相对于现有技术,本实用新型具有以下有益效果:

24.本实用新型提供的自动测试验证装置,通过设置上位机自动编码测试脚本,解决了传统测试技术存在测试效率低,操作困难的问题,实现了自动化的高效测试,保证了测试的产品质量和开发进度,方便了试验可操作性。

附图说明

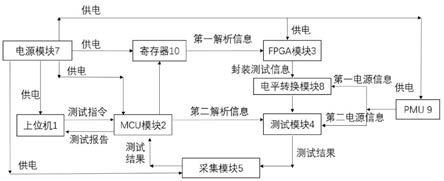

25.图1为本实用新型提供的自动测试验证装置结构示意图;

26.图2为本实用新型提供的mcu模块结构示意图;

27.图3为本实用新型提供的自动测试验证装纸工作流程图。

具体实施方式

28.以下结合附图通过具体实施例对本实用新型作进一步的描述,这些实施例仅用于说明本实用新型,并不是对本实用新型保护范围的限制。

29.本实用新型是一种自动测试验证装置,如图1所示,包括上位机1、微控制单元(mcu)模块2、现场可编辑门列阵(fpga)模块3、测试模块4、采集模块5、电平转换模块8、寄存器10。

30.用户在上位机1中编写测试脚本,并发出测试指令,用于对待测芯片6进行自动测试验证;mcu模块2的第一输入端通过usb接口与上位机1的输出端连接,用于对上位机1发出的测试指令进行指令解析,生成第一解析信息或者第二解析信息。

31.fpga模块3的输入端通过寄存器10与mcu模块2的第一输出端连接,用于对第一解析信息进行指令封装,获得封装测试信息。

32.测试模块4内部放置待测芯片(dut)6,且测试模块4的第一输入端通过电平转换模块8与fpga模块3的输出端连接,第二输入端与mcu模块2的第二输出端连接,输出端通过采集模块5与mcu模块的第二输入端连接,根据封装测试信息或者第二解析信息,对待测芯片6进行测试验证,生成测试结果,并通过采集模块5采集测试结果,并传输至mcu模块进行解析。

33.mcu模块2的第三输出端与上位机1的输入端连接,将解析后的测试结果反馈回上位机1;上位机1根据解析后的测试结果,生成测试报告并呈现给用户,完成待测芯片6的自动测试验证。

34.采集模块5设置于测试模块4与mcu模块2之间,用于采集测试模块4中的待测芯片6的测试结果,并将测试结果传输至mcu模块2中进行解析。

35.寄存器10设置于mcu模块2与fpga模块3之间,用于测量两者之间的慢速静态的电气特性。

36.电平转换模块8设置于fpga模块3与测试模块4之间,用于对封装测试信息的电平进行自动匹配,使得封装测试信息的电平符合测试模块4的电平要求。

37.在本实施例中,电平转换模块8设置有漏极开路(open drain)模式和推挽(push pull)模式两种模式,且两种模式相互切换,使得电平转换器模块8能够实现自动双向电压转换、以及最大40mhz的信号转换。

38.同时,电平转换模块8自动匹配后的封装测试信息的输出电平可以自由设置无需跟随电平转换模块的供电电压而变化。

39.如图1所示,该自动测试验证装置还包括电源模块7,分别与上位机1、mcu模块2、fpga模块3、测试模块4和采集模块5连接,为各个模块提供电源;在本实施例中,电源模块7为12v/3a型号的ac/dc开关电源。

40.如图1所示,该自动测试验证装置还包括电源管理单元(pmu)9,输入端与电源模块7连接,第一输出端与电平转换模块8连接,第二输出端与测试模块4连接,用于对电源模块7提供的电源信息进行处理,分别生成第一电源信息和第二电源信息,并分别传输至电平转换模块8和测试模块4。

41.在本实施例中,第一电源信息和第二电源信息的电压范围为0.7v~3.6v。

42.其中,如图2所示,mcu模块2包括收发模块201、模拟数字转换器(adc)202、解析模

块203和控制模块204。

43.收发模块201的第一输入端与上位机1的输出端连接,用于接收上位机1发出的测试指令;收发模块201的第二输入端与测试模块4的第一输出端连接,第一输出端与上位机1的输入端连接,用于接收测试模块4的测试结果反馈回上位机1。

44.adc 202的第一输入端与测试模块4的第二输出端连接,第二输入端与收发模块201的第一输出端连接,采集测试模块4中待测芯片6的电压信息,并根据上位机1发出的测试指令,对测试模块4中待测芯片6的电压信息进行微调,获得供电电压信息。

45.解析模块203的输入端与收发模块201的第二输出端连接,对测试指令的指令类型进行解析判断,生成指令判定信息。

46.控制模块204的第一输入端与adc 202的输出端连接,第二输入端与解析模块203的输出端连接,第一输出端与fpga模块3连接,第二输出端与测试模块4的第二输入端连接,根据供电电压信息和指令判定信息,生成第一解析信息或者第二解析信息;若控制模块204生成第一解析信息,则对应传输至fpga模块3;若控制模块204生成第二解析信息,则第二解析信息直接传输至测试模块4。

47.其中,上位机1发出的测试指令的指令类型包括hardware指令、iic指令和i3c指令三种。

48.当上位机1发出的测试指令的指令类型为iic指令或者i3c指令时,mcu模块2中解析模块203生成的指令判定信息为正,则控制模块204输出第一解析信息,并传输至fpga模块3;fpga模块3对第一解析信息进行数据封装,生成封装测试信息。

49.当上位机1发出的测试指令的指令类型为hardware指令,mcu模块2中解析模块203生成的指令判定信息为负,则控制模块204输出第二解析信息,直接传输至测试模块4。

50.在本实施例中,adc 202内部设置有两个相互切换的量程,两个量程中的采样电阻均为高精度无感采样电阻,采样量程为0.5μa~20ma,采用低噪声、高精度、差分输入和增益可控的adc,提高了采集精度。

51.fpga模块3内部包括iic处理核301和i3c处理核302;iic处理核301通过iic端口与mcu模块2中的控制模块204的第一输出端连接,用于对指令类型为iic指令的第一解析信息进行数据封装;i3c处理核302通过i3c端口与mcu模块2中的控制模块204的第二输出端连接,用于对指令类型为i3c指令的第一解析信息进行数据封装。

52.测试模块4根据fpga模块3处理后的封装测试信息或者mcu模块2直接传输的第二解析信息,对待测芯片6进行测试验证,生成待测芯片6的测试结果。

53.在本实施例中,如图3所示,用户在上位机1中编写测试脚本,并发出测试指令;mcu模块2中的收发模块201接收上位机1发出的测试指令;mcu模块2中的adc 202采集待测芯片6的电压信息,并根据测试指令,对待测芯片6的电压信息进行微调,获得供电电压信息;mcu模块2中的解析模块203对测试指令的指令类型进行解析判断,生成指令判定信息。

54.若上位机1发出的测试指令的指令类型为iic指令,mcu模块2中解析模块203生成的指令判定信息为正,mcu模块2中的控制模块204输出第一解析信息传输至fpga模块3的iic处理核301,对第一解析信息进行数据封装,生成封装测试信息;测试模块4根据fpga模块3处理后的封装测试信息,对待测芯片6进行测试验证,生成测试结果。

55.若上位机1发出的测试指令的指令类型为i3c指令,mcu模块2中解析模块203生成

的指令判定信息为正,mcu模块2中的控制模块204输出的第一解析信息传输至fpga模块3的i3c处理核302,对第一解析信息进行数据封装,生成封装测试信息;测试模块4根据fpga模块3处理后的封装测试信息,对待测芯片6进行测试验证,生成测试结果。

56.若上位机1发出的测试指令的指令类型为hardware指令,mcu模块2中解析模块202生成的指令判定信息为负,mcu模块2中的控制模块204输出第二解析信息,并直接传输至测试模块4;测试模块4根据mcu模块2直接传输的第二解析信息,对待测芯片6进行测试验证,生成测试结果。

57.测试模块4将测试结果传输至mcu模块2进行解析;mcu模块2将解析后的测试结果反馈回上位机1;上位机1根据解析后的测试结果,生成测试报告并呈现给用户,完成待测芯片的自动测试验证。

58.在本实施例中,待测芯片6的测试结果包括待测芯片6的供电电压信息、运行速率、电流信息、温度信息以及湿度信息。

59.测试模块4的型号与待测芯片6的封装型号有关;在本实施例中,待测芯片6的封装型号为spd5 hub。

60.本实用新型的工作原理:

61.用户在上位机中编写测试脚本,并发出测试指令;mcu模块中的收发模块接收上位机发出的测试指令;mcu模块中的adc采集待测芯片的电压信息,并根据测试指令,对待测芯片的电压信息进行微调,获得供电电压信息;mcu模块中的解析模块对测试指令的指令类型进行解析判断,生成指令判定信息。

62.若测试指令的指令类型为iic指令或者i3c指令,指令判定信息为正,mcu模块中的控制模块根据供电电压信息和指令判定信息,生成第一解析信息,并传输至fpga模块;fpga模块对第一解析信息进行指令封装,获得封装测试信息,传输至测试模块;

63.若测试指令的指令类型为hardware指令,指令判定信息为负,mcu模块中的控制模块根据供电电压信息和指令判定信息,生成第二解析信息,并直接传输至测试模块;

64.测试模块根据封装测试信息或者第二解析信息,对待测芯片进行测试验证,生成测试结果,并传输至mcu模块进行解析;mcu模块将解析后的测试结果反馈回上位机;上位机根据解析后的测试结果,生成测试报告并呈现给用户,完成待测芯片的自动测试验证。

65.综上所述,本实用新型一种自动测试验证装置,解决了传统测试技术存在测试效率低,操作困难的问题,通过设置上位机自动编码测试脚本,实现了自动化的高效测试,保证了测试的产品质量和开发进度,方便了试验可操作性。

66.尽管本实用新型的内容已经通过上述优选实施例作了详细介绍,但应当认识到上述的描述不应被认为是对本实用新型的限制。在本领域技术人员阅读了上述内容后,对于本实用新型的多种修改和替代都将是显而易见的。因此,本实用新型的保护范围应由所附的权利要求来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。