1.本发明是有关于一种半导体装置及其制造方法,且特别是有关于一种三维半导体装置及其制造方法。

背景技术:

2.近来,由于对于更优异的存储器装置的需求已逐渐增加,已提供各种三维(3d)存储器装置,例如是三维与非(3d nand)存储器装置、三维或非存储器装置(3d nor)或三维与存储器装置(3d and)。

3.一般而言,三维存储器装置包括一衬底及设置于衬底上的一叠层结构。叠层结构包括交替叠层的多个绝缘层及多个导电层。并且,三维存储器装置包括阵列区及邻接于阵列区的阶梯区。存储器串列结构及虚拟存储器串列结构可通过相同工艺分别形成于阵列区及阶梯区中。其中,存储器串列结构及虚拟存储器串列结构分别包括由衬底向上延伸的外延成长层。

4.然而,在目前的三维存储器装置中,经常发现阶梯区的部分区域的虚拟存储器串列结构的外延成长层生长情况不佳(例如外延成长层呈歪斜或者高度不够),如此可能产生短路,导致电性问题(例如漏电流)。

技术实现要素:

5.本发明是关于一种半导体装置。半导体装置的阶梯区的本体部包括第一区及第二区。在第一区中,虚拟存储器串列结构所对应的导电层的数量是介于1~10。在第二区中,虚拟存储器串列结构所对应的导电层的数量是大于10。由于在俯视图的一相同的单位面积中,第一区的虚拟存储器串列结构的面积是大于第二区的虚拟存储器串列结构的面积(亦即是第一区的用于形成虚拟存储器串列结构的第一开口的面积大于第二区的用于形成虚拟存储器串列结构的第一开口的面积),在形成包括外延成长层的虚拟存储器串列结构的期间,第一区的排放刻蚀气体的效果优于第二区的排放刻蚀气体的效果,能够减轻第一区的外延成长层受到刻蚀气体的不良影响。因此,相较于第一区的虚拟存储器串列结构的面积没有大于第二区的虚拟存储器串列结构的面积的比较例而言,本发明的第一区的虚拟存储器串列结构的外延成长层可具有较好的生长情况,可防止外延成长层呈歪斜或者高度不够,借此避免产生短路及漏电流的问题。

6.根据本发明的一方面,提出一种半导体装置。半导体装置包括一衬底、设置于衬底上的一叠层结构以及多个虚拟存储器串列结构。叠层结构包括沿着一第一方向交替叠层的多个绝缘层及多个导电层。虚拟存储器串列结构设置于半导体装置的一阶梯区,且沿着第一方向穿过叠层结构,其中阶梯区包括一本体部,且本体部包括相邻的一第一区及一第二区。在第一区中,虚拟存储器串列结构所对应的导电层的数量是介于1~10;在第二区中,虚拟存储器串列结构所对应的导电层的数量是大于10。在一俯视图中,在一相同的单位面积中,第一区的虚拟存储器串列结构的面积是大于第二区的虚拟存储器串列结构的面积。

7.根据本发明的另一方面,提出一种半导体装置的制造方法。半导体装置的制造方法包括下述步骤。首先,提供一衬底以及设置于衬底上的一叠层结构。此后,形成多个第一开口于半导体装置的阶梯区中。叠层结构包括沿着一第一方向交替叠层的多个绝缘层及多个导电层。第一开口沿着第一方向穿过叠层结构,其中阶梯区包括一本体部,且本体部包括相邻的一第一区及一第二区。在第一区中,第一开口所对应的导电层的数量是介于1~10;在第二区中,第一开口所对应的导电层的数量是大于10。在一俯视图中,在一相同的单位面积中,第一区的第一开口的面积是大于第二区的第二开口的面积。

8.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

9.图1a~图2b绘示依照本发明一实施例的半导体装置的制造方法的流程图;

10.图3a绘示依照一比较例的半导体装置的部分俯视图;

11.图3b绘示图3a的a-a'联机的剖面图;

12.图4a绘示依照本发明一实施例的半导体装置的部分俯视图;

13.图4b绘示图4a的a-a'联机的剖面图;

14.图5绘示依照本发明一实施例的半导体装置与比较例的半导体装置的虚拟存储器串列结构的外延成长层的形成高度的曲线图;

15.图6a绘示比较例的半导体装置的异常的虚拟存储器串列结构的外延成长层的扫描结果;

16.图6b绘示依照本发明一实施例的半导体装置的异常的虚拟存储器串列结构的外延成长层的扫描结果;

17.图7绘示依照本发明另一实施例的半导体装置的部分俯视图;

18.图8a绘示依照本发明又一实施例的半导体装置的部分俯视图;

19.图8b绘示图8a的a-a'联机的剖面图;

20.图9a绘示比较例的半导体装置的异常的虚拟存储器串列结构的外延成长层的扫描结果;

21.图9b绘示依照本发明一实施例的半导体装置的异常的虚拟存储器串列结构的外延成长层的扫描结果;

22.图9c绘示依照本发明另一实施例的半导体装置的异常的虚拟存储器串列结构的外延成长层的扫描结果;及

23.图10绘示依照本发明又一实施例的半导体装置的部分俯视图。

24.【符号说明】

25.100,100a,100p,200,300:半导体装置

26.110:衬底

27.110a:上表面

28.112:绝缘层

29.114:导电层

30.116:存储器串列结构

31.116h:阵列开口

32.118,118p,218,318,418:虚拟存储器串列结构

33.118h,118hp,218h,318h,418h:第一开口

34.120:接触结构

35.120':接触结构预定位置

36.1161,1181:外延成长层

37.a,a',b,b':剖面线端点

38.ar:阵列区

39.as:阶梯区

40.as1:本体部

41.as1a:第一区

42.as1b:第二区

43.as2:虚拟部

44.c1~c5,ca1,cb1,ca2,cb2,ca3,cb3,ca4,cb4:中心点

45.r1,r2:排

46.s1:叠层结构

47.ua:单位面积

具体实施方式

48.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

49.在下文的详细描述中,为了便于解释,提供各种的特定细节以整体理解本发明的实施例。然而,应理解的是,一或多个实施例能够在不采用这些特定细节的情况下实现。在其他情况下,为了简化附图,已知的结构及元件系以示意图表示。

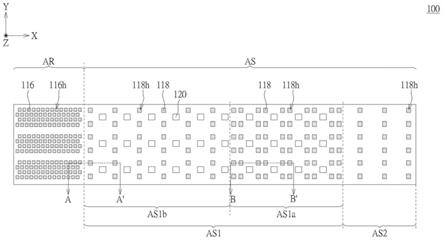

50.图1a~图2b绘示依照本发明一实施例的半导体装置100的制造方法的流程图。其中,图1a及图2a绘示依照本发明一实施例的半导体装置100的制造过程的俯视图。图1b绘示图1a的a-a'联机与b-b'联机的剖面图。图2b绘示图2a的a-a'联机与b-b'联机的剖面图。

51.请同时参照图1a及图1b,提供一衬底110及设置于衬底110上的一叠层结构s1。叠层结构s1例如是沿着第一方向(例如z方向)设置于衬底110的上表面110a上。叠层结构s1包括沿着第一方向(例如z方向)交替叠层的多个绝缘层112及多个导电层114。接着,经由一般的存储器工艺步骤修整导电层114,使得导电层114的边缘部分呈现阶梯状结构,以形成包括阵列区ar及阶梯区as的半导体装置100。此后,通过一相同工艺(例如是刻蚀工艺)分别形成多个阵列开口116h及多个第一开口118h于阵列区ar及阶梯区as中。阵列开口116h及第一开口118h沿着第一方向(例如是z方向)穿过叠层结构s1,并暴露衬底110。

52.阶梯区as包括与阵列区ar电性连接的本体部as1以及不与阵列区ar电性连接的虚拟部as2。在俯视图中,第一开口118h是与本体部as1的接触结构预定位置120'交错设置。并且,阶梯区as的本体部as1包括相邻的第一区as1a及第二区as1b。由于阶梯区as的本体部as1中的导电层114为阶梯状结构,第一开口118h在不同区域所对应的导电层114的数量有所不同。在第一区as1a中,第一开口118h所对应的导电层114的数量是介于1~10,亦即第一

区as1a是对应于第一开口118h穿过最底部的(最邻近于衬底110的)1~10层的导电层114的区域。在第二区as1b中,第一开口118h所对应的导电层114的数量是大于10,亦即第二区as1b是对应于第一开口118h穿过最底部的(最邻近于衬底110的)大于10层的导电层114的区域。举例而言,在第一区as1a中,当第一开口118h所对应的导电层114的数量是10的时候,由底部起算的第10层导电层114的上方是填充绝缘材料而不具有导电层;当第一开口118h所对应的导电层114的数量是5的时候,由最底部起算的第5层导电层114的上方是填充绝缘材料而不具有导电层,以此类堆。在第二区as1b中,当第一开口118h所对应的导电层114的数量是11的时候,由最底部起算的第11层导电层114的上方是填充绝缘材料而不具有导电层;当第一开口118h所对应的导电层114的数量是15的时候,由最底部起算的第15层导电层114的上方是填充绝缘材料而不具有导电层,以此类推。因此,当叙述「第一区as1a中的第一开口118h所对应的导电层114的数量是介于1~10」时,表示第一区as1a中的第一开口118h是存在于由底部起算的导电层114的数量是介于1~10的环境之下;当叙述「第二区as1b中的第一开口118h所对应的导电层114的数量是大于10」时,表示第二区as1b中的第一开口118h是存在于由底部起算的导电层114的数量是大于10的环境之下;并且,第一区as1a中的第一开口118h与第二区as1b中的第一开口118h可具有相同的深度。

53.由俯视图的角度观之,第一区as1a的第一开口118h所形成的图案不同于第二区as1b的第一开口118h所形成的图案。详细而言,在一俯视图的一相同的单位面积中,第一区as1a的第一开口118h的面积是大于第二区as1b的第一开口118h的面积。根据本实施例,在一相同的单位面积中,第一区as1a的第一开口118h的数量是大于第二区as1b的第一开口118h的数量,且在俯视图中,第一区as1a的每个第一开口118h的面积是等于第二区as1b的每个第一开口118h的面积。例如,在一相同的单位面积中,第一区as1a的第一开口118h的数量是第二区as1b的第一开口118h的数量的2倍,然本发明并不限于此。在其他实施例中,第一区as1a的第一开口118h的数量可以是第二区as1b的第一开口118h的数量的3倍或大于3倍(在一相同的单位面积中),且在俯视图中,第一区as1a的每个第一开口118h的面积可不同于第二区as1b的每个第一开口118h的面积,例如在俯视图中,第一区as1a的每个第一开口118h的面积可大于第二区as1b的每个第一开口118h的面积。

54.图1b仅示例性绘示8层导电层114,然本发明并不限于此,叠层结构s1可包括大于8层的导电层114,端视需求而调整。在一实施例中,叠层结构s1可包括60层的导电层114。

55.在一些实施例中,衬底110可为硅衬底或其他合适的衬底。绝缘层112可由氧化物所形成,例如是二氧化硅(sio2)。导电层114可由导电材料所形成,此导电材料例如是钨(w)、铝(al)、氮化钛(tin)、氮化钽(tan)、掺杂或未掺杂的多晶硅(poly-silicon)或其他合适的材料。绝缘层112及导电层114可分别通过沉积法所形成。其中,形成绝缘层112的沉积法例如是等离子体辅助化学气相沉积法(plasma enhanced chemical vapor deposition,pecvd),例如是使用反应气体硅烷(sih4)与一氧化二氮(n2o)进行。当利用等离子体辅助化学气相沉积法形成材料为二氧化硅的绝缘层112时,其反应式如下:

56.sih4 2n2o

→

sio2 2n2 2h2(1)

57.在一些实施例中,公式(1)中所产生的气体(例如是氮气及氢气)可能会残留于衬底110中。

58.在一些实施例中,阵列开口116h及第一开口118h可通过刻蚀法所形成,例如是干

刻蚀法。在一些实施例中,衬底110可受到过刻蚀(overetched),使阵列开口116h及第一开口118h的底部低于衬底110的上表面110a。然而,刻蚀步骤可能会与残留于衬底110中的气体反应,产生氨气(nh3)的副产物。氨气(nh3)将不利于后续外延成长层1161及1181(绘示于图2b中)的形成。特别是,相较于第二区as1b而言,第一区as1a中的衬底110可能残留较高浓度的氨气。

59.根据本实施例,由于在一相同的单位面积中,第一区as1a的第一开口118h的面积是大于第二区as1b的第一开口118h的面积,第一区as1a相较于第二区as1b而言具有更多的排放刻蚀气体(例如氨气)的路径(通过第一开口118h),第一区as1a的排放刻蚀气体(例如氨气)的效果优于第二区as1b的排放刻蚀气体的效果,故能够减轻第一区as1a的外延成长层1161(绘示于图2b中)受到刻蚀气体的不良影响。

60.此后,请同时参照图2a及图2b,分别形成存储器串列结构116及虚拟存储器串列结构118于阵列开口116h及第一开口118h中,其中各个存储器串列结构116及各个虚拟存储器串列结构118分别包括一外延成长层1161及1181,外延成长层1161及1181是由衬底110沿着第一方向(例如是z方向)延伸。外延成长层1161及1181例如是硅的外延成长层。接着,在本体部as1的接触结构预定位置120'形成接触结构120。接触结构120设置于阶梯区as的本体部as1中,且位于本体部as1的接触结构120是分别电性连接于对应的导电层114。虚拟部as2的虚拟存储器串列结构118是用于支撑半导体装置100的结构,并没有电性连接于其他装置或元件。

61.根据本发明的一实施例,在俯视图的一相同的单位面积中,第一区as1a的虚拟存储器串列结构118的面积是大于第二区as1b的虚拟存储器串列结构118的面积。并且,在一相同的单位面积中,第一区as1a的虚拟存储器串列结构118的数量可大于第二区as1b的虚拟存储器串列结构118的数量(例如是2倍)。

62.在一些实施例中,存储器串列结构116及虚拟存储器串列结构118包括相同的结构与材料。例如,除了外延成长层1161及1181之外,存储器串列结构116及虚拟存储器串列结构118更包括存储层、通道层及绝缘柱(未绘示)。在一些实施例中,存储器串列结构116与虚拟存储器串列结构118可具有不同的尺寸。

63.在一些实施例中,存储器串列结构116、阵列开口116h、虚拟存储器串列结构118、第一开口118h及接触结构120具有矩形的横截面,然本发明并不限于此,在其他实施例中,存储器串列结构116、阵列开口116h、虚拟存储器串列结构118、第一开口118h及接触结构120的横截面可具有圆形、椭圆形或其他合适的几何形状。

64.在一些实施例中,导电层114中最底部的导电层114(亦即是最邻近于衬底110的导电层114)可作为接地选择线;叠层结构s1的中间部分的导电层114可作为字线;最顶部的导电层114(亦即是最远离于衬底110的导电层114)可作为串列选择线。

65.由于在俯视图的一相同的单位面积中,第一区as1a的虚拟存储器串列结构118的面积是大于第二区as1b的虚拟存储器串列结构118的面积(亦即是第一区as1a的用于形成虚拟存储器串列结构118的第一开口118h的面积大于第二区as1b的用于形成虚拟存储器串列结构118的第一开口118h的面积),在形成包括外延成长层1161及1181的虚拟存储器串列结构116及118的期间,第一区as1a的排放刻蚀气体的效果优于第二区as1b的排放刻蚀气体的效果,能够减轻第一区as1a的外延成长层1181受到刻蚀气体的不良影响。因此,相较于第

一区的虚拟存储器串列结构的面积没有大于第二区的虚拟存储器串列结构的面积的比较例而言,本发明的第一区as1a的虚拟存储器串列结构118的外延成长层1181可具有较好的生长情况,可防止外延成长层1181呈歪斜或者高度不够,借此避免产生短路及漏电流的问题(例如生长不良的外延成长层与接地选择线短路)。

66.在本实施例中,即使是在第一区as1a中,外延成长层1181的高度仍可大于导电层114中最邻近于衬底110的第一层的导电层114的顶面的高度。

67.图3a绘示依照一比较例的半导体装置100p的部分俯视图。图3b绘示图3a的a-a'联机的剖面图。图4a绘示依照本发明一实施例的半导体装置100a的部分俯视图。图4b绘示图4a的a-a'联机的剖面图。本发明的半导体装置100a是类似于半导体装置100,除了半导体装置100a与半导体装置100之间的存储器串列结构116、阵列开口116h、虚拟存储器串列结构118、第一开口118h及接触结构120的横截面的形状有所不同。

68.比较例的半导体装置100p与本发明的半导体装置100a的不同之处在于第一开口118hp(或者是虚拟存储器串列结构118p)在第一区as1a的图案,其他结构系相同或类似。亦即,第一开口118hp(或者是虚拟存储器串列结构118p)在第一区as1a及第二区as1b中具有相同的图案(如图3a所示),第一开口118h(或者是虚拟存储器串列结构118)在第一区as1a及第二区as1b中则具有不同的图案(如图4a所示)。更确切地说,由图3a的俯视图观之,在相同的单位面积ua之下,第一区as1a的第一开口118hp(或者是虚拟存储器串列结构118p)的面积是等于第二区as1b的第一开口118hp(或者是虚拟存储器串列结构118p)的面积。相对地,由图4a的俯视图观之,在相同的单位面积ua之下,第一区as1a的第一开口118h(或者是虚拟存储器串列结构118)的面积是大于第二区as1b的第一开口118h(或者是虚拟存储器串列结构118)的面积。在本实施例中,单位面积ua例如是以接触结构预定位置120'的中心点c1为中心点,朝第二方向(例如是x方向)及第三方向(y方向)延伸至相邻两接触结构预定位置120'之间的中心点c2~c5所围成的一矩形面积。换言之,由图3a的俯视图观之,在相同的单位面积ua之下,第一区as1a的第一开口118hp(或者是虚拟存储器串列结构118p)的面积为2个第一开口118hp(或者是虚拟存储器串列结构118p)的总面积(1/2*4=2);第二区as1b的第一开口118hp(或者是虚拟存储器串列结构118p)的面积亦为2个第一开口118hp(或者是虚拟存储器串列结构118p)的总面积(1/2*4=2)。由图4a的俯视图观之,在相同的单位面积ua之下,第一区as1a的第一开口118h(或者是虚拟存储器串列结构118)的面积为4个第一开口118h(或者是虚拟存储器串列结构118)的总面积;第二区as1b的第一开口118h(或者是虚拟存储器串列结构118)的面积则为2个第一开口118h(或者是虚拟存储器串列结构118)的总面积(1/2*4=2)。在本实施例中,在相同的单位面积ua之下,第一区as1a的第一开口118h的面积为第二区as1b的第一开口118h的面积的2倍,然本发明并不限于此。在本实施例中,每个第一开口118h具有相同的面积,然本发明并不限于此。

69.根据本发明的一些实施例,在相同的单位面积ua之下,第一区as1a的第一开口118h(或者是虚拟存储器串列结构118)的数量大于第二区as1b的第一开口118h(或者是虚拟存储器串列结构118)的数量。举例而言,在半导体装置100p的第一区as1a及第二区as1b中,多个第一开口118hp(或者是虚拟存储器串列结构118p)是沿着第三方向(例如是y方向)排列为一排(例如是一排r1的第一开口118hp(或者是虚拟存储器串列结构118p)),并沿着第二方向(例如是x方向)排列为多排,沿着第三方向(例如是y方向)排列的相邻的2排接触

结构预定位置120'之间设置有沿着第三方向(例如是y方向)排列的1排第一开口118hp(或者是虚拟存储器串列结构118p)。在半导体装置100中,多个第一开口118h(或者是虚拟存储器串列结构118)是沿着第三方向(例如是y方向)排列为一排(例如是一排r2的第一开口118h(或者是虚拟存储器串列结构118)),并沿着第二方向(例如是x方向)排列为多排。在第一区as1a中,沿着第三方向(例如是y方向)排列的相邻的2排接触结构预定位置120'之间设置有沿着第三方向(例如是y方向)排列的2排第一开口118h(或者是虚拟存储器串列结构118)。在第二区as1b中,沿着第三方向(例如是y方向)排列的相邻的2排接触结构预定位置120'之间设置有沿着第三方向(例如是y方向)排列的1排第一开口118h(或者是虚拟存储器串列结构118)。在本实施例中,在相同的单位面积ua之下,第一区as1a的第一开口118h(或者是虚拟存储器串列结构118)的数量为第二区as1b的第一开口118h(或者是虚拟存储器串列结构118)的数量的2倍,然本发明并不限于此。

70.在本实施例中,第一开口118h(或者是虚拟存储器串列结构118)在衬底110上沿着第二方向(例如x方向)设置,第二方向垂直于第一方向。在第二方向中,设置于第一区as1a的第一开口118h(或者是虚拟存储器串列结构118)的中心点ca1是与设置于第二区as1b的第一开口118h(或者是虚拟存储器串列结构118)的中心点cb1对齐。

71.根据本发明的一些实施例,在一俯视图中,当第一开口118h(或者是虚拟存储器串列结构118)的总面积对于阶梯区as的总面积的面积比是等于或大于8%,即可有效释放不利外延成长层成长的气体,使得本发明的第一区as1a中的外延成长层1181仍可具有良好的生长情形。例如,在比较例的半导体装置100p中,由俯视图的角度观之,第一开口118hp(或者是虚拟存储器串列结构118p)的总面积对于阶梯区as1的总面积的面积比是等于5.44%。在本发明一实施例的半导体装置100a中,由俯视图的角度观之,第一开口118h(或者是虚拟存储器串列结构118)的总面积对于阶梯区as的总面积的面积比是等于8.99%。

72.图5绘示依照本发明一实施例的半导体装置100a与比较例的半导体装置100p的虚拟存储器串列结构的外延成长层的形成高度的曲线图。

73.图5是分别对半导体装置100a与半导体装置100p中对应位置的虚拟存储器串列结构的外延成长层进行测量的结果。外延成长层的高度例如是定义为衬底110的上表面110a与外延成长层的顶面之间的垂直高度。x坐标表示虚拟存储器串列结构的编号,其中s1~s9表示本体部as1的第一区as1a的虚拟存储器串列结构的编号,d0~d10表示虚拟部as2的虚拟存储器串列结构的编号。

74.一般而言,当外延成长层的高度等于或大于800埃时,可具备良好的电性效果。由图5的结果可知,半导体装置100p的第一区as1a中,至少编号s5及s1的虚拟存储器串列结构的外延成长层的高度是小于800埃。依照本发明一实施例的半导体装置100a的第一区as1a中,所有的虚拟存储器串列结构118的外延成长层1181的高度皆大于800埃。

75.图6a绘示比较例的半导体装置100p的异常的虚拟存储器串列结构的外延成长层的扫描结果。图6b绘示依照本发明一实施例的半导体装置100a的异常的虚拟存储器串列结构的外延成长层的扫描结果。

76.请同时参照图6a及图6b,若虚拟存储器串列结构的外延成长层的高度是小于200埃则用黑点标记为异常的虚拟存储器串列结构的外延成长层。图6a显示比较例的半导体装置100p中具有一些异常的虚拟存储器串列结构的外延成长层;图6b显示本发明一实施例的

半导体装置100a并不具有异常的虚拟存储器串列结构的外延成长层。

77.由图5~图6b的结果可知,相较于比较例的半导体装置100p而言,由于本发明一实施例的半导体装置100a的第一区as1a的第一开口118h(或虚拟存储器串列结构118)的面积大于第二区as1b的第一开口118h(或虚拟存储器串列结构118)的面积(在相同单位面积ua之下),可较有效地排除衬底110中不利外延成长层生长的气体,即使是第一区as1a的虚拟存储器串列结构118的外延成长层1181亦可具有较好的生长情况,进而避免上述的短路及漏电流的问题。

78.图7绘示依照本发明另一实施例的半导体装置200的部分俯视图。

79.请参照图7,在一相同的单位面积ua中,第一区as1a的第一开口218h(或者是虚拟存储器串列结构218)的面积是大于第二区as1b的第一开口218h(或者是虚拟存储器串列结构218)的面积。半导体装置200是类似于半导体装置100a,其不同之处在于第一区as1a的第一开口218h(或者是虚拟存储器串列结构218)的图案(如图7所示)不同于第一区as1a的第一开口118h(或者是虚拟存储器串列结构118)的图案(如图4a所示)。进一步而言,第一开口218h(或者是虚拟存储器串列结构218)在衬底110上沿着第二方向(例如是x方向)及第三方向(例如是y方向)设置,第一方向、第二方向与第三方向例如是互相垂直。在第二方向中,设置于第一区as1a的第一开口218h(或者是虚拟存储器串列结构218)的中心点ca2是与设置于第二区as1b的第一开口218h(或者是虚拟存储器串列结构218)的中心点cb2错开。

80.在半导体装置100a及200中,第一区as1a的第一开口118h及218h(或者是虚拟存储器串列结构118及218)的中心点ca1及ca2是沿着第二方向互相对齐,然本发明并不以此为限,在其他实施例中,相邻2排的第一区as1a的第一开口118h及218h(或者是虚拟存储器串列结构118及218)的中心点ca1及ca2在第二方向可彼此错开。

81.本发明的第一开口118h及218h(或者是虚拟存储器串列结构118及218)的数量及排列方式可任意调整,只要在一相同的单位面积ua中,第一区as1a的第一开口118h及218h(或者是虚拟存储器串列结构118及218)的面积是大于第二区as1b的第一开口118h及218h(或者是虚拟存储器串列结构118及218)的面积,即为本发明所欲保护的范围。

82.图8a绘示依照本发明又一实施例的半导体装置300的部分俯视图。图8b绘示图8a的a-a'联机的剖面图。

83.请同时参照图8a及图8b,在一相同的单位面积ua中,第一区as1a的第一开口318h(或者是虚拟存储器串列结构318)的面积是大于第二区as1b的第一开口318h(或者是虚拟存储器串列结构318)的面积。半导体装置300是类似于半导体装置100a,其不同之处在于第一区as1a的第一开口318h(或者是虚拟存储器串列结构318)的图案(如图8a所示)不同于第一区as1a的第一开口118h(或者是虚拟存储器串列结构118)的图案(如图4a所示)。进一步而言,第一区as1a的第一开口318h(或者是虚拟存储器串列结构318)的直径d1是大于第二区as1b的第一开口318h(或者是虚拟存储器串列结构318)的直径d2。在一实施例中,第一区as1a的第一开口318h(或者是虚拟存储器串列结构318)的直径d1是比第二区as1b的第一开口318h(或者是虚拟存储器串列结构318)的直径d2多10%以上。例如,当第二区as1b的第一开口318h(或者是虚拟存储器串列结构318)的直径d2是80nm时,第一区as1a的第一开口318h(或者是虚拟存储器串列结构318)的直径d1可以是88nm以上的任意数值,例如90nm或100nm。

84.在一些实施例中,第一开口318h(或者是虚拟存储器串列结构318)在衬底110上沿着第二方向(例如是x方向)及第三方向(例如是y方向)设置,第一方向、第二方向与第三方向可互相垂直。在第二方向中,设置于第一区as1a的第一开口318h(或者是虚拟存储器串列结构318)的中心点ca3是与设置于第二区as1b的第一开口318h(或者是虚拟存储器串列结构318)的中心点cb3对齐。

85.图9a绘示比较例的半导体装置100p的异常的虚拟存储器串列结构的外延成长层的扫描结果。图9b绘示依照本发明一实施例的半导体装置300的异常的虚拟存储器串列结构的外延成长层的扫描结果。图9c绘示依照本发明另一实施例的半导体装置300的异常的虚拟存储器串列结构的外延成长层的扫描结果。

86.在图9a所示的比较例中,第一区as1a的第一开口118hp的直径为80nm。在图9b的半导体装置300的一实施例中,第一区as1a的第一开口318h的直径为90nm。在图9c的半导体装置300的另一实施例中,第一区as1a的第一开口318h的直径为100nm。

87.请同时参照图9a~图9c,若虚拟存储器串列结构的外延成长层的高度是小于200埃则用黑点标记为异常的虚拟存储器串列结构的外延成长层。图9a显示比较例的半导体装置100p中具有一些异常的虚拟存储器串列结构的外延成长层;图9b及图9c显示本发明一些实施例的半导体装置300并不具有异常的虚拟存储器串列结构的外延成长层。

88.图10绘示依照本发明又一实施例的半导体装置400的部分俯视图。

89.请参照图10,在一相同的单位面积ua中,第一区as1a的第一开口418h(或者是虚拟存储器串列结构418)的面积是大于第二区as1b的第一开口418h(或者是虚拟存储器串列结构418)的面积。半导体装置400是类似于半导体装置300,其不同之处在于第一区as1a的第一开口418h(或者是虚拟存储器串列结构418)的图案(如图10所示)不同于第一区as1a的第一开口318h(或者是虚拟存储器串列结构318)的图案(如图8a所示)。进一步而言,第一开口418h(或者是虚拟存储器串列结构418)在衬底110上沿着第二方向(例如是x方向)及第三方向(例如是y方向)设置,第一方向、第二方向与第三方向例如是互相垂直。在第二方向中,设置于第一区as1a的第一开口418h(或者是虚拟存储器串列结构418)的中心点ca4是与设置于第二区as1b的第一开口418h(或者是虚拟存储器串列结构418)的中心点cb4错开。

90.本发明的第一开口318h及418h(或者是虚拟存储器串列结构318及418)的数量及排列方式可任意调整,只要在一相同的单位面积ua中,第一区as1a的第一开口318h及418h(或者是虚拟存储器串列结构318及418)的面积是大于第二区as1b的第一开口318h及418h(或者是虚拟存储器串列结构318及418)的面积,即为本发明所欲保护的范围。

91.根据本发明的一些实施例中,在一相同的单位面积ua中,仅需要增加第一区as1a的第一开口118h(或虚拟存储器串列结构118)的面积(例如是通过增加第一区as1a的第一开口118h的数量或直径)即可达成防止外延成长层呈歪斜或者高度不够的效果,并不需要同时增加第一区as1a及第二区as1b的第一开口118h(或虚拟存储器串列结构118)的面积,故可大幅节省成本。

92.本发明提供一种半导体装置及其制造方法。根据一实施例,半导体装置包括一衬底、设置于衬底上的一叠层结构以及多个虚拟存储器串列结构。叠层结构包括沿着一第一方向交替叠层的多个绝缘层及多个导电层。虚拟存储器串列结构设置于半导体装置的一阶梯区,且沿着第一方向穿过叠层结构,其中阶梯区包括一本体部,且本体部包括相邻的一第

一区及一第二区。在第一区中,虚拟存储器串列结构所对应的导电层的数量是介于1~10;在第二区中,虚拟存储器串列结构所对应的导电层的数量是大于10。在一相同的单位面积中,第一区的虚拟存储器串列结构的面积是大于第二区的虚拟存储器串列结构的面积。

93.相较于第一区的虚拟存储器串列结构的面积没有大于第二区的虚拟存储器串列结构的面积(在一相同的单位面积中)的比较例而言,由于本发明的半导体装置的第一区的虚拟存储器串列结构的面积是大于第二区的虚拟存储器串列结构的面积(在一相同的单位面积中),可更有效地释放不利外延成长层的气体,故本发明的第一区的虚拟存储器串列结构的外延成长层可具有较好的生长情况,可防止外延成长层呈歪斜或者高度不够,借此避免产生如短路及漏电流的电性问题。

94.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。