1.本发明涉及存储器访问技术,尤其是涉及一种存储器系统及其存储器访问接口装置。

背景技术:

2.nand快闪存储器最早期采用低速的单倍数据速率(single data rate;sdr)模式架构。然而,随着产品的带宽需求逐渐增加,传统的单倍数据速率模式架构已经不能满足使用要求,无法达成速度的需求。因此,非挥发性双倍数据速率(non

‑

volatile double data rate;nvddr)模式的架构被提出以突破速度的限制,并在此架构下提出愈来愈高速的规格。

3.然而,市面上的控制器均被要求能够支持所有速度的模式,以及具有信号校正的能力。因此,如何设计一个新的存储器访问接口装置,以解决上述的缺陷,是该领域迫切需要解决的问题。

技术实现要素:

4.鉴于先前技术的问题,本发明的一目的在于提供一种存储器系统及其存储器访问接口装置,以改善先前技术。

5.本发明包括一种存储器访问接口装置,包括:时钟产生电路、一对双倍数据速率访问信号传输电路、数据信号传输电路以及命令与地址信号传输电路。时钟产生电路配置以根据源头时钟信号产生直接传送至存储设备的操作时钟信号,以及一对双倍数据速率(double data rate;ddr)参考时钟信号以及命令与地址参考时钟信号。双倍数据速率访问信号传输电路分别配置为在双倍数据速率模式中,根据该对双倍数据速率参考时钟信号其中之一,调整来自存储器访问控制器的一对双倍数据速率访问信号其中之一的相位以及工作周期,以产生一对输出访问信号其中之一以访问存储设备,其中该对双倍数据速率访问信号包括双倍数据速率数据信号以及数据选通(data strobe)信号,且该对输出访问信号包括输出双倍数据速率数据信号以及输出数据选通信号。数据信号传输电路配置为在单倍数据速率模式中,根据命令与地址参考时钟信号,对来自存储器访问控制器的单倍数据速率数据信号施加最小延迟(minimum latency),以产生输出单倍数据速率数据信号以访问存储设备。命令与地址信号传输电路配置为在双倍数据速率模式或单倍数据速率模式中,根据命令与地址参考时钟信号,对来自存储器访问控制器的命令与地址信号施加可调整延迟(programmable latency),以产生输出命令信号以及输出地址信号以访问存储设备。

6.本发明还包括一种存储器系统,包括:存储器访问控制器、存储设备以及存储器访问接口装置。存储器访问接口装置包括:时钟产生电路、一对双倍数据速率访问信号传输电路、数据信号传输电路以及命令与地址信号传输电路。时钟产生电路配置为根据源头时钟信号产生直接传送至存储设备的操作时钟信号,以及一对双倍数据速率参考时钟信号以及命令与地址参考时钟信号。双倍数据速率访问信号传输电路各配置为在双倍数据速率模式中,根据该对双倍数据速率参考时钟信号其中之一,调整来自存储器访问控制器的一对双

倍数据速率访问信号其中之一的相位以及工作周期,以产生一对输出访问信号其中之一为访问存储设备,其中该对双倍数据速率访问信号包括双倍数据速率数据信号以及数据选通信号,且该对输出访问信号包括输出双倍数据速率数据信号以及输出数据选通信号。数据信号传输电路配置为在单倍数据速率模式中,根据命令与地址参考时钟信号,对来自存储器访问控制器的单倍数据速率数据信号施加最小延迟,以产生输出单倍数据速率数据信号以访问存储设备。命令与地址信号传输电路配置为在双倍数据速率模式或单倍数据速率模式中,根据命令与地址参考时钟信号,对来自存储器访问控制器的命令与地址信号施加可调整延迟,以产生输出命令信号以及输出地址信号以访问存储设备。

7.有关本发明的特征、实作与功效,将如下结合附图针对优选实施例做详细说明。

附图说明

8.图1显示本发明的一实施例中,一种存储器系统的方块图;

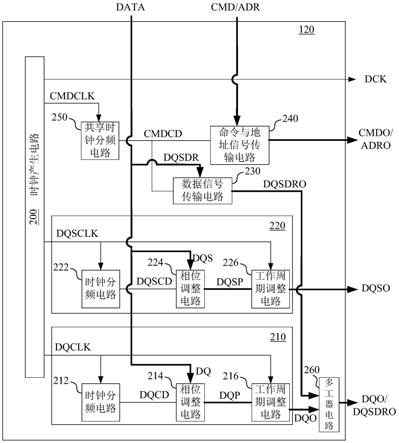

9.图2显示本发明的一实施例中,图1的存储器访问接口装置的详细方块图;以及

10.图3显示本发明一实施例中,图2的时钟产生电路的详细方块图。

具体实施方式

11.本发明的一目的在于提供一种存储器系统及其存储器访问接口装置。

12.请参照图1。图1显示本发明的一实施例中,一种存储器系统100的方块图。存储器系统100包括:存储器访问控制器110、存储器访问接口装置120以及存储设备130。

13.存储器系统100可通过例如、但不限于系统总线(未示出)电耦接于其他模组。举例而言,存储器系统100可通过系统总线电耦接于处理器(未示出),以使处理器得以访问存储器系统100。

14.在一个实施例中,存储器访问接口装置120可为例如,但不限于实体层电路。存储设备130可为单倍数据速率(single data rate;sdr)存储设备或双倍数据速率(double data rate;ddr)存储设备。

15.外部的访问信号,例如来自于处理器的访问信号,可先由存储器访问控制器110所接收并传送至存储器访问接口装置120,再由存储器访问接口装置120传送访问信号至存储设备130中进行访问。

16.更详细地说,在一个实施例中,存储器访问控制器110可接收并传送包括例如、但不限于命令信号cmd、地址信号adr以及数据信号data的访问信号至存储器访问接口装置120。其中,命令信号cmd以及地址信号adr的传送可由一个信号路径进行。数据信号data的传送可由另一信号路径进行。

17.存储器访问接口装置120对命令信号cmd以及地址信号adr施加延迟,以调整时序并产生输出命令信号cmdo以及输出地址信号adro至存储设备130。

18.在存储设备130是单倍数据速率存储设备的情形下,数据信号data仅包括单倍数据速率访问信号,亦即单倍数据速率数据信号dqsdr。存储器访问接口装置120因此运作于单倍数据速率模式中,以施加延迟于单倍数据速率数据信号dqsdr,并产生输出单倍数据速率数据信号dqsdro至存储设备130。

19.在存储设备130是双倍数据速率存储设备的情形下,数据信号data包括一对双倍

数据速率访问信号,包括双倍数据速率数据信号dq以及数据选通信号dqs,以使存储器访问接口装置120运作于双倍数据速率模式中,以调整双倍数据速率数据信号dq以及数据选通信号dqs的相位,并产生输出双倍数据速率数据信号dqo以及输出数据选通信号dqso至存储设备130。

20.输出命令信号cmdo以及输出地址信号adro的传送可由一个信号路径进行。输出双倍数据速率数据信号dqo或是输出单倍数据速率数据信号dqsdro的传送则可由另一信号路径进行。输出数据选通信号dqso的传送可由又一信号路径进行。

21.更进一步地,存储器访问接口装置120更配置为通过再一信号路径产生操作时钟信号dck至存储设备130,以使存储设备130据以运作。

22.存储设备130的内部数据因此可根据上述传送至存储设备130的信号的正确时序进行访问。

23.存储器访问接口装置120实际上包括接收器rx以及传送器tx。传送器tx的结构以及运作方式,将在下面的段落中详细说明。

24.请参照图2。图2显示本发明的一实施例中,图1的存储器访问接口装置120的详细方块图。需注意的是,在图2中,仅示出存储器访问接口装置120的传送器tx的部分,而未示出接收器rx的部分。

25.存储器访问接口装置120包括时钟产生电路200、一对双倍数据速率访问信号传输电路210及220、数据信号传输电路230以及命令与地址信号传输电路240。

26.时钟产生电路200配置为根据源头时钟信号产生直接传送至存储设备的操作时钟信号dck,以及一对双倍数据速率参考时钟信号以及命令与地址参考时钟信号cmdclk。

27.在一个实施例中,该对双倍数据速率参考时钟信号包括数据参考时钟信号dqclk以及数据选通参考时钟信号dqsclk。

28.在双倍数据速率模式中,双倍数据速率访问信号传输电路210及220分别对应处理双倍数据速率数据信号dq以及数据选通信号dqs。

29.双倍数据速率访问信号传输电路210包括时钟分频电路(clock frequency division circuit)212、相位调整电路214以及工作周期调整电路216。

30.时钟分频电路212配置为对数据参考时钟信号dqclk的频率进行分频,以产生分频双倍数据速率参考时钟,亦即分频数据参考时钟信号dqcd。

31.相位调整电路214配置为自存储器访问控制器110接收双倍数据速率数据信号dq,以根据分频数据参考时钟信号dqcd调整双倍数据速率数据信号dq的相位,并产生相位调整访问信号dqp。

32.在一个实施例中,相位调整电路214可包括至少一触发器(flip

‑

flop),根据分频数据参考时钟信号dqcd的相位对双倍数据速率数据信号dq进行取样,达到相位调整的机制。

33.在一个实施例中,当分频数据参考时钟信号dqcd的上升沿(rising edge)位于双倍数据速率数据信号dq的建立与保持时间(set

‑

up and hold time)中,将容易产生时序违反(timing violation)的状况。其中,建立与保持时间是双倍数据速率数据信号dq的波形由低态转往高态的转态时间。

34.因此,在一个实施例中,相位调整电路214可根据分频数据参考时钟信号dqcd的上

升沿以及下降沿(falling edge)的取样结果,调整双倍数据速率数据信号dq的相位。在一个实施例中,当分频数据参考时钟信号dqcd的上升沿并未取样到信号转态,而分频数据参考时钟信号dqcd的下降沿取样到信号转态时,相位调整电路214可根据例如,但不限于分频数据参考时钟信号dqcd的下降沿调整双倍数据速率数据信号dq的相位。

35.需注意的是,上述相位调整电路214的结构仅为一范例。在其他实施例中,相位调整电路214的结构可为不同。

36.工作周期调整电路216配置为根据数据参考时钟信号dqclk调整相位调整访问信号dqp的工作周期,以产生并传送输出访问信号,亦即输出双倍数据速率数据信号dqo至存储设备130。

37.为了能够支持可同时根据上升沿以及下降沿进行数据取样的双倍数据速率模式,工作周期调整电路216可根据由数据参考时钟信号dqclk分频而来的分频数据参考时钟信号dqcd运作,以使具有较高速度的数据参考时钟信号dqclk能被用来微调相位调整访问信号dqp的工作周期,使工作周期成为50

‑

50,即半周期。调整的结果被输出为输出双倍数据速率数据信号dqo。需注意的是在实作上,由于元件造成的误差,工作周期可与完全的半周期之间有合理的差距。

38.在一个实施例中,双倍数据速率访问信号传输电路220可具有相同于双倍数据速率访问信号传输电路210的结构,而包括时钟分频电路222、相位调整电路224以及工作周期调整电路226。

39.时钟分频电路222配置为对数据选通参考时钟信号dqsclk的频率进行分频,以产生分频双倍数据速率参考时钟,亦即分频数据选通参考时钟信号dqscd。相位调整电路224配置为自存储器访问控制器110接收数据选通信号dqs,以根据分频数据选通参考时钟信号dqscd调整数据选通信号dqs的相位,进而产生相位调整访问信号dqsp。更进一步地,工作周期调整电路226配置为根据数据选通参考时钟信号dqsclk调整相位调整访问信号dqsp的工作周期,以产生并传送输出访问信号,亦即输出数据选通信号dqso至存储设备130。

40.在一个实施例中,存储器访问接口装置120更包括共享时钟分频电路250,配置为对命令与地址参考时钟信号cmdclk进行分频,以产生分频命令与地址参考时钟信号cmdc,进而使数据信号传输电路230以及命令与地址信号传输电路240实际上接收到分频命令与地址参考时钟信号cmdcd并据以运作。

41.在单倍数据速率模式中,数据信号传输电路230仅需处理单倍数据速率数据信号dqsdr。因此,不需进行相位的调整或是工作周期的确保。数据信号传输电路230配置为根据分频命令与地址参考时钟信号cmdcd,对来自存储器访问控制器110的单倍数据速率数据信号dqsdr施加最小延迟,以产生输出单倍数据速率数据信号dqsdro至存储设备130。在一个实施例中,最小延迟远小于该对双倍数据速率访问信号传输电路210及220的处理时间。

42.不论在双倍数据速率模式或单倍数据速率模式中,命令与地址信号传输电路240配置为根据分频命令与地址参考时钟信号cmdcd,对来自存储器访问控制器110的命令信号cmd以及地址信号adr施加可调整延迟,以产生输出命令信号cmdo以及输出地址信号adro至存储设备130。

43.根据以上所述,不论存储设备130是双倍数据速率存储设备或单倍数据速率存储设备,存储器访问接口装置120均可访问存储设备130。

44.当存储设备130是双倍数据速率存储设备时,存储器访问接口装置120运作于双倍数据速率模式。该对双倍数据速率访问信号传输电路210及220对双倍数据速率数据信号dq以及数据选通信号dqs进行处理,以产生输出双倍数据速率数据信号dqo以及输出数据选通信号dqso。

45.命令与地址信号传输电路240对命令信号cmd以及地址信号adr施加与该对双倍数据速率访问信号传输电路210及220的处理时间相符的可调整延迟。存储设备130可根据命令信号cmd以及地址信号adr被访问,以将与输出双倍数据速率数据信号dqo以及输出数据选通信号dqso相关的数据写入至存储设备130。

46.当存储设备130为单倍数据速率存储设备时,存储器访问接口装置120运作于单倍数据速率模式。数据信号传输电路230对单倍数据速率数据信号dqsdr施加最小延迟,以产生输出单倍数据速率数据信号dqsdro。

47.命令与地址信号传输电路240对命令信号cmd以及地址信号adr施加与数据信号传输电路230的最小延迟相符的可调整延迟。存储设备130可根据命令信号cmd以及地址信号adr被访问,以将与输出单倍数据速率数据信号dqsdro相关的数据写入至存储设备130。

48.在一个实施例中,存储器访问接口装置120更包括多工器电路260,配置为在双倍数据速率模式中,选择输出双倍数据速率数据信号dqo以传送至存储设备130,并在单倍数据速率模式中,选择输出单倍数据速率数据信号dqsdro以传送至存储设备130。

49.请参照图3。图3显示本发明一实施例中,图2的时钟产生电路200的详细方块图。

50.时钟产生电路200包括源头时钟电路300、使能信号产生电路310以及时钟相位调整电路320、330、340以及350。

51.在一个实施例中,源头时钟电路300为例如,但不限于振荡器,并配置为产生源头时钟信号clk。使能信号产生电路310配置为产生使能信号en。

52.在一个实施例中,时钟相位调整电路320~350包括运作时钟相位调整电路320、命令与地址时钟相位调整电路330、数据时钟相位调整电路340以及数据选通时钟相位调整电路350。

53.以运作时钟相位调整电路320为例,运作时钟相位调整电路320包括源头相位调整电路322、使能同步电路324以及突波去除电路326。

54.源头相位调整电路322配置为接收源头时钟信号clk,并调整源头时钟信号clk的相位,以产生相位调整时钟信号,例如相位调整操作时钟信号pdclk。在一个实施例中,相位调整操作时钟信号pdclk是由源头时钟信号clk延迟90的的相位产生。

55.使能同步电路324配置为接收相位调整操作时钟信号pdclk以及使能信号en,以根据相位调整操作时钟信号pdclk调整使能信号en,进而产生相位调整使能信号,例如相位调整操作使能信号den,其与相位调整操作时钟信号pdclk具有相同的相位。

56.突波去除电路326配置为接收相位调整操作使能信号den以及相位调整操作时钟信号pdclk,以由相位调整操作使能信号den使能以输出相位调整时钟信号pdclk。

57.在一个实施例中,命令与地址时钟相位调整电路330、数据时钟相位调整电路340以及数据选通时钟相位调整电路350具有与运作时钟相位调整电路320相同的元件。

58.在一个实施例中,时钟产生电路200更包括源头时钟分频电路360,配置为对来自运作时钟相位调整电路320的相位调整时钟信号pdclk的频率进行分频,以产生操作时钟信

号dck。

59.对于命令与地址时钟相位调整电路330、数据时钟相位调整电路340以及数据选通时钟相位调整电路350来说,由其产生的相位调整时钟信号分别对应于命令与地址参考时钟信号cmdclk、数据参考时钟信号dqclk以及数据选通参考时钟信号dqsclk。由于这些电路可经由与运作时钟相位调整电路320相同的方式产生各自的时钟信号,因此不再详述。

60.藉由图3的结构,时钟产生电路200可产生双倍数据速率访问信号传输电路210及220、数据信号传输电路230以及命令与地址信号传输电路240所需的参考时钟信号,且各参考时钟信号具有可调整的相位。因此,存储器访问接口装置120可提供精准的信号校正机制。

61.在一个实施例中,信号校正可与存储器访问控制器110共同进行,由存储器访问控制器110传送访问信号,通过存储器访问接口装置120访问存储设备130的内容,并将访问结果与存储设备130主动提供的内容进行比较。比较结果可用以控制时钟产生电路200的相位调整机制,达到信号校正的机制。

62.需注意的是,各时钟相位调整电路320~350的突波去除电路,例如时钟相位调整电路320中的突波去除电路326,是在相位调整操作时钟信号pdclk的任一偶数周期波形时,根据相位调整操作使能信号den使能。这样的方式,可避免突波去除电路326所输出的信号与源头相位调整电路322产生的源头相位调整电路322成为反相的状况。

63.因此,存储器访问接口装置120可在双倍数据速率模式提供独立、相位可调,且具有大频率范围的时钟信号,并确保输出的访问信号的工作周期为半周期,达到精确调整访问信号的相位,以访问存储设备130的功效。

64.更进一步地,存储器访问接口装置120可在单倍数据速率模式提供具有较低速的参考时钟信号,使数据信号、命令信号以及地址信号的处理具有最小延迟。

65.需注意的是,上述的实施方式仅为一范例。在其他实施例中,本领域具有普通知识的技术人员当可在不违背本发明的精神下进行更改。

66.虽然本发明的实施例如上所述,然而该些实施例并非用来限定本发明,本技术领域具有普通知识的技术人员可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均属于本发明所寻求的专利保护范畴,换言之,本发明的专利保护范围须根据本发明的权利要求书所界定为准。

67.附图标记说明:

68.100:存储器系统

69.110:存储器访问控制器

70.120:存储器访问接口装置

71.130:存储设备

72.200:时钟产生电路

73.210:双倍数据速率访问信号传输电路

74.212:时钟分频电路

75.214:相位调整电路

76.216:工作周期调整电路

77.220:双倍数据速率访问信号传输电路

78.222:时钟分频电路

79.224:相位调整电路

80.226:工作周期调整电路

81.230:数据信号传输电路

82.240:命令与地址信号传输电路

83.250:共享时钟分频电路

84.260:多工器电路

85.300:源头时钟电路

86.310:使能信号产生电路

87.320:运作时钟相位调整电路

88.322:源头相位调整电路

89.324:使能同步电路

90.326:突波去除电路

91.330:命令与地址时钟相位调整电路

92.340:数据时钟相位调整电路

93.350:数据选通时钟相位调整电路

94.360:源头时钟分频电路

95.adr:地址信号

96.adro:输出地址信号

97.clk:源头时钟信号

98.cmd:命令信号

99.cmdcd:分频命令与地址参考时钟信号

100.cmdclk:命令与地址参考时钟信号

101.cmdo:输出命令信号

102.data:数据信号

103.dck:操作时钟信号

104.den:相位调整操作使能信号

105.dq:双倍数据速率数据信号

106.dqcd:分频数据参考时钟信号

107.dqclk:数据参考时钟信号

108.dqo:输出双倍数据速率数据信号

109.dqp:相位调整访问信号

110.dqs:数据选通信号

111.dqscd:分频数据选通参考时钟信号

112.dqsclk:数据选通参考时钟信号

113.dqso:输出数据选通信号

114.dqsp:相位调整访问信号

115.dqsdr:单倍数据速率数据信号

116.dqsdro:输出单倍数据速率数据信号

117.en:使能信号

118.pdclk:相位调整操作时钟信号

119.rx:接收器

120.tx:传送器

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。