1.本公开涉及一种半导体装置封装和其制造方法,且涉及一种包含导电元件的半导体装置封装和其制造方法。

背景技术:

2.在至少部分地由针对经增强处理速度和较小大小的需求的驱动下,半导体装置已变得越来越复杂。经增强处理速度往往涉及更高的时钟速度,这可涉及信号电平之间更频繁的转换,继而可引起较高频率或较短波长下的较高电平的电磁发射。电磁发射可从源半导体装置中辐射,且可入射到相邻半导体装置上。如果相邻半导体装置处的电磁发射的电平足够高,则这些发射可能会不利地影响相邻半导体装置的操作。此现象有时称作电磁干扰(emi)。大小较小的半导体装置可能因在整个电子系统内提供较高密度的半导体装置而使emi加重,且因此加重相邻半导体装置处较高电平的不合需要的电磁发射。因此,期望在两个电子组件之间提供emi屏蔽。

技术实现要素:

3.在本公开的一或多个实施例中,一种半导体装置封装包含衬底、导电元件和导电层。所述衬底具有第一表面、与所述第一表面相对的第二表面以及在所述第一表面与所述第二表面之间延伸的侧面。所述导电元件安置在所述衬底的所述第一表面上。所述导电层具有处于所述导电元件上的第一部分和处于所述衬底的所述侧面上的第二部分。所述导电层的所述第一部分的层数目与所述导电层的所述第二部分的层数目不同。

4.在本公开的一或多个实施例中,一种半导体装置封装包含衬底、导电元件和导电层。所述衬底具有第一表面、与所述第一表面相对的第二表面以及在所述第一表面与所述第二表面之间延伸的侧面。所述导电元件安置在所述衬底的所述第一表面上。所述导电层安置在所述导电元件和所述衬底的所述侧面上。所述导电层包含抗氧化保护层,所述抗氧化保护层安置在所述导电元件上且与所述衬底的所述侧面间隔开。所述衬底的所述第二表面与所述导电层之间的电阻处于从约0.008欧姆到约0.08欧姆的范围。

5.在本公开的一或多个实施例中,一种制造半导体装置封装的方法包含:(a)在衬底的第一表面上形成导电元件;(b)形成与所述导电元件的顶面接触的抗氧化保护层;(c)在与所述衬底的所述第一表面相对的所述衬底的第二表面上形成第一电子组件;以及(d)在所述抗氧化保护层上形成导电层。

附图说明

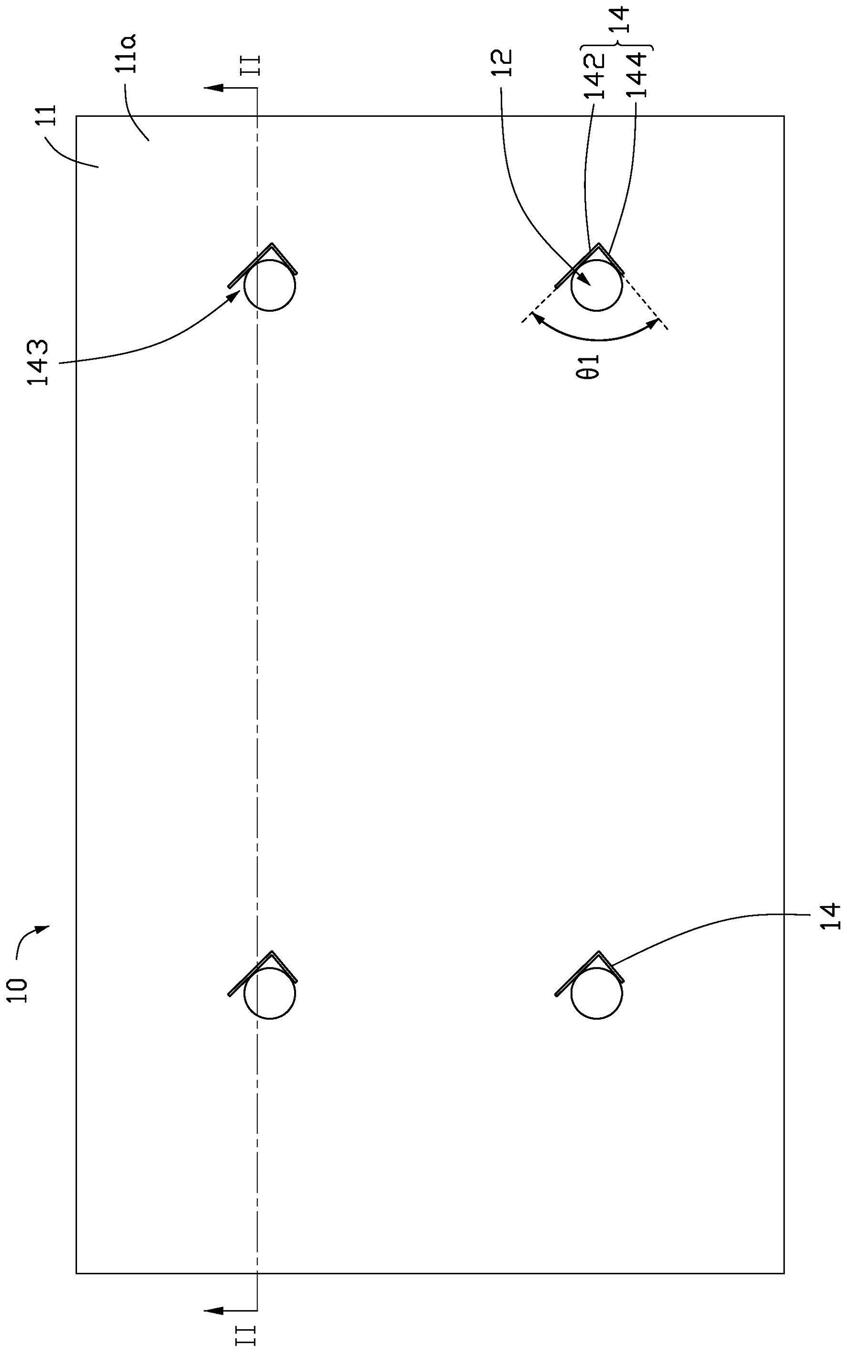

6.图1a说明根据本公开的一些实施例的半导体装置封装的横截面图。

7.图1b说明根据本公开的一些实施例的如图1a中所展示的半导体装置封装的一部分的放大视图。

8.图2说明根据本公开的一些实施例的半导体装置封装的横截面图。

9.图3a、图3a'、图3a

″

、图3a

″′

、图3b、图3c、图3d、图3e、图3f和图3g说明根据本公开的一些实施例的半导体制造方法。

10.图4a、图4a

′

和图4b说明根据本公开的一些实施例的半导体制造方法。

11.在整个图式和具体实施方式中使用共同参考标号来指示相同或类似组件。根据以下结合附图作出的详细描述将容易理解本公开。

具体实施方式

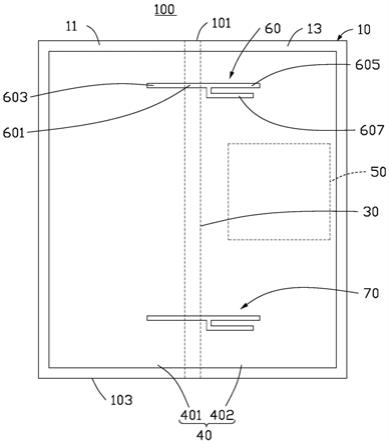

12.图1a说明根据本公开的一些实施例的半导体装置封装1的横截面图。半导体装置封装1包含衬底10、电子组件11a、11b、11c、封装体12、13、导电元件14(或屏蔽元件)、盖15和电触点16。

13.衬底10可例如为印刷电路板,例如基于纸的铜箔层合物、复合铜箔层合物,或聚合物浸渍的基于玻璃纤维的铜箔层合物。衬底10可包含互连结构10r,例如重新分布层 (rdl)和/或接地元件。衬底10可具有表面101、与表面101相对的表面102以及在表面 101与表面102之间延伸的侧面103。

14.衬底10可包含一或多个导电衬垫10c1,其接近、邻近或嵌入并暴露在衬底10的表面101处。衬底10可包含在衬底10的表面101上的阻焊剂10p1(或焊接掩模或钝化层),以完全暴露或暴露导电衬垫10c1的至少一部分以用于电连接。举例来说,阻焊剂10p1 可覆盖导电衬垫10c1的一部分。衬底10可包含一或多个导电衬垫10c2,其接近、邻近或嵌入并暴露在衬底10的表面102处。衬底10可包含在衬底10的表面102上的阻焊剂10p2(或焊接掩模或钝化层),以完全暴露或暴露导电衬垫10c2的至少一部分以用于电连接。举例来说,阻焊剂10p2可覆盖导电衬垫10c2的一部分。

15.电子组件11a和11b安置在衬底10的表面101上。电子组件11a和11b可为主动组件或被动组件,或其组合。主动电子组件可以是例如集成芯片(ic)或裸片。被动电子组件可以是例如电容器、电阻器或电感器。电子组件11a和11b可通过倒装芯片或导线接合技术电连接到衬底10(例如,电连接到导电衬垫10c1)。

16.导电元件14安置在衬底10的表面101上。导电元件14安置在电子组件11a与电子组件11b之间。举例来说,电子组件11a和电子组件11b通过导电元件14彼此分离。在一些实施例中,导电元件14是分隔屏蔽件(compartment shield)。在一些实施例中,导电元件14可包含屏蔽壁。在一些实施例中,导电元件14可包含彼此分离的多个导电柱或导线。举例来说,两个邻近导电柱(或导线)之间存在间隙或距离。与屏蔽壁的使用相比,这可降低制造导电元件14的成本。

17.在一些实施例中,导电元件14可通过安置在衬底10上或构成其部分的导电衬垫或通过盖15连接到接地。导电元件14可包含例如铝(al)、铜(cu)、铬(cr)、锡(sn)、金(au)、银(ag)、镍(ni)、不锈钢、另一金属、其混合物或合金,或它们的其它组合。

18.封装体12安置在衬底10的表面101上以覆盖或包封电子组件11a、11b。封装体12 可进一步覆盖或包封导电元件14的至少一部分。举例来说,封装体12可覆盖导电元件 14的侧面且暴露导电元件14的顶面(或上部部分)。在一些实施例中,封装体12包含具有填料的环氧树脂、模制原料(例如,环氧模制原料或其它模制原料)、聚酰亚胺、酚类化合物或材料、在其中分散有硅酮的材料,或其组合。

19.电子组件11c安置在衬底10的表面102上。电子组件11c可为主动组件或被动组件,或其组合。主动电子组件可以是例如集成芯片(ic)或裸片。被动电子组件可以是例如电容器、电阻器或电感器。电子组件11c可通过倒装芯片或导线接合技术电连接到衬底10 (例如,电连接到导电衬垫10c2)。

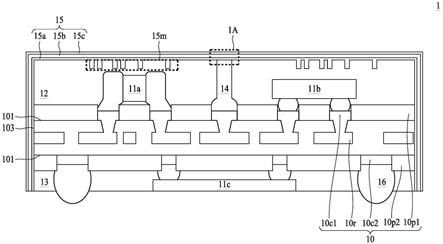

20.在一些实施例中,在操作中,电子组件11c可产生大量的热。举例来说,电子组件11c可以是或包含热源。在一些实施例中,使电子组件11c的背侧表面从封装体13暴露可促进电子组件11c的热耗散。在一些实施例中,半导体装置封装1可通过电触点16 电连接到印刷电路板(例如,主板),且热界面材料(tim)可连接在电子组件11c的背侧表面与印刷电路板之间以提供用于电子组件11c的热耗散路径。

21.电触点16(例如焊球)安置在衬底10的表面102上。电触点16电连接到衬底10的导电衬垫10c2以提供半导体装置封装1与外部组件(例如外部电路或电路板)之间的电连接。在一些实施例中,电触点16可包含可控塌陷芯片连接(c4)凸块、球栅阵列(bga) 或焊盘网格阵列(lga)。

22.封装体13安置在衬底10的表面102上以覆盖或包封电子组件11c。封装体13可进一步覆盖或包封电触点16的至少一部分且暴露电触点16的其它部分以用于电连接。在一些实施例中,电子组件11c的背侧表面可从封装体13暴露。在其它实施例中,电子组件11c的背侧表面可被封装体13覆盖。在一些实施例中,封装体13包含具有填料的环氧树脂、模制原料(例如,环氧模制原料或其它模制原料)、聚酰亚胺、酚类化合物或材料、在其中分散有硅酮的材料,或其组合。

23.盖15安置在封装体12的外部表面上且覆盖电子组件11a、11b、封装体12和导电元件14。盖15可进一步沿着衬底10的侧面103和封装体13的侧面延伸。在一些实施例中,盖15接触从封装体12暴露的导电元件14的顶面。在一些实施例中,盖15是共形屏蔽件(例如,与封装体12的至少一部分(例如封装体12的顶面)共形)。在一些实施例中,盖15可接触从衬底10的侧面103暴露的接地元件。在一些实施例中,盖15通过导电元件14连接到接地。

24.盖15可包含一或多个导电层(或导电薄膜)。举例来说,如图1a中所展示,盖15 包含多个导电层15a、15b、15c。导电层15b安置在导电层15a与导电层15c之间。举例来说,导电层15b被导电层15a和导电层15c包夹。在一些实施例中,导电层15a和 15c可包含不锈钢。在一些实施例中,导电层15b可包含al、cu、cr、sn、au、ag、 ni、其混合物或合金,或上述物的其它组合。在一些实施例中,导电层15a可进一步在封装体12内延伸以限定标记15m。在其它实施例中,可省略标记15m。在一些实施例中,导电层15a可以是或包含晶种层或粘合剂层。在一些实施例中,导电层15c可以是或包含保护层。

25.单独地或一起,导电元件14和盖15可降低电磁发射(例如,emi或串扰)的影响。举例来说,导电元件14和盖15可阻止(至少部分地)在导电元件14和盖15外部产生的电磁发射被电子组件11a、11b接收,阻止(至少部分地)从半导体装置封装1内发出的电磁发射离开半导体装置封装1,和/或阻止(至少部分地)在电子组件11a与11b之间传输的电磁发射。

26.在一些实施例中,半导体装置封装1可通过包含以下操作的操作形成:(i)在衬底10 的表面101上形成元件(例如,电子组件11a、11b、导电元件14和封装体12);(ii)在衬底10的表面102上形成元件(例如,电子组件11c、封装体13和电触点16);以及(iii) 在封装体12、13和衬底10的外表面上形成盖15以接触导电元件14的顶面。

27.然而,由于盖15在形成衬底10的表面102上的元件之后形成,因此导电元件14 的顶面将在空气中暴露一会儿(例如,至少在衬底10的表面102上的元件的形成与盖15 的形成之间的时间段期间)。因此,如在说明由图1中展示的点线方形1a包围的半导体装置封装1的一部分的放大视图的图1b中所展示,金属氧化物层15o(例如,agox、 cuox等)形成于导电元件14的顶面上或邻近所述顶面形成。这将增大导电元件14与盖 15之间的电阻,且不利地影响导电元件14与盖15的屏蔽性能。另外,许多空隙14v也可形成于导电元件14和/或金属氧化物层15o内。这将减小导电元件14和盖15的结构强度,且不利地影响半导体装置封装1的电气性能。

28.在一些实施例中,为了防止导电元件14的顶面的氧化,导电元件14可由au形成。然而,这将增大制造导电元件14的成本。在一些实施例中,可通过应用等离子体(例如,电感耦合等离子体、icp)、蚀刻、研磨或抛光来移除或减少金属氧化物层15o。然而,这将增加制造成本和时间,且将面临工艺可行性问题。在一些实施例中,可在衬底10 的表面102上形成元件之前将胶带或胶粘剂附接到导电元件14的顶面以防止导电元件 14的顶面氧化。然而,当必须移除胶带或胶粘剂以形成盖15时,一些胶带或胶粘剂可能保持在导电元件14的顶面上(即,胶粘剂残余问题),这将妨碍导电元件14与盖15之间的连接。

29.图2说明根据本公开的一些实施例的半导体装置封装2的横截面图。半导体装置封装2类似于图1中展示的半导体装置封装1,且下文描述所述半导体装置封装之间的一些差异。

30.半导体装置封装2进一步包含保护层25。保护层25安置在封装体12上。保护层 25安置在盖15与封装体12之间。保护层25安置在盖15的导电层15a与封装体12之间。保护层25与封装体12的顶面接触。保护层25与导电元件14的顶面接触。保护层 25与盖15的导电层15a接触。在一些实施例中,保护层25具有等于或大于0.1微米的厚度。举例来说,保护层25可包含0.3微米的厚度。

31.在其它实施例中,保护层25可仅安置在导电元件14的顶面上。举例来说,保护层 25不安置在封装体12的顶面上。举例来说,保护层25与封装体12间隔开。举例来说,保护层25与封装体12隔离。在此实施例中,盖15的导电层15a可与封装体12的顶面接触。

32.在一些实施例中,保护层25安置在封装体12上,而不沿着封装体12的侧面、衬底10的侧面103和封装体13的侧面延伸。举例来说,保护层25可包含与封装体12的侧面大体上共面的侧面。举例来说,导电层15a可与保护层25的顶面和侧面接触。

33.在一些实施例中,保护层25可以是或包含抗氧化保护层以防止导电元件14的顶面在制造过程期间被氧化(下文将描述用于制造半导体装置封装2的详细操作)。在一些实施例中,保护层25和盖15的导电层15a可包含相同材料。举例来说,保护层25可以是包含不锈钢的导电层。在其它实施例中,保护层25和盖15的导电层15a可包含不同材料。在一些实施例中,保护层25和盖15的导电层15a可在制造过程期间在不同操作或步骤处形成。因此,即使保护层25和盖15的导电层15a可包含相同材料,保护层25 与导电层15a之间也会存在边界或界面。

34.在一些实施例中,保护层25可用作盖15以提供屏蔽性能。举例来说,保护层25 可被视为盖15的一部分。在一些实施例中,如图2中所展示,封装体12的顶面上的盖 15的一部分的导电层数目与封装体12的侧面、衬底10的侧面103和封装体13的侧面上的盖15的其它

部分的导电层数目不同。举例来说,盖15包含封装体12的顶面(和导电元件14的顶面)上的四个导电层(即,导电层15a、15b、15c和保护层25),以及封装体12的侧面、衬底10的侧面103和封装体13的侧面上的三个导电层(即,导电层15a、 15b、15c)。举例来说,在封装体12(和导电元件14)的顶面上存在四个导电层(即,导电层15a、15b、15c和保护层25)。举例来说,在封装体12的侧面、衬底10的侧面103 和封装体13的侧面上存在三个导电层(即,导电层15a、15b、15c)。

35.在一些实施例中,如图2中所展示,导电层15a可进一步穿入保护层25且在封装体12内延伸以限定标记25m。举例来说,朝向封装体12延伸的导电层15的一部分可被保护层25和封装体12覆盖。在其它实施例中,可省略标记25m。

36.根据图2中所展示的实施例,通过形成保护层25以覆盖导电元件14的顶面(以及封装体12的顶面),可消除或减少导电元件14的顶面上的金属氧化物层。在一些实施例中,与图1a中展示的导电元件14相比,图2中所展示的导电元件14的金属氧化物层的厚度可减少至少90%。举例来说,图2中所展示的导电元件14的金属氧化物层具有比图 1a中所展示的导电元件14的金属氧化物层15o的厚度小至少90%的厚度。

37.在一些实施例中,图2中所展示的盖15与导电元件14之间的电阻小于图1a中所展示的盖15与导电元件14之间的电阻。举例来说,图2中所展示的盖15与衬底10的导电衬垫10c2之间的电阻比图1a中所展示的盖15与衬底10的导电衬垫10c2之间的电阻小约44%到约77%。在一些实施例中,图2中所展示的盖15与衬底10的导电衬垫 10c2之间的电阻处于从约0.008欧姆到约0.08欧姆的范围。举例来说,图2中所展示的盖15与衬底10的导电衬垫10c2之间的电阻处于从约0.021欧姆到约0.08欧姆的范围。举例来说,图2中所展示的盖15与衬底10的导电衬垫10c2之间的电阻处于从约0.044 欧姆到约0.08欧姆的范围。举例来说,图2中所展示的盖15与衬底10的导电衬垫10c2 之间的电阻处于从约0.068欧姆到约0.08欧姆的范围。

38.与图1a中所展示的半导体装置封装1相比,半导体装置封装2的导电元件14的金属氧化物层可显著减少或甚至消除,且盖15与导电元件14之间的电阻也可减小。这将增强导电元件14和盖15的屏蔽性能。另外,还可消除或减小空隙的问题,这将增强导电元件14和盖15的结构强度以及半导体装置封装2的电气性能。

39.图3a、图3a'、图3a”、图3a”'、图3b、图3c、图3d、图3e、图3f和图3g说明根据本公开的一些实施例的半导体制造方法。在一些实施例中,图3a、图3a'、图3a”、图3a”'、图3b、图3c、图3d、图3e、图3f和图3g中的方法可用以制造图2中的半导体装置封装2。

40.参考图3a,提供衬底10。为清楚起见,图3a仅说明衬底单元(例如,单个衬底)。然而,衬底10可呈晶片类型、板类型或条带类型。电子组件11a和11b被安置在衬底 10的表面101上。电子组件11a和11b可通过例如表面安装技术(smt)或任何其它合适的操作置于衬底10的表面101上。电子组件11a和11b可通过例如倒装芯片、导线接合或任何其它合适的技术电连接到衬底10的表面101上的导电衬垫10c1。

41.导电元件14形成于衬底10的表面101上且形成于电子组件11a与电子组件11b之间。在一些实施例中,导电元件14可包含屏蔽壁。在一些实施例中,导电元件14可包含彼此分离的多个导电柱/引脚/立柱/支柱、导电壁或导线。在一些实施例中,导电元件 14可通过导线接合、溅镀或任何其它合适的技术形成。

42.在一些实施例中,如图3a'中所展示,导电元件14可由一或多个导线30w(例如,接合线)形成或包含一或多个导线,每个导线包含连接到衬底10的导电衬垫10c1的第一端子和作为自由端的第二端子。

43.在一些实施例中,如图3a”中所展示,导电元件14可由一或多个环线30w'形成或包含一或多个环线,每个环线包含连接到衬底10的导电衬垫10c1的一部分的第一端子和连接到衬底10的导电衬垫10c1的另一部分(或另一导电衬垫)的第二端子。每个环线 30w'可进一步包含将第一端子连接到第二端子的环部分。所述环部分与衬底10间隔开。

44.在一些实施例中,如图3a”'中所展示,环线30w'可布置成两个或更多个行。在一些实施例中,位于第一行的环线30w'和位于第二行的环线30w'可至少部分重叠。

45.参考图3b,封装体12形成于衬底10的表面101上以覆盖电子组件11a、11b和导电元件14。在一些实施例中,封装体12可完全覆盖电子组件11a、11b和导电元件14。在一些实施例中,封装体12可通过例如压缩模制、转移模制或任何其它合适的模制操作形成。

46.参考图3c,移除封装体12的一部分以暴露导电元件14的顶面。在一些实施例中,通过例如研磨或任何其它合适的操作来移除封装体12的所述部分。在一些实施例中,也可移除导电元件14的一部分。举例来说,将移除图3a”和3a”'所展示的每个环线30w' 的顶部部分以将每个环线30w'分成两个单独的线。

47.接着,在封装体12的顶面和导电元件14的顶面上形成保护层25。保护层25接触封装体12的顶面和导电元件14的顶面。在一些实施例中,保护层25可以是或包含抗氧化保护层以防止导电元件14的顶面在后续操作期间被氧化。在一些实施例中,保护层25可以是或包含不锈钢。在一些实施例中,保护层25可通过例如溅镀或任何其它合适的操作形成。

48.在一些实施例中,在用于移除封装体12的部分的研磨操作之后,封装体12的剩余顶面可具有相对较高的粗糙度(例如,约1.7微米)。因此,为确保保护层25可完全且均匀覆盖封装体12的顶面,保护层25可具有等于或大于0.1微米的厚度。

49.参考图3d,电子组件11c安置在衬底10的表面102上。可通过例如smt或任何其它合适的操作将电子组件11c置于衬底10的表面102上。电子组件11c可通过例如倒装芯片、导线接合或任何其它合适的技术电连接到衬底10的表面102上的导电衬垫 10c2。电触点16形成于衬底10的表面102上,且电连接到衬底10的表面102上的导电衬垫10c2。

50.参考图3e,封装体13形成于衬底10的表面102上以覆盖电子组件11c和电触点 16。在一些实施例中,封装体13可完全覆盖电子组件11c和电触点16。在一些实施例中,封装体13可通过例如压缩模制、转移模制或任何其它合适的模制操作形成。

51.参考图3f,移除封装体13的一部分以暴露电触点16的一部分以用于电连接。在一些实施例中,通过例如研磨或任何其它合适的操作来移除封装体13的所述部分。在一些实施例中,电子组件11c的背侧表面可从封装体13暴露。在一些实施例中,可执行回焊操作(或锡球重植(reballing)操作)以使电触点16从封装体13突出,如图3f中所展示。

52.接着,形成一或多个凹部12r以穿入保护层25和封装体12的一部分。凹部12可限定如图2中所展示的标记25m。在一些实施例中,凹部12r可通过例如激光、钻孔、蚀刻或其它合适的技术形成。

53.参考图3g,可执行单切以分离出个别半导体封装装置。即,贯穿封装体12、包含衬底10和封装体13的衬底条执行单切。可例如通过使用划片机、激光或其它适当的切割技术

执行单切。

54.接着,在保护层25、封装体12、衬底10和封装体13的外表面上形成盖15以形成如图2中所展示的半导体装置封装2。在一些实施例中,导电层15a形成于保护层25上和凹部12r内。导电层15a进一步形成于封装体12、衬底10和封装体13的侧面上。导电层15b形成于导电层15a上。导电层15c形成于导电层15b上。在一些实施例中,导电层15a和15c可包含不锈钢。在一些实施例中,导电层15b可包含al、cu、cr、sn、 au、ag、ni、其混合物或合金,或上述物的其它组合。在一些实施例中,导电层15a、 15b和15c可通过例如涂布、溅镀、电镀、打印或任何其它合适的操作形成。

55.根据图3a、3a'、3a”、3a”'、3b、3c、3d、3e、3f和3g中展示的实施例,在导电元件14的顶面从封装体12暴露之后形成保护层25以覆盖导电元件14的顶面(和封装体12的顶面)可防止导电元件14的顶面在用于在衬底10的表面102上形成元件的操作期间被氧化。这可促进导电元件14与盖15之间的连接且减小盖15与导电元件14之间的电阻,从而增强导电元件14和盖15的屏蔽性能。

56.图4a、4a'和4b说明根据本公开的一些实施例的半导体制造方法。在一些实施例中,图4a、4a'和4b中的操作类似于图3a、图3a'、图3a”、图3a”'、图3b、图3c、图3d、图3e、图3f和图3g中所展示的操作,且下文描述操作之间的一些差异。

57.参考图4a和图4a',在安置衬底10的电子组件11a和11b之后,环线40w经形成以跨越电子组件11b。举例来说,环线40w的一个端子连接到邻近电子组件11b的一侧的导电衬垫,且环线40w的另一端子连接到邻近电子组件11b的相对侧的另一导电衬垫。环线40w可进一步包含跨电子组件11b且连接环线40w的两个端子的环部分。

58.在类似于图3b、3c、3d、3e、3f和3g中展示的操作的操作之后,形成如图4b 中展示的半导体装置封装4。在一些实施例中,在如图3c中所展示的移除封装体12的一部分的操作之后,环线40w可分成如图4b中所展示的两个部分40w1和40w2,每个部分具有从封装体12暴露且与保护层25接触的顶部端子。举例来说,可完全移除环线 40w的顶部部分以将环线40分成两个单独的部分40w1和40w2。在其它实施例中,移除环线40w的顶部部分的仅一部分以从封装体12暴露,而不将环线40w切割成两个单独的部分40w1和40w2。

59.如本文所使用,术语“大约”、“大体上”、“大体”和“约”用以描述和说明小的变化。当与事件或情形结合使用时,所述术语可指事件或情形准确发生的例子以及事件或情形极近似地发生的例子。举例来说,当结合数值使用时,所述术语可指小于或等于所述数值的

±

10%的变化范围,例如,小于或等于

±

5%、小于或等于

±

4%、小于或等于

±

3%、小于或等于

±

2%、小于或等于

±

1%、小于或等于

±

0.5%、小于或等于

±

0.1%,或小于或等于

±

0.05%。举例来说,如果两个数值之间的差值小于或等于所述值的平均值的

±

10%(例如,小于或等于

±

5%、小于或等于

±

4%、小于或等于

±

3%、小于或等于

±

2%、小于或等于

±

1%、小于或等于

±

0.5%、小于或等于

±

0.1%,或小于或等于

±

0.05%),那么可认为所述两个数值“大体上”相同。举例来说,“大体上”平行可指相对于0

°

小于或等于

±

10

°

的角变化范围,例如,小于或等于

±5°

、小于或等于

±4°

、小于或等于

±3°

、小于或等于

±2°

、小于或等于

±1°

、小于或等于

±

0.5

°

、小于或等于

±

0.1

°

,或小于或等于

±

0.05

°

。举例来说,“大体上”垂直可指相对于90

°

小于或等于

±

10

°

的角变化范围,例如,小于或等于

±5°

、小于或等于

±4°

、小于或等于

±3°

、小于或等于

±2°

、小于或等于

±1°

、小于或等于

±

0.5

°

、小于或等

于

±

0.1

°

,或小于或等于

±

0.05

°

。

60.如果两个表面之间的位移不大于5μm、不大于2μm、不大于1μm或不大于0.5μm,那么可认为所述两个表面是共面的或大体上共面。

61.另外,量、比率和其它数值有时在本文中以范围格式呈现。可理解,此类范围格式是为便利和简洁起见而使用,且应灵活地理解为不仅包含明确地指定为范围限值的数值,且还包含涵盖于所述范围内的所有个别数值或子范围,如同明确地指定每一数值和子范围一般。

62.如本文中所使用,术语“导电(conductive)”、“导电(electrically conductive)”和“导电率”是指传输电流的能力。导电材料通常指示对电流的流动展现极少对抗或无对抗的那些材料。导电率的一个量度是西门子/米(s/m)。通常,导电材料是电导率大于约104s/m (例如至少105s/m或至少106s/m)的一种材料。材料的导电率有时可随温度而改变。除非另外指定,否则在室温下测量材料的导电率。

63.如本文所使用,除非上下文另外明确规定,否则单数术语“一”和“所述”可包含复数指示物。在一些实施例的描述中,提供于另一组件“上”或“上方”的组件可涵盖前一组件直接在后一组件上(例如,与后一组件物理接触)的情况,以及一或多个居间组件位于前一组件与后一组件之间的情况。

64.虽然已参考本发明的具体实施例描述和说明本公开,但这些描述和说明并不限制本公开。所属领域的技术人员可清楚地理解,在不脱离如由所附权利要求书限定的本公开的真实精神和范围的情况下,可作出各种改变且可在实施例内替换等同组件。各图解可能未必按比例绘制。归因于制造工艺中的变量等,本公开中的工艺再现与实际设备之间可能存在区别。本公开可存在没有具体说明的其它实施例。说明书和图应视为说明性的而不是限制性的。可做出修改以使特定情况、材料、物质组成、方法或过程适应本公开的目标、精神和范围。所有此类修改旨在属于所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作来描述本文公开的方法,但可理解,这些操作可在不脱离本公开的教示的情况下组合、细分或重新排序以形成等同方法。因此,除非本文特别指示,否则所述操作的次序和分组不是对本公开的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。