技术特征:

1.一种可动态调整的时钟路径电路,其特征在于,包括:由n级时钟延迟单元串联而成的时钟延迟链,n大于1;第1级时钟延迟单元的输入端连接时钟输入信号;第k级时钟延迟单元的输入端连接第(k

‑

1)级时钟延迟单元的输出端,2≤k≤n;所述时钟输入信号连接到第一多路选择器的输入端;各级所述时钟延迟单元的输出端通过对应的选择开关连接到所述第一多路选择器的输入端;各级所述时钟延迟单元的输出端输出所述时钟输入信号的各级延迟信号,所述第一多路选择器从所述时钟输入信号和所述时钟输入信号的各级延迟信号中选择一个信号作为时钟输出信号;各所述选择开关的控制信号以及所述第一多路选择器的选择信号通过延迟链控制电路控制,以实现对所述时钟输出信号的相位的动态调整。2.如权利要求1所述的可动态调整的时钟路径电路,其特征在于:所述选择开关的数量为(n

‑

1)个,第k级时钟延迟单元的输入端和输出端之间连接一个所述选择开关;所述第一多路选择器包括两个输入端,所述第一多路选择器的第一输入端连接所述时钟输入信号,所述第一多路选择器的第二输入端连接第n级时钟延迟单元的输出端。3.如权利要求2所述的可动态调整的时钟路径电路,其特征在于:各级所述时钟延迟单元的结构相同且延时相同。4.如权利要求3所述的可动态调整的时钟路径电路,其特征在于:各级所述时钟延迟单元都由偶数个反相器串联而成。5.如权利要求4所述的可动态调整的时钟路径电路,其特征在于:各级所述时钟延迟单元都由2个反相器串联而成。6.如权利要求2所述的可动态调整的时钟路径电路,其特征在于:时钟路径电路应用于双端口静态存储器的可测试设计电路中;所述可测试设计电路中包括两条所述时钟路径电路,两条所述时钟路径电路分别为第一时钟路径电路和第二时钟路径电路,令所述第一时钟路径电路的时钟输出信号为第一时钟输出信号,所述第二时钟路径电路的时钟输出信号为第二时钟输出信号,所述第一时钟路径电路的时钟输入信号为第一时钟输入信号,所述第二时钟路径电路的时钟输入信号为第二时钟输入信号;对所述双端口静态存储器进行测试时,所述双端口静态存储器的第一端口的时钟输入端连接所述第一时钟输出信号,所述双端口静态存储器的第二端口的时钟输入端连接所述第二时钟输出信号,通过在测试中动态调整所述第一时钟输出信号的相位以及所述第二时钟输出信号的相位调节所述双端口静态存储器的第一端口和第二端口间的端口时钟信号的延时。7.如权利要求6所述的可动态调整的时钟路径电路,其特征在于:对所述双端口静态存储器进行测试包括找出最差情形下的最低操作电压,最差情形对应于所述双端口静态存储器的第一端口和第二端口同时存取同一个位址,通过不断调整所述第一时钟输出信号的相位以及所述第二时钟输出信号的相位使所述双端口静态存储器的第一端口和第二端口的端口时钟信号的相位相同并从而达到所述双端口静态存储器的第一端口和第二端口同时存取同一个位址。

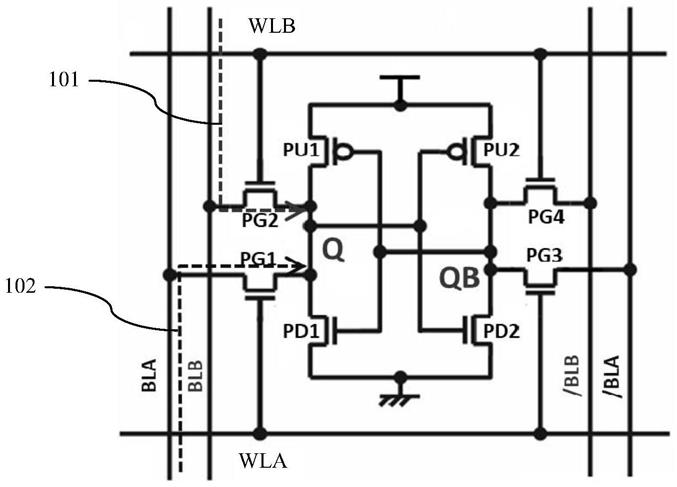

8.如权利要求6或7所述的可动态调整的时钟路径电路,其特征在于:所述可测试设计电路还包括两个第二多路选择器,第一个所述第二多路选择器的两个输入端分别连接第一时钟信号和第二时钟信号,第二个所述第二多路选择器的两个输入端分别连接第二时钟信号和地;第一个所述第二多路选择器的输出端连接所述所述第一时钟路径电路的输入端并提供所述第一时钟输入信号;第二个所述第二多路选择器的输出端连接所述所述第二时钟路径电路的输入端并提供所述第二时钟输入信号。9.如权利要求8所述的可动态调整的时钟路径电路,其特征在于:所述双端口静态存储器正常工作时,第一个所述第二多路选择器选择第一时钟信号作为所述第一时钟输入信号,第二个所述第二多路选择器选择第二时钟信号作为所述第二时钟输入信号,所述第一时钟路径电路的所述第一多路选择器选择所述第一时钟输入信号作为所述第一时钟输出信号,所述第二时钟路径电路的所述第一多路选择器选择所述第二时钟输入信号作为所述第二时钟输出信号。10.如权利要求9所述的可动态调整的时钟路径电路,其特征在于:所述双端口静态存储器测试时,第一个所述第二多路选择器选择第二时钟信号作为所述第一时钟输入信号,第二个所述第二多路选择器选择第二时钟信号作为所述第二时钟输入信号,所述第一时钟路径电路的所述第一多路选择器选择所述第一时钟输入信号对应级的延迟信号作为所述第一时钟输出信号,所述第二时钟路径电路的所述第一多路选择器选择所述第二时钟输入信号作为所述第二时钟输出信号。11.如权利要求2所述的可动态调整的时钟路径电路,其特征在于:所述延迟链控制电路通过(n

‑

1)位的数字信号信号控制(n

‑

1)个所述选择开关。12.如权利要求2所述的可动态调整的时钟路径电路,其特征在于:各所述第一多路选择器的选择信号通过所述延迟链控制电路提供的1位的数字信号提供。13.如权利要求8所述的可动态调整的时钟路径电路,其特征在于:各所述第二多路选择器的选择信号通过所述延迟链控制电路提供的1位的数字信号提供。14.如权利要求10所述的可动态调整的时钟路径电路,其特征在于:所述可测试设计电路植入于所述双端口静态存储器的内部;或者,所述可测试设计电路放置在所述双端口静态存储器的内建自我测试电路中。15.如权利要求6所述的可动态调整的时钟路径电路,其特征在于:在版图上所述可测试设计电路中的两条所述时钟路径电路完全对称且相同。

技术总结

本发明公开了一种可动态调整的时钟路径电路包括:由n级时钟延迟单元串联而成的时钟延迟链。第1级时钟延迟单元的输入端连接时钟输入信号。第k级时钟延迟单元的输入端连接第(k

技术研发人员:赖振安 陈俊晟

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:2021.08.31

技术公布日:2021/11/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。