1.本发明涉及一种半导体集成电路,特别涉及一种可动态调整的时钟路径电路。

背景技术:

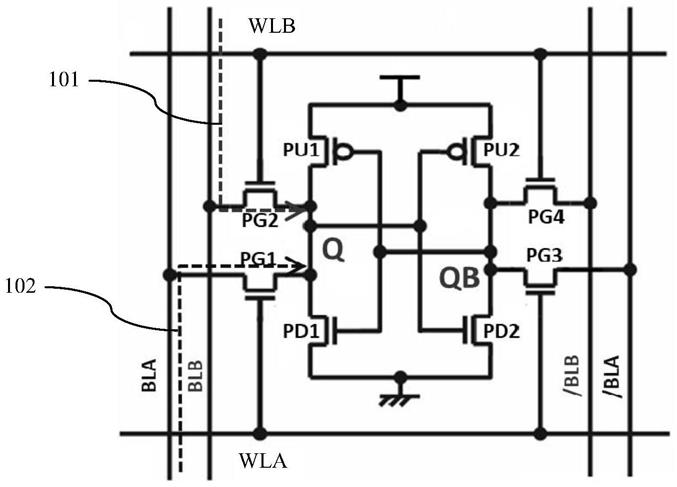

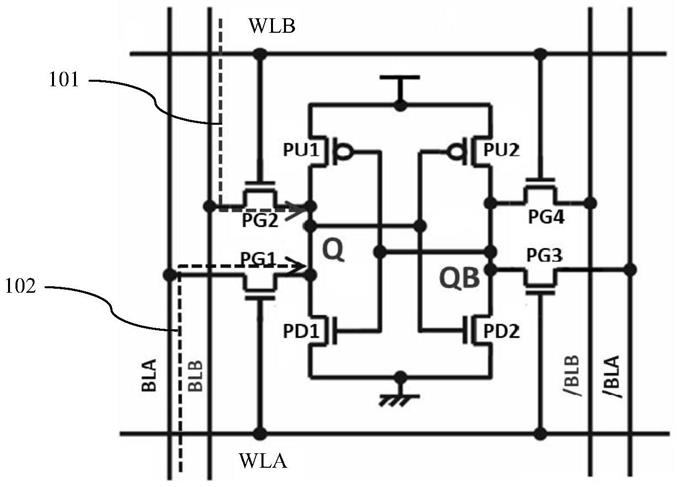

2.双端口(dp)静态存储器(sram)在集成电路中被广泛的应用在并行计算和不同频域中数据交换。如图1所示,是现有双端口sram的存储单元结构的电路图;包括由上拉管pu1和下拉管pd1组成的第一反相器以及由上拉管pu2和下拉管pd2组成的第二反相器,第一反相器的输出端和第二反相器的输入端连接且连接点形成存储节点q,第一反相器的输入端和第二反相器的输出端连接且连接点形成存储节点qb。第一端口包括选择管pg1和pg3组成,第二端口包括选择管pg2和pg4;第一端口的一对位线为bla和/bla,字线为wla;第二端口的一对位线为blb和/blb,字线为wlb。第一端口通常也称为a端口,第二端口通常称为b端口。

3.双端口静态存储器主要是在单端口的静态存储器基础上多了一个端口,它与单端口的静态存储器在本质上相同,因此在读写所面临的限制也类似。

4.由于双端口静态存储器支持在同一时间对某一个地址,经由不同的的端口读或写,这种操作方式使得写的alpha ratio和beta ratio比起单端口的静态存储器更加恶化。alpha ratio为上拉管和下拉管之间的idsat即饱和漏电流的比值;beta ratio为下拉管和选择管之间的idsat即饱和漏电流的比值。

5.如图2所示,是图1所示电路中节点q出现地弹现象时的信号曲线;以通过一个端口的读值操作为例,数据存值为0时即存储节点q为0时,在字线wl打开时即图1中的wla和wlb中的一个打开时,原本为0的存储节点q,因为分压原理而出现类似地弹(ground bounce)的现象。图2中的bl和blb的位线对为bla和/bla位线对以及blb和/blb位线对中的一个。

6.由于一个端口读取时就会出现地弹现象,两个端口同时读取同一个位址时,此现象将更为恶化。

7.地弹现象使得操作电压vcc无法一直降低,在特性分析时,如何有效求出真正意义上的最低操作电压vcc

min

,才是最重要的任务。

8.如图3所示,是现有双端口sram的结构图;双端口sram即dp sram201包括存储阵列202、写入电路203、读取电路204、控制电路(controller)205和地址解码器(address decoder)206。

9.存储阵列202中包括多个存储单元2021,存储单元2021的结构请参考图1所示。

10.写入电路203包括多个列对应的子写入电路2031。读取电路204包括多个列对应的子读取电路2041。

11.图3中,存储阵列202的各列分别用col.1、col.2

···

col.l表示;第一端口的一对位线分别用bl

1a

和bl

1a’、bl

2a

和bl

2a’···

bl

la

和bl

la’表示,字线分别用wl1a、wl2a

···

wlma表示;第二端口的一对位线分别用bl

1b

和bl

1b’、bl

2b

和bl

2b’···

bl

lb

和bl

lb’表示,字线分别用wl1b、wl2b

···

wlmb表示;存储单元2021分别用c加列和行组成的下标表示,具体

请参考图3所示,如第一列第一行对应的存储单元2021为c

1,1

。

12.a端口的地址为addr

a

,b端口的地址为addr

b.

13.a端口的读写控制信号用rwb

a

表示,b端口的读写控制信号用rwb

b

表示。

14.a端口的l位写信号用wdata

a

[1:l]表示,b端口的l位写信号用wdata

b

[1:l]表示。

[0015]

a端口的l位读取信号用rdata

a

[1:l]表示,b端口的l位读取信号用rdata

b

[1:l]表示。

[0016]

由于a,b端口有各自的时钟信号和输入输出信号,要在真正的同时存取同一个位址,还必须考虑在soc芯片时,a/b端口的两时钟信号的传递延时,仅仅是测试信号的同步,并不是真正的同时。而现有测试方法中仅考虑测试信号的同步。

[0017]

如图4所示,是现有双端口sram的测试方法中最找出最差情形(worst case)下的最低操作电压的二维shmoo图;目前业界的作法是利用二维shmoo,找出worst case的最低操作电压。图4中,虚线103对应于最佳情形(best case),虚线104对应于worst case。而实际的测试数据显示,双端口的worst case比起单端的读写worst case的最低操作电压可能高上100mv。

[0018]

然而,此种作法非常耗时,而且由于测试机所造成的信号间延时不同,测试的范围必需加大,图4中标记104对应的大括号范围内都需要进行测试,故测试范围大,会非常耗时。而单纯由版图上信号线长度估算的时延差异,没有参考作用。

技术实现要素:

[0019]

本发明所要解决的技术问题是提供一种可动态调整的时钟路径电路,能对时钟输出信号的相位进行动态调整,能应用于双端口静态存储器的可测试设计电路(dft)中并实现对双端口静态存储器进行有效且快速的测试和特性分析。

[0020]

为解决上述技术问题,本发明提供的可动态调整的时钟路径电路包括:

[0021]

由n级时钟延迟单元串联而成的时钟延迟链,n大于1。

[0022]

第1级时钟延迟单元的输入端连接时钟输入信号。

[0023]

第k级时钟延迟单元的输入端连接第(k

‑

1)级时钟延迟单元的输出端,2≤k≤n。

[0024]

所述时钟输入信号连接到第一多路选择器的输入端。

[0025]

各级所述时钟延迟单元的输出端通过对应的选择开关连接到所述第一多路选择器的输入端;各级所述时钟延迟单元的输出端输出所述时钟输入信号的各级延迟信号,所述第一多路选择器从所述时钟输入信号和所述时钟输入信号的各级延迟信号中选择一个信号作为时钟输出信号。

[0026]

各所述选择开关的控制信号以及所述第一多路选择器的选择信号通过延迟链控制电路控制,以实现对所述时钟输出信号的相位的动态调整。

[0027]

进一步的改进是,所述选择开关的数量为(n

‑

1)个,第k级时钟延迟单元的输入端和输出端之间连接一个所述选择开关。

[0028]

所述第一多路选择器包括两个输入端,所述第一多路选择器的第一输入端连接所述时钟输入信号,所述第一多路选择器的第二输入端连接第n级时钟延迟单元的输出端。

[0029]

进一步的改进是,各级所述时钟延迟单元的结构相同且延时相同。

[0030]

进一步的改进是,各级所述时钟延迟单元都由偶数个反相器串联而成。

[0031]

进一步的改进是,各级所述时钟延迟单元都由2个反相器串联而成。

[0032]

进一步的改进是,时钟路径电路应用于双端口静态存储器的可测试设计电路中。

[0033]

所述可测试设计电路中包括两条所述时钟路径电路,两条所述时钟路径电路分别为第一时钟路径电路和第二时钟路径电路,令所述第一时钟路径电路的时钟输出信号为第一时钟输出信号,所述第二时钟路径电路的时钟输出信号为第二时钟输出信号,所述第一时钟路径电路的时钟输入信号为第一时钟输入信号,所述第二时钟路径电路的时钟输入信号为第二时钟输入信号。

[0034]

对所述双端口静态存储器进行测试时,所述双端口静态存储器的第一端口的时钟输入端连接所述第一时钟输出信号,所述双端口静态存储器的第二端口的时钟输入端连接所述第二时钟输出信号,通过在测试中动态调整所述第一时钟输出信号的相位以及所述第二时钟输出信号的相位调节所述双端口静态存储器的第一端口和第二端口间的端口时钟信号的延时。

[0035]

进一步的改进是,对所述双端口静态存储器进行测试包括找出最差情形下的最低操作电压,最差情形对应于所述双端口静态存储器的第一端口和第二端口同时存取同一个位址,通过不断调整所述第一时钟输出信号的相位以及所述第二时钟输出信号的相位使所述双端口静态存储器的第一端口和第二端口的端口时钟信号的相位相同并从而达到所述双端口静态存储器的第一端口和第二端口同时存取同一个位址。

[0036]

进一步的改进是,所述可测试设计电路还包括两个第二多路选择器,第一个所述第二多路选择器的两个输入端分别连接第一时钟信号和第二时钟信号,第二个所述第二多路选择器的两个输入端分别连接第二时钟信号和地。

[0037]

第一个所述第二多路选择器的输出端连接所述所述第一时钟路径电路的输入端并提供所述第一时钟输入信号。

[0038]

第二个所述第二多路选择器的输出端连接所述所述第二时钟路径电路的输入端并提供所述第二时钟输入信号。

[0039]

进一步的改进是,所述双端口静态存储器正常工作时,第一个所述第二多路选择器选择第一时钟信号作为所述第一时钟输入信号,第二个所述第二多路选择器选择第二时钟信号作为所述第二时钟输入信号,所述第一时钟路径电路的所述第一多路选择器选择所述第一时钟输入信号作为所述第一时钟输出信号,所述第二时钟路径电路的所述第一多路选择器选择所述第二时钟输入信号作为所述第二时钟输出信号。

[0040]

进一步的改进是,所述双端口静态存储器测试时,第一个所述第二多路选择器选择第二时钟信号作为所述第一时钟输入信号,第二个所述第二多路选择器选择第二时钟信号作为所述第二时钟输入信号,所述第一时钟路径电路的所述第一多路选择器选择所述第一时钟输入信号对应级的延迟信号作为所述第一时钟输出信号,所述第二时钟路径电路的所述第一多路选择器选择所述第二时钟输入信号作为所述第二时钟输出信号。

[0041]

进一步的改进是,所述延迟链控制电路通过(n

‑

1)位的数字信号信号控制(n

‑

1)个所述选择开关。

[0042]

进一步的改进是,各所述第一多路选择器的选择信号通过所述延迟链控制电路提供的1位的数字信号提供。

[0043]

进一步的改进是,各所述第二多路选择器的选择信号通过所述延迟链控制电路提

供的1位的数字信号提供。

[0044]

进一步的改进是,所述可测试设计电路植入于所述双端口静态存储器的内部;或者,所述可测试设计电路放置在所述双端口静态存储器的内建自我测试电路中。

[0045]

进一步的改进是,在版图上所述可测试设计电路中的两条所述时钟路径电路完全对称且相同。

[0046]

本发明的时钟路径电路能对时钟输出信号的相位进行动态调整,在多端口中有利于对多端口之间的时钟波的相位进行控制并使得不同端口之间的时钟波相位能快速相同。

[0047]

本发明可动态调整的时钟路径电路能应用于双端口静态存储器的可测试设计电路中通过时钟路径电路的设置如通过两条时钟路径电路的设置能使双端口静态存储器的两个端口的时钟波尽可能无时延,从而能实现对双端口静态存储器进行有效且快速的测试和特性分析,能使找到最差情形下的最低操作电压的测试时间得以有效的降低。

[0048]

本发明能在版图上使可测试设计电路中的两条所述时钟路径电路完全对称且相同,且在启动dft即可测试设计电路时强制使用其中的一个时钟波当作输入以减少外部的绕线造成的时延,如此一来双端口静态存储器的两端口同时存取相同位址的时延便大幅减小,延时链的长度也可以有效减少,能进一步提高特性分析测试的速率。

附图说明

[0049]

下面结合附图和具体实施方式对本发明作进一步详细的说明:

[0050]

图1是现有双端口sram的存储单元结构的电路图;

[0051]

图2是图1所示电路中节点q出现地弹现象时的信号曲线;

[0052]

图3是现有双端口sram的结构图;

[0053]

图4是现有双端口sram的测试方法中最找出最差情形下的最低操作电压的二维shmoo图;

[0054]

图5是本发明实施例可动态调整的时钟路径电路的电路结构图;

[0055]

图6是本发明实施例可动态调整的时钟路径电路应用于双端口静态存储器的可测试设计电路后的电路结构图;

[0056]

图7是图6中双端口sram中一个端口测试时的信号曲线;

[0057]

图8是图6中的可测试设计电路的电路图;

[0058]

图9是采用本发明实施例双端口sram的可测试设计电路进行测试最找出最差情形下的最低操作电压的二维shmoo图。

具体实施方式

[0059]

如图5所示,是本发明实施例可动态调整的时钟路径电路301的电路结构图;本发明实施例可动态调整的时钟路径电路301包括:

[0060]

由n级时钟延迟单元302串联而成的时钟延迟链,n大于1。

[0061]

第1级时钟延迟单元302的输入端连接时钟输入信号clkin。

[0062]

第k级时钟延迟单元302的输入端连接第(k

‑

1)级时钟延迟单元302的输出端,2≤k≤n。

[0063]

所述时钟输入信号clkin连接到第一多路选择器303的输入端。

[0064]

各级所述时钟延迟单元302的输出端通过对应的选择开关304连接到所述第一多路选择器303的输入端;各级所述时钟延迟单元302的输出端输出所述时钟输入信号clkin的各级延迟信号,所述第一多路选择器303从所述时钟输入信号clkin和所述时钟输入信号clkin的各级延迟信号中选择一个信号作为时钟输出信号clkout。

[0065]

各所述选择开关304的控制信号以及所述第一多路选择器303的选择信号sel1通过延迟链控制电路控制,以实现对所述时钟输出信号clkout的相位的动态调整。

[0066]

所述选择开关304的数量为(n

‑

1)个,第k级时钟延迟单元302的输入端和输出端之间连接一个所述选择开关304。即所述选择开关304包括(n

‑

1)个。所述延迟链控制电路通过(n

‑

1)位的数字信号信号控制(n

‑

1)个所述选择开关304。图5中显示了3位所述选择开关304的控制信号即s0、s1和s2。

[0067]

所述第一多路选择器303包括两个输入端,所述第一多路选择器303的第一输入端连接所述时钟输入信号clkin,所述第一多路选择器303的第二输入端连接第n级时钟延迟单元302的输出端。

[0068]

所述第一多路选择器303的选择信号sel1通过所述延迟链控制电路提供的1位的数字信号提供。

[0069]

本发明实施例中,各级所述时钟延迟单元302的结构相同且延时相同。

[0070]

各级所述时钟延迟单元302都由偶数个反相器串联而成。较佳为,各级所述时钟延迟单元302都由2个反相器串联而成。

[0071]

如图6所示,是本发明实施例可动态调整的时钟路径电路应用于双端口静态存储器的可测试设计电路305后的电路结构图;时钟路径电路301应用于双端口静态存储器的可测试设计电路305中。

[0072]

所述可测试设计电路305中包括两条所述时钟路径电路301,两条所述时钟路径电路301分别为第一时钟路径电路301a和第二时钟路径电路301b,令所述第一时钟路径电路301a的时钟输出信号clkout为第一时钟输出信号clkout1,所述第二时钟路径电路301b的时钟输出信号clkout为第二时钟输出信号clkout2,所述第一时钟路径电路301a的时钟输入信号clkin为第一时钟输入信号clkin1,所述第二时钟路径电路301b的时钟输入信号clkin为第二时钟输入信号clkin2。

[0073]

对所述双端口静态存储器进行测试时,所述双端口静态存储器的第一端口的时钟输入端连接所述第一时钟输出信号clkout1,所述双端口静态存储器的第二端口的时钟输入端连接所述第二时钟输出信号clkout2,通过在测试中动态调整所述第一时钟输出信号clkout1的相位以及所述第二时钟输出信号clkout2的相位调节所述双端口静态存储器的第一端口和第二端口间的端口时钟信号aclk和bclk的延时。aclk表示第一端口的端口时钟信号,bclk表示第二端口的端口时钟信号。

[0074]

对所述双端口静态存储器进行测试包括找出最差情形下的最低操作电压,最差情形对应于所述双端口静态存储器的第一端口和第二端口同时存取同一个位址,通过不断调整所述第一时钟输出信号clkout1的相位以及所述第二时钟输出信号clkout2的相位使所述双端口静态存储器的第一端口和第二端口的端口时钟信号的相位相同并从而达到所述双端口静态存储器的第一端口和第二端口同时存取同一个位址。

[0075]

如图8所示,是图6中的可测试设计电路的电路图;较佳选择为,所述可测试设计电

路305还包括两个第二多路选择器,第一个所述第二多路选择器306a的两个输入端分别连接第一时钟信号clk1和第二时钟信号clk2,第二个所述第二多路选择器306b的两个输入端分别连接第二时钟信号clk2和地。

[0076]

第一个所述第二多路选择器306a的输出端连接所述所述第一时钟路径电路301a的输入端并提供所述第一时钟输入信号clkin1。

[0077]

第二个所述第二多路选择器306b的输出端连接所述所述第二时钟路径电路301b的输入端并提供所述第二时钟输入信号clkin2。

[0078]

各所述第二多路选择器的选择信号通过所述延迟链控制电路提供的1位的数字信号提供。第一个所述第二多路选择器306a的选择信号为信号sel2,第二个所述第二多路选择器306b的选择信号为信号sel3。

[0079]

所述双端口静态存储器正常工作时,第一个所述第二多路选择器306a选择第一时钟信号clk1作为所述第一时钟输入信号clkin1,第二个所述第二多路选择器306b选择第二时钟信号clk2作为所述第二时钟输入信号clkin2,所述第一时钟路径电路301a的所述第一多路选择器303选择所述第一时钟输入信号clkin1作为所述第一时钟输出信号clkout1,所述第二时钟路径电路301b的所述第一多路选择器303选择所述第二时钟输入信号clkin2作为所述第二时钟输出信号clkout2。

[0080]

所述双端口静态存储器测试时,第一个所述第二多路选择器306a选择第二时钟信号clk2作为所述第一时钟输入信号clkin1,第二个所述第二多路选择器306b选择第二时钟信号clk2作为所述第二时钟输入信号clkin2,所述第一时钟路径电路301a的所述第一多路选择器303选择所述第一时钟输入信号clkin1对应级的延迟信号作为所述第一时钟输出信号clkout1,所述第二时钟路径电路301b的所述第一多路选择器303选择所述第二时钟输入信号clkin2作为所述第二时钟输出信号clkout2。

[0081]

图8中信号ctr1中包括了所述第一时钟路径电路301a的(n

‑

1)位所述选择开关304的控制信号即s0、s1直至s(n

‑

1)以及所述第一时钟路径电路301a的选择信号sel1;信号ctr2中包括了所述第二时钟路径电路301b的(n

‑

1)位所述选择开关304的控制信号即s0、s1直至s(n

‑

1)以及所述第二时钟路径电路301b的选择信号sel1。

[0082]

图8的各信号中,sel3保持为1;在所述双端口静态存储器正常工作时sel2为1,在测试时sel2为0。

[0083]

信号ctr1中,所述第一时钟路径电路301a的(n

‑

1)位所述选择开关304的控制信号s0、s1直至s(n

‑

1)根据需要调节;在所述双端口静态存储器正常工作时所述第一时钟路径电路301a的sel1为1,在测试时所述第一时钟路径电路301a的sel1为0。

[0084]

信号ctr2中,所述第二时钟路径电路301b的sel1保持为1,所述第二时钟路径电路301b的(n

‑

1)位所述选择开关304的控制信号s0、s1直至s(n

‑

1)的值不需要考虑。这样,bclk一直取第二信号clk2;aclk则在工作时取第一信号clk1以及在测试时取第二信号clk2的延迟信号,这样bclk和ackl之间的延迟由第二信号clk2和第二信号clk2的延迟信号决定。也能对电路进行对称设置,使得,aclk一直取第一信号clk1,bclk则在工作时取第二信号clk2以及在测试时取第一信号clk1的延迟信号。

[0085]

所述可测试设计电路305植入于所述双端口静态存储器的内部;或者,所述可测试设计电路305放置在所述双端口静态存储器的内建自我测试电路中。

[0086]

在版图上所述可测试设计电路305中的两条所述时钟路径电路301完全对称且相同。

[0087]

如图9所示,是采用本发明实施例双端口sram的可测试设计电路进行测试最找出最差情形下的最低操作电压的二维shmoo图,由于本发明实施例能最大可能实现aclk和bclk的同时即同相位,故仅需测试标记501对应的范围即可;和图4相比,测试范围得到大大较小,测试速率也会增加。

[0088]

如图6所示,是本发明实施例可动态调整的时钟路径电路应用于双端口静态存储器的可测试设计电路后的电路结构图;a端口和b端口的地址信号a/b address会输入到地址缓冲器(address buffer)406中,两个端口时钟信号aclk和bclk分别有第一时钟信号clk1和第二时钟信号clk2通过所述可测试设计电路305形成。

[0089]

地址缓冲器406会将地址分别输入到列解码器(column decoder)402和行解码器(row decoder)403进行解码,用于选择存储阵列(memory array)401中的存储单元。

[0090]

读写控制信号read/write control控制读写;写入时需要采用驱动电路(driver)405进行驱动,读取时需要采用灵敏放大器(sense amplifier)404进行信号放大。

[0091]

如图7所示,是图6中双端口sram中一个端口测试时的信号曲线;以b端口为例:

[0092]

图7中的时钟信号clk对应于bclk,tbpwh为clk的高脉冲宽度,tbpwl为clk的低脉冲宽度;

[0093]

信号adrr表示地址信号如图6中的b address,tback表示信号adrr的起始位置和clk的上升沿之间的时间间隔;

[0094]

信号din表示输入数据信号,tbdck表示信号din的起始位置和clk的上升沿之间的时间间隔;

[0095]

信号dout表示输出数据信号,tbcko表示clk的上升沿和信号dout的起始位置之间的时间间隔;

[0096]

信号we为读写控制信号包括写即write控制信号和read控制信号,tbwck表示信号we的write控制信号的起始位置和clk的上升沿之间的时间间隔。

[0097]

由图7所示可知,读写过程中的各信号都需要通过时钟信号clk进行控制。

[0098]

本发明实施例的时钟路径电路301能对时钟输出信号clkout的相位进行动态调整,在多端口中有利于对多端口之间的时钟波的相位进行控制并使得不同端口之间的时钟波相位能快速相同。

[0099]

本发明实施例可动态调整的时钟路径电路301能应用于双端口静态存储器的可测试设计电路305中通过时钟路径电路301的设置如通过两条时钟路径电路301的设置能使双端口静态存储器的两个端口的时钟波尽可能无时延,从而能实现对双端口静态存储器进行有效且快速的测试和特性分析,能使找到最差情形下的最低操作电压的测试时间得以有效的降低。

[0100]

本发明实施例能在版图上使可测试设计电路305中的两条所述时钟路径电路301完全对称且相同,且在启动dft即可测试设计电路305时强制使用其中的一个时钟波当作输入以减少外部的绕线造成的时延,如此一来双端口静态存储器的两端口同时存取相同位址的时延便大幅减小,延时链的长度也可以有效减少,能进一步提高特性分析测试的速率。

[0101]

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限

制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。