并行路径延迟线

背景技术:

1.电子部件诸如半导体器件、电路和印刷电路板(pcb)组件在其制造期间和之后使用测试系统诸如自动化测试设备(ate)进行频繁测试。为了执行这些测试,ate可包括生成或测量测试信号的仪器,使得可在特定被测器件(dut)上测试一系列操作条件。例如,仪器可生成或测量数字信号的模式以使得能够测试半导体器件内的数字逻辑。数字信号具有由数据边缘(诸如上升边缘或下降边缘)在数字信号内的时域中的位置表示的时序。

2.ate通常用于施加具有特定时序的测试信号,或者在某些情况下,用于将具有协调时序的多个测试信号施加到dut的一个或多个测试点。为了协调时序,ate可被设计成使不同通道内的多个测试信号的生成同步。然而,仅使生成测试信号的时间同步可能不足以协调信号到达dut测试点的时间。通过ate内的仪器的传播延迟的差异可改变测试信号的相对时序,从而影响测试结果的准确性。为了提高测试准确性,可在ate中采用一条或多条延迟线以提供可调节的传播延迟。ate可通过调节通过延迟线的相对传播延迟来校准。此类校准可在不同时间进行,包括在制造ate时、在安装ate时、在定期时间表上或有时根据使用量进行。

技术实现要素:

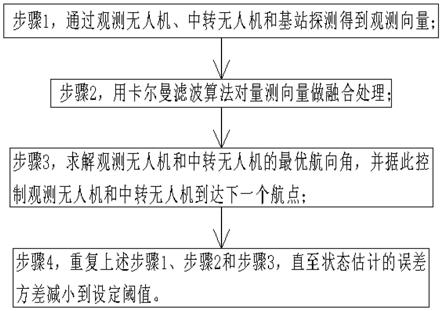

3.本技术的各方面涉及一种装置及其操作方法以延迟信号的时序。

4.根据一些实施方案,提供了一种用于延迟信号的装置。该装置包括具有输入和n个输出(n为至少二)的分离器电路。分离器电路被配置成在输入处接收具有第一数据速率的输入信号,并且在相应输出处生成n个分离信号,该n个分离信号中的每个分离信号具有小于第一数据速率的数据速率。该装置还包括延迟电路,该延迟电路被配置成基于n个分离信号生成延迟信号。延迟信号是具有延迟的输入信号。

5.根据一些实施方案,提供了一种用于延迟信号的方法。该方法包括利用分离器电路以第一数据速率接收具有多个上升边缘和下降边缘的输入信号;利用分离器电路以第二数据速率生成具有多个上升边缘和下降边缘的第一分离信号,以及以第三数据速率生成具有多个上升边缘和下降边缘的第二分离信号,其中第二数据速率和第三数据速率小于第一数据速率;在延迟电路处基于第一分离信号和第二分离信号来生成延迟信号。延迟信号是具有延迟的输入信号。

6.根据一些实施方案,提供了一种用于校准测试设备的方法。测试设备包括分离器电路,该分离器电路被配置成接收具有第一数据速率的输入信号,并且生成第一分离信号和第二分离信号,第一分离信号和第二分离信号各自具有小于第一数据速率的数据速率;第一延迟路径,该第一延迟路径被配置成以第一量延迟第一分离信号;第二延迟路径,该第二延迟路径被配置成以第二量延迟第二分离信号;以及组合器电路,该组合器电路被配置成分别在第一输入和第二输入处接收延迟的第一分离信号和延迟的第二分离信号,并且基于延迟的第一分离信号和延迟的第二分离信号在输出处生成延迟信号。该方法包括在组合器电路的输出处测量延迟信号;以及基于所测量的延迟信号校准第一量和第二量。

附图说明

7.各种方面和实施方案将结合以下附图描述。应当理解,附图未必按比例绘制。在附图中,不同图中所示的每个相同或近乎相同的部件由相同的标号表示。为了清晰起见,并非对每张附图中的每个部件都进行了标记。

8.图1为根据一些实施方案的其中可应用根据本技术的各个方面的延迟线架构的自动化测试系统的示例性实施方案的示意图;

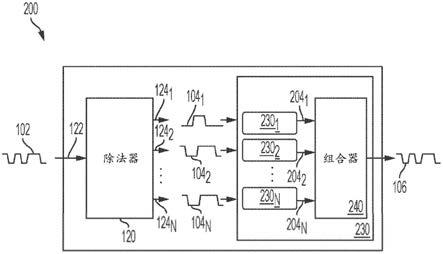

9.图2为示出根据本技术的一些方面的用于延迟信号的延迟线电路的示意图;

10.图3是示出根据一些实施方案的具有两个分离信号和两个延迟路径的图2所示的延迟线电路的示例性实施方式的示意图;

11.图4是示出根据一些实施方案的采用两个d锁存器的分离器电路的示例性实施方式的示意图;

12.图5示出根据一些实施方案的表示在图3和图4中所示的分离器电路420的不同操作状态的一系列信号波形;

13.图6示出了根据一些实施方案的表示校准方法期间的不同操作状态的一系列信号波形;和

14.图7是根据一些实施方案的具有用于校准的反馈路径的延迟线700的示意图。

具体实施方式

15.本发明人已经认识到并理解了用于有效地产生具有高时序精度但低功耗的高速信号的技术和电路设计。此类技术可能需要将具有高数据速率的输入信号分离成具有较低数据速率的并行分离信号。分离信号可以在被组合以生成作为具有延迟的输入信号的延迟信号之前在各自的并行延迟路径中被延迟。

16.本文所述的技术可用于在ate中生成时序信号。多个信号路径中的每个信号路径可包括延迟电路,并且由每个此类延迟电路引入的延迟量可以是可变的。每个延迟电路的延迟量可基于延迟信号的期望用途来确定,并且可被编程为测试系统的编程的一部分,然后在校准过程期间偏移确定的校准值,使得延迟量可校准信号路径之间的延迟变化。

17.以该方式延迟信号可使用紧凑且模块化的电路设计在高数据速度下提供高时序精度。在一些实施方案中,高速延迟线可由各自为模块化的多个较低数据速率的并行延迟线构造而成,从而简化了高速电路的电路设计。在一个实施方案中,根据本技术的各个方面的延迟线可对具有至少10gbps的数据速度的信号进行操作。此类高速延迟线可用带宽小于10gbps的部件实现,例如用半速率(5gbps)带宽部件实现。在一个示例中,半速率部件可使用几十个互补金属氧化物半导体(cmos)晶体管以紧凑设计构造。

18.该类型的可变延迟线可例如用于ate的引脚电子器件(pe)中。在ate内,数字测试仪器可用引脚电子器件(pe)、时序发生器(tg)来实现,其包含多个可变延迟线以按小时间增量延迟数字数据。tg获取来自模式发生器(pg)的矢量数据和周期信息,并且产生通过生成接收选通脉冲和驱动路径边缘时间来控制pe的报时信号。pe、pg和tg可为单独的部件,或者可被实现为包括大量晶体管的一个或多个集成电路(ic)。每个延迟线的可变延迟可基于使用从延迟线输出的信号。例如,如果延迟线输出连接到驱动器的控制输入,使得延迟线输出设定驱动路径边缘的时间,则可变延迟可被设定为产生控制驱动器在期望时间输出边缘

的信号。产生此类信号的延迟量可以基于该边缘偏移的编程值加上校准值,该校准值可针对信号路径确定,包括延迟电路和驱动器以及可影响生成此类边缘的时间的其他部件。

19.本发明人已经认识到并理解,当pe中的测试信号具有多个gbps数量级的高数据速率(诸如高达10gbps)时,可使用低成本和低功率技术(诸如cmos)实现可提供分辨率在单皮秒范围内的准确数据边缘放置的延迟线。

20.本技术的各个方面涉及一种延迟线架构,其中具有高数据速率的输入信号可在分离器电路中被分离成在相应的并行延迟路径中被延迟的具有较低数据速率的并行分离信号。因为分离信号中的每个分离信号与输入信号相比具有较低的数据(上升/下降)边缘速率,并且一般来讲相邻数据边缘之间具有较大的时序间隔,所以并联延迟路径可使用带宽低于输入信号的数据速率的电路部件来实现,例如使用基于65nm或40nm节点技术的cmos晶体管。本发明人已经认识到并理解,与使用单个高数据速率延迟线相比,除其他益处之外,使用以较低数据速率操作的较低带宽cmos部件降低了延迟线的总体电功率消耗。即使部件的数量可能更大,也是如此。较低带宽部件可为并行延迟线架构的延迟电路的一部分。

21.延迟电路被配置成使用多个并行延迟路径向分离信号中的每个分离信号施加选择性的延迟量,并且在组合器中组合延迟的分离信号以基于并行分离信号来延迟生成与输入信号基本上相同的延迟信号。延迟量可通过使用每个并行延迟路径中的可变延迟部件来编程。

22.在一些实施方案中,具有高数据速率的输入信号被分离成两个信号,两个信号中的每个信号具有输入信号的基本上一半的数据速率。对于此类信号,并且假设输入信号边缘可仅存在于由周期性时钟限定的位置处,则最小数据边缘间距是输入信号的最小数据边缘间距的两倍。对于足够长的随机输入信号,此类信号的平均数据速率将收敛至输入信号的数据速率的一半。然而,分离器电路可利用简单的电路部件来实现,并且每个分离信号的瞬时数据速率可基于输入信号中的上升边缘和下降边缘的模式随时间变化。

23.具有低带宽部件的延迟电路可用于延迟两个分离信号,这两个分离信号在重组为全速率信号时产生输入信号的延迟版本。此类延迟信号可相对于在半导体技术中实现的延迟线以降低的延迟线的电功率消耗产生,延迟线延迟全速率信号,同时提供准确的延迟量。

24.出于示出延迟线的电路设计的目的,本文描述了将输入信号分成两个基本上半速率的信号的电路。然而,应当理解,延迟线可用将输入信号分成n个并行路径的电路来实现,每个并行路径在被重新组合成输入的延迟版本之前被延迟。例如,双重分离和组合可以分层方式重复两次,从而得到四条平行路径。又如,可使用用于分离成两个以上信号并将它们组合的紧凑不分级电路,并且这些是本领域技术人员将认识到的下文所述的示例性设计的自然概括。

25.可使用任何合适的方法将输入信号分离成两个低速率分离信号。根据一方面,分离电路可用于在输入处接收输入信号并在两个输出处生成第一分离信号和第二分离信号。在一些实施方案中,第一分离信号和第二分离信号中的每个分离信号与输入信号相比平均包括给定时间段中的数据边缘量的一半,并且因此具有输入信号的基本上一半的数据速率。

26.因为输入信号通常包括一系列的连续且交替的上升边缘和下降边缘,所以本发明人已经认识到并理解,将输入信号分离成两个半速率分离信号的一种方式是针对从输入信

号接收的每个上升边缘/下降边缘交替地在两个分离信号中生成上升边缘/下降边缘。在一个示例性实施方案中,分离器电路被配置成响应于接收到输入信号中的上升边缘而在第一分离信号中但不在第二分离信号中生成第一边缘,并且响应于接收到输入信号中的上升边缘之后的下降边缘而在第二分离信号中但不在第一分离信号中生成第二边缘。实际上,第一分离信号中的数据边缘中的每个数据边缘对应于输入信号的上升边缘,而第二分离信号中的数据边缘中的每个数据边缘对应于输入信号的下降边缘。不希望受特定理论的约束,本发明人已经认识到,上述示例性实施方案中的分离器电路有效地作为“反向异或门”操作,使得输入处的逻辑高对应于两个输出处的逻辑高和逻辑低,并且输入处的逻辑低对应于具有相同极性的两个输出。应当理解,在此类“反向异或门”中,分离器电路的输入和两个输出的真实表与异或门的真实表相同,其中分离器电路的输入对应于真实表中的异或门输出,并且分离器电路的两个输出对应于真实表中的异或门输入。本发明人已经认识到并理解了实现此类“反向异或门”的简单电路设计。在一些实施方案中,反向异或门设计可用少量cmos晶体管来实现。基于cmos的延迟线电路设计可提供具有紧凑占有面积和小电功率消耗的器件。

27.较低速率信号可被单独处理,然后在异或门中组合回到输入信号的全速率。在延迟线的示例中,低速率分离信号的处理可能需要以可变的量延迟每个信号。

28.根据本技术的一方面,可例如通过使用连接到分离器电路的相应输出的两个并行延迟路径,将可单独调整的延迟施加到两个分离信号。这两个延迟路径生成两个相应的延迟分离信号,这些延迟分离信号可在组合器电路中组合。组合器电路被配置成组合延迟的两个较低数据速率分离信号中的每个分离信号中的数据边缘内携带的信息,以生成延迟的输入信号,该延迟的输入信号具有与输入信号相同的数据边缘的量和相对时序,但具有可变延迟。在一些实施方案中,异或门可在组合器电路内部使用,其中两个输入被配置成接收延迟的分离信号,并且异或门的输出被配置成生成延迟的输入信号。

29.根据本技术的另一方面,延迟电路的各个并联延迟路径内的延迟量可偏移校准值,以相对于原始输入信号在组合器电路的输出处产生延迟输入信号所需的延迟量。

30.参见附图,图1为可应用根据本技术的各个方面的延迟线架构的自动化测试系统的示例性实施方案的示意图。图1示出了根据本技术所公开的方法的包含测试计算机12的测试系统10,该测试计算机控制测试器16以对被测器件(dut)20执行测试。在某些情况下,测试器16可以是使用本领域已知的技术构造的自动测试设备(ate)。dut 20可以是用于测试的任何合适的器件。例如,dut 20可以是半导体器件。ate 16可包含用于生成和/或测量dut 20的多个测试信号14的电路。ate 16可包括被配置成生成或测量不同类型的模拟信号或数字信号的多个仪器。ate 16可包括一个或多个时序发生器,该时序发生器被配置成使不同通道内的多个测试信号的生成同步。在一些实施方案中,ate 16可包括可编程延迟线,该可编程延迟线用于延迟控制多个测试信号中的每个测试信号的多个时序信号中的每个时序信号的信号,如下文所详述。

31.应当理解,图1为自动化测试系统的极大简化图示。例如,尽管未示出,但测试系统10可包括控制ate 16内的仪器的操作的控制电路。另外,测试系统10可包括处理电路以处理测量并且确定dut 20是否正在正确操作。此外,尽管图1示出了正在测试单个dut 20的场景,但测试系统10可被配置成测试多个器件。无论生成或测量测试信号的仪器或其他部件

的数量以及被测器件的数量如何,测试系统10均可包括在dut 20与ate 16内的仪器之间路由信号的信号传送部件。

32.此外,应当理解,如图所示的其他部件是示例性的而非限制性的。例如,尽管测试计算机12在图1中被示出为个人计算机(pc),但应当理解,可使用任何合适的计算器件来实现测试计算机,例如,移动器件或计算机工作站。测试计算机12可以连接到网络并且能够通过网络访问资源和/或与连接到网络的一个或多个其他计算机通信。

33.图2为示出根据本技术的一些方面的用于延迟信号的延迟线电路的示意图。如图2所示,提供延迟线电路200以接收具有多个上升边缘/下降边缘的输入信号102,并且基于并行分离信号以可编程延迟生成与输入信号102基本上相同的延迟信号106。延迟线电路200可用于测试系统内的任何所需位置,包括引脚电子器件内。输入信号102可为在时序发生器内生成的高频边缘信号。由于引脚电子器件芯片中的每个通道和多个通道可存在多个边缘,因此引脚电子器件芯片中的延迟线电路200可存在多个副本。因此,实现具有可在gbps范围内操作的紧凑、低成本和低功率电路(例如cmos)的延迟线可为测试系统提供期望的特性。如本文所述的设计使得能够实现测试系统的这些特性。

34.在图2所示的示意图中,分离器电路120在输入122处接收输入信号102,并在相应的输出1241‑

124

n

处生成n个分离信号1041‑

104

n

,其中n是整数。根据一些实施方案,分离信号1041‑

104

n

中的每个分离信号具有比输入信号102中的数据速率更低的数据速率。延迟电路230接收分离信号1041‑

104

n

,并且生成延迟信号106,该延迟信号是具有延迟的输入信号102。延迟信号106具有基本上相同的数据边缘,其中数据边缘之间的相对时序与输入信号102基本上相同,但每个数据边缘的时序偏移了预定延迟。

35.根据本技术的一方面,输入信号102可以是具有5gbps、20gbps、1gbps至100gbps或5gbps至50gbps的数据速率的数字数据流,但是应当理解,本文公开的技术的各个方面可以与具有任何带宽的数字数据流一起使用。延迟线电路200被配置成高速延迟线电路。作为具体示例,数据速率可以是10gbps。n个分离信号1041‑

104

n

中的每个分离信号具有低于输入信号102的数据速率的相应数据速率。

36.在一些实施方案中,延迟电路230包括n个延迟路径2301‑

230

n

和组合器电路240。延迟路径2301‑

230

n

中的每个延迟路径接收相应的分离信号1041‑

104

n

,施加可调节量的延迟,并且生成相应的延迟分离信号2041‑

204

n

。如上所述,可调节延迟可包括可编程延迟,诸如可基于模式发生器中的编程由时序发生器来施加可调节延迟。该编程延迟可偏移校准值,该校准值被确定为校准例程的一部分,以补偿测试系统内的不同信号路径的传播延迟的变化。在一些实施方案中,延迟路径2301‑

230

n

中的每个延迟路径可单独延迟通过其的信号的上升边缘和下降边缘。此类配置能够为具有不对称的上升时间和下降时间的电路提供准确的延迟。延迟路径2301‑

230

n

中的每个延迟路径可通过本领域中已知的合适技术来实现,以将可调节量的延迟应用于在其中传播的信号。

37.组合器240接收n个延迟分离信号2041‑

204

n

,并且基于n个延迟分离信号2041‑

204

n

生成延迟信号106。

38.根据一方面,因为分离信号1041‑

104

n

具有比输入信号102更低的数据速率,所以低带宽部件可用于延迟电路230中并以比输入信号102更低的数据速率校准。因此,本技术的实施方案可在延迟高速信号方面提供高精度。在一个非限制性示例中,对于10gbps的输入

数据,延迟路径中的每个延迟路径可看到5gbps的数据速率,并且延迟线的后边缘误差(tee)可小于10ps。另一优点是使用在比输入信号的数据速率更低的带宽下操作的部件而降低了电功率消耗。

39.另一优点是模块化。因为延迟线包括较低带宽部件,所以在一些实施方案中,在高数据速率输入信号上操作的延迟线可包括并行模块,该并行模块本身是延迟线,但被配置成在较低数据速率输入信号上操作。例如,10gbps的延迟线可以将输入信号分离成具有5gbps数据速率的两个半速率分离信号,并且包括任何合适设计的两条并行5gbps的子延迟线,以在将结果组合成10gbps输入信号的延迟版本之前延迟相应的半速率分离信号。此类模块化可简化高速延迟线的电路设计。

40.图3是示出根据一些实施方案的具有两个分离信号和两个延迟路径的图2所示的延迟线电路的示例性实施方式的示意图。如图3所示,延迟线电路300被设置成接收输入信号d_1,并且生成与具有延迟的输入信号d_1基本上相同的延迟信号d_2。除法器电路320在输入322处接收输入信号d_1,并且在相应的输出3241和3242处生成两个分离信号xr和xf。延迟电路330包括两个延迟路径3301和3302以及异或门340。延迟路径3301和3302中的每个延迟路径接收相应的分离信号xr和xf,施加可调节量的延迟并且生成相应的延迟分离信号xr'和xf'。异或门340接收两个延迟分离信号xr'和xf',并且基于延迟分离信号xr'和xf'在异或门输出处生成延迟信号d_2。

41.根据本技术的一方面,输入信号d_1可以是具有5gbps、10gbps、20gbps、1gbps至100gbps或5gbps至50gbps的数据速率的数字数据流,但是应当理解,本文公开的技术的各个方面可以与具有任何带宽的数字数据流一起使用。两个分离信号xr和xf中的每个分离信号具有低于输入信号d_1的数据速率的相应数据速率。在一些实施方案中,xr和xf是具有基本上为d_1中的数据速率的一半的数据速率的半速率信号。在一个非限制性示例中,d_1具有10gbps的数据速率,而xr和xf具有5gbps的数据速率。

42.在一些实施方案中,分离器电路320被配置成作为“反向异或门”操作,使得输入322处的逻辑高对应于两个输出3241和3242处的一个逻辑高和一个逻辑低,并且输入322处的逻辑低对应于具有相同极性的两个输出3241和3242两者。应当理解,在此类配置中,分离器电路320在两个输出3241、3242和单个输入322之间的真实表将映射(00,01,10,11)到(0,1,1,0)。当输入在0和1之间切换时,两个输出改变状态,一次1位。例如,对于每个边缘转换,分离器电路320可以按照(0,0)、(0,1)、(1,1)、(1,0)的重复序列进行输出状态(xr,xf),返回到(0,0)以重复模式。

43.分离器电路320的示例性实施方式以及分离器电路320的输入和输出处的信号波形之间的关系将在下文中相对于图4和图5详细论述。

44.图4是示出根据一些实施方案的采用两个d锁存器的分离器电路的示例性实施方式的示意图。如图4所示,分离器电路420具有输入422以及两个输出4241和4242。除法器电路420包括两个d锁存器430和450。第一d锁存器430具有第一时钟输入431、第一锁存器d输入432和第一锁存器q输出433。第二d锁存器450具有第二时钟输入451、第二锁存器d输入452和第二锁存器q输出453。两个d锁存器430和450串联连接,其中第二锁存器d输入452连接至第一锁存器q输出433。第二锁存器q输出453被反转,然后连接到第一锁存器d输入432。两个d锁存器430和450的时钟异相,其中第一时钟输入431连接到输入422,并且第二时钟输入

451被配置成从输入422接收反转信号。输出4241连接到第二锁存器q输出453,并且4242连接到第一锁存器q输出433。

45.图4所示的除法器电路420是改进的d触发器(dff),在图中称为d2ff。输入422是d2ff的时钟,输出424是d2ff的q输出,并且在423处具有d2ff的d输入。dff是由异相时钟的两个边缘触发的d锁存器组成的触发器。在时钟的上升边缘,输入数据被锁存在第一锁存器中,而第二锁存器向输出提供相同的数据,即开始跟踪其输入数据。在时钟的下降边缘上,来自第一锁存器的锁存的数据被锁存到第二锁存器中,而第一锁存器开始跟踪输入数据。当上述序列在dff中重复时,输出4241(q)保持恒定,直到下一个时钟上升边缘。除法器电路420是d2ff,其中输出4241(q)被反转并连接到第一输入432(d),并且充当反转触发器(tff)。当tff被时钟控制时,输出q是时钟的除以2版本。对于给定的时钟模式,根据tff节点的初始状态,两种输出q模式是可能的,其中该两种可能的q模式彼此反转。

46.用于d锁存器和逆变器的晶体管电平电路在本领域中是已知的。此类部件可相对简单地实现,包括使用cmos晶体管。d锁存器的晶体管电平示意图例如可包括大约10个晶体管。逆变器可用少至两个晶体管来实现。任选地并且例如在差分电路中,逆变器可通过交换正极导线和负极导线来实现,而无需使用任何晶体管。除法器电路420因此可利用总共20

‑

25个晶体管来实现,并且可易于实现并且消耗低功率。

47.重新参考图3,当分离器电路320被实现为通过输入信号d_1以422时钟控制的d2ff 420时,其输出4241(q)将包含输入信号d_1的边缘的一半。根据一些方面,因为分离器电路420是正边缘触发dff,所以输出3241(q)处的信号xr中的任何数据边缘(下降或上升)对应于上升d_1边缘。同时,输出3242(d')是输出3241(q)中的上升时钟(d_1)边缘的下降时钟(d_1)边缘预览。应当理解,输出3242(d')处的信号xf具有用于任何下降d_1边缘的边缘(上升或下降)。因此,d_1被分离成两个半速率信号xr和xf,与d_1相比,这两个半速率信号在相同时间段期间各自具有数据边缘量的一半。

48.仍然参考图3,因为信号xr中的数据边缘仅对应于上升d_1边缘,而信号xf中的数据边缘仅对应于下降d_1边缘,所以应当理解,仅当xf为低(高)时才发生上升(下降)xr边缘。因此,当分离信号xr和xf分别在延迟路径3301和3302中延迟以变为延迟分离信号xr'和xf'时,可在异或门340中组合分离信号xr和xf以生成延迟信号d_2,该延迟信号是原始输入信号d_1的延迟版本。因此,在延迟路径3301中花费第一时间量之后,每个输入信号d_1上升边缘引起xr中的边缘,继而引起xr'中的边缘,并且作为响应,异或门340将为xr'边缘产生对应于d_1中的原始上升边缘的上升输出边缘。类似地,在延迟路径3302中花费第二时间量之后,每个输入信号d_1下降边缘引起下降输出边缘。实际上,延迟信号d_1中的边缘对应于输入信号d_1中的相应边缘。根据另一方面,可以校准施加到xr和xf的第一延迟量和第二延迟量,以调整d_2中的数据边缘的相对时序,从而与输入信号d_1中的数据边缘匹配,如下面关于图6和图7更详细地论述。

49.图5示出根据一些实施方案的表示图3和图4所示的分离器电路420的不同操作状态的一系列信号波形。波形500表示在输入422处接收到分离器电路420的输入信号d_1的时间线。波形510a

‑

510c表示响应于输入信号d_1而在分离器电路420的输出4241和4242处生成的两个分离信号xr和xf以及在异或门340的输出处的延迟信号d_2的时间线。波形520a

‑

520c表示响应于输入信号d_1的分离信号xr、xf和d_2的另选时间线。虽然波形500、510a

‑

510c和520a

‑

520c中的数据边缘如图5所示在时间上对齐,但应当理解,此类对齐仅出于说明目的是简化的,并且分离信号xr、xf和d_2中的数据边缘将受到传输延迟的影响,并且在d_2的情况下,延迟路径3301和3302中添加了额外的延迟时间。

50.根据xr和xf处的初始状态,d2ff 420响应于在输入422处从d_1接收的数据边缘而具有两种另选的启动模式。如图5所示,波形510a

‑

510c表示第一模式,其中d_1中的上升边缘501使xr随着上升边缘511从逻辑低翻转到逻辑高,而d_1中的上升边缘503引起xr中的下降边缘513。在波形520a

‑

520c所示的另选模式中,d_1中的上升边缘501使xr随下降边缘521从逻辑高翻转到逻辑低,而d_1中的上升边缘503引起xr中的上升边缘523。应当理解,xr的两个另选波形彼此反转,并且xr中的下降边缘/上升边缘总是对应于d_1中的上升边缘。从波形510a

‑

510c和520a

‑

520c还应当理解,xf响应于d_1中的上升边缘而保持在恒定逻辑电平,而没有任何数据边缘。

51.另一分离信号xf响应于输入信号d_1中的下降边缘而翻转。如图5中的波形510a

‑

510c所示,d_1中的下降边缘502使xf随着上升边缘512从逻辑低翻转到逻辑高,而d_1中的下降边缘504引起xf中的下降边缘514。在波形520a

‑

520c所示的另选模式中,d_1中的下降边缘502使xf随着下降边缘522从逻辑高翻转到逻辑低,而d_1中的上升边缘504引起xf中的上升边缘524。应当理解,xf的两个另选波形彼此反转,并且xf中的下降边缘/上升边缘总是对应于d_1中的下降边缘。从波形510a

‑

510c和520a

‑

520c还应当理解,xr响应于d_1中的下降边缘而保持在恒定逻辑电平,而没有任何数据边缘。

52.应当理解,如图5所示,当xr和xf中的仅一者处于逻辑高时,d_1处于逻辑高,并且当两个输出中的两者具有相同极性时,d_1处于逻辑低。应当理解,xr、xf和d_1的真实表将xr、xf中的(00,01,10,11)映射到d_1中的(0,1,1,0),这是异或门的真实表。因此,分离器电路420可以被视为“反向异或门”。

53.还应当理解,如图5所示,与输入信号d_1相比,xr和xf中的每一者包括给定时间段中数据边缘的数量的一半,因此分离信号xr和xf可被认为是半速率分离信号。与d_1相比,相邻数据边缘之间的间隔在xr、xf中也更长。在一些实施方案中,输入信号d_1中的数据边缘可以由作为数据周期的持续时间的单位间隔(ui)分开。例如,在图5中,d_1中的边缘501和502由一个ui隔开,而在半速率分离信号xr和xf中的每一者中,数据边缘之间的间隔从不比两个原始ui更接近。

54.重新参考图3,分离信号xr和xf在异或门340中组合以在输出处生成延迟信号d_2之前,分离信号xr和xf在相应的延迟路径3301、3302中单独延迟。如图5所示,在波形510a

‑

510c中,输出信号d_2具有对应于原始上升边缘501和503的上升边缘531和533。具体地讲,上升边缘531是基于xr中的上升边缘511,并且可称为xr_r,而d_2中的上升边缘533是基于xr中的下降边缘513,并且可称为xr_f。d_2中的下降边缘532对应于d_1中的下降边缘502,并且被称为xf_r,因为其是基于xf的上升边缘512。d_2中的下降边缘534对应于d_1中的下降边缘504,并且被称为xf_f,因为其是基于xf的下降边缘514。波形520a

‑

520c在另选模式中通常示出d_2和d_1、xr和xf的数据边缘之间的对应关系,并且不再详细讨论。

55.根据本技术的一方面,使用本文所述的技术延迟信号的优点是改善的上升/下降偏差(rfs)范围。rfs是上升边缘传播延迟和下降边缘传播延迟之间的差值。在称为上升/下降去歪斜(rfd)的操作中,电路可用于调整信号中的上升边缘和下降边缘之间的相对延迟。

rfd可例如用于更改信号流内的单脉冲宽度。根据一方面,如图3所示的延迟线架构300中的延迟路径3301、3302中的每个延迟路径可用于在其自身内执行rfd。例如并且参考图5中的波形510a

‑

510c,第一延迟路径3301可用于通过在xr内调整上升边缘/下降边缘511和513来在xr上执行rfd,而第二延迟路径3301可在xf上执行rfd以调整上升边缘/下降边缘512和514。因此,如图5所示,因为分离器电路320使数据路径的数量从一个全速率数据路径到两个半速率数据路径加倍,所以两个延迟路径3301、3302可以提供对四个上升边缘/下降边缘xr_r、xr_f、xf_r和xf_f的相对延迟时序的调整。因此,诸如分离器电路320的电路中rfs控制的范围增加。例如,电路可执行上升/上升去歪斜(rrd)以通过使用xr上的第一延迟路径3301中的rfd调整xr_r和xr_f的延迟时序来调整d_2的偶数上升边缘和奇数上升边缘之间的相对延迟。类似地,可以使用xf上的第二延迟路径3302中的rfd在d_2上执行下降/下降去歪斜(ffd)。

56.根据一个实施方案,输入信号d_1是10gbps信号,并且两个分离信号是半速率5gbps信号。根据本技术的各方面的延迟线可具有介于

‑

500ps和500ps之间的rfd(例如,xr_r或xr_f vs.xf_r或xf_f边缘去歪斜)范围。延迟线可具有介于

‑

200ps和200ps之间的rrd(例如,xr_r vs.xr_f边缘去歪斜)范围。延迟线可具有介于

‑

200ps和200ps之间的ffd(例如,xf_r vs.xf_f边缘去歪斜)范围。由于xr线处理输入信号的所有上升边缘并且xf处理输入信号的所有下降边缘,因此rfd范围特别大,当脉冲加宽被计为正rfd时,基本上从减去xr延迟线范围到加上xf延迟线范围。

57.本技术的一方面涉及校准延迟线(诸如如图3所示的延迟线300)内的并行延迟路径的方法。从图5中应当理解,根据初始加电或启动时xr和xf的初始状态,可存在两种启动模式。从图5应当理解,基于xr或xf的初始启动模式,不需要特殊测量或“启动”,因为无论启动模式如何,分离器电路420中接收的任何第一d_1边缘将根据波形510a

‑

510c或520a

‑

520c中的一者在xr或xf上导致边缘,并且延迟线将生成具有与d_1相同的边缘的延迟信号d_2。甚至启动后的第一边缘也被恰当地处理。

58.根据一方面,可在考虑其两种启动模式的同时校准延迟线300。如图5中的波形510a

‑

510c和520a

‑

520c所示,两种启动模式交换连续上升输出边缘的历史,并且类似地交换输出下降边缘的历史。例如,在波形510a

‑

510c所示的第一启动模式中,输出信号d_2中的两个连续上升边缘531、533对应于xr_r,接着是xr_f。相反,在波形520a

‑

520c所示的第二启动模式中,输出信号d_2中的连续上升边缘541、543首先对应于xr_f,接着是xr_r。边缘xr_r和xr_f均有助于输出信号d_2中的上升边缘,但作为xr延迟路径3301上的上升边缘或下降边缘行进。因此,需要通过调节延迟路径3301和3302来校准所有四个边缘xr_r、xr_f、xf_r和xf_f,使得分离器电路启动模式不影响所得输出信号d_2的时序校准。

59.现在将参考图6论述用于校准四个边缘xr_r、xr_f、xf_r和xf_f中的每个边缘的示例性方法。图6示出了根据一些实施方案的表示校准方法期间的不同操作状态的一系列信号波形。图6示出了具有以线数据间隔切换的上升边缘/下降边缘的输入信号d_1的波形600。

60.为了校准xr_r和xr_f,可调谐涉及第一延迟路径3301中的上升边缘和下降边缘的传播的可调节延迟,同时监测输出延迟信号d_2。在一些实施方案中,延迟分离信号xf'可被设置在恒定电平,以允许校准xr。波形610a

‑

610c示出了当xf'被迫使为逻辑低时,组合器异

或门340将上升边缘xr_r与xf'组合以生成d_2中的上升边缘611。因此,d_2中测量的上升边缘611表示上升边缘xr_r基于xr通过第一延迟路径3301的传播的时序延迟。为了校准上升边缘xr_r,可调节延迟路径3301中的上升边缘传播延迟量,直到d_2中监测到的上升边缘611处于所需的预定时序。根据延迟路径3301的性质,可使用任何合适的方法来调节其上升边缘的传播延迟量。在一个示例中,控制信号可被发送到延迟路径3301以指示上升边缘延迟量的变化。d_2中上升边缘611的所需预定时序可以是与已知基准(例如初始上升边缘601)相比延迟时间的设定量,但应当理解,可使用任何基准时序来校准上升边缘611的所需时序。在一个示例中,校准可以是相对的,即,对于每种边缘类型(诸如xr_r),可以调节延迟路径中的延迟设置,使得监测到的d_2边缘处于相对于基准延迟线设置的值。基准延迟线设置可通过到延迟线电路的一个或多个外部连接(例如通过连接到外部信号发生器和示波器)来单独校准。

61.延迟线中的其他独特边缘类型可类似地使用上文相对于xr中的上升边缘xr_r的校准所述的方法来校准。如图6中的波形620a

‑

620c所示,通过将xf'设置为恒定逻辑高,分离器电路420被迫以与图5的波形520a

‑

520c所示的另选启动模式类似的方式操作。d_2中的所测量的上升边缘613表示下降边缘xr_f基于xr的下降边缘通过第一延迟路径3301的传播的时序延迟。为了校准下降边缘xr_f,可调节延迟路径3301中的下降边缘传播延迟量,直到d_2中监测到的上升边缘613处于所需的预定时序。

62.类似地,为了校准用于第二延迟路径3302中的xf的传播的下降边缘延迟和上升边缘延迟,延迟分离信号xr'可被设置为恒定逻辑高(用于校准xf_r,参见波形630a

‑

630c)或恒定逻辑低(用于校准xf_r,参见波形640a

‑

640c)。为了校准xf_r,可以调节延迟路径3302中的上升边缘传播延迟量,直到d_2中监测到的下降边缘632处于所需的预定时序。为了校准xf_f,可调节延迟路径3302中的下降边缘传播延迟量,直到d_2中监测到的上升边缘644处于所需的预定时序。

63.根据本技术的一方面,可通过单独校准两个半速率延迟线来校准全速率延迟线。图7是具有用于校准的反馈路径的延迟线700的示意图。在延迟线700中,分离器电路720接收全速率输入信号d_1,并且生成在两个相应的并行延迟路径7301和7302中延迟的两个半速率分离信号xr和xf。延迟路径的输出处的延迟分离信号xr'和xf'在组合器异或门740中组合以生成延迟信号d_2。反馈路径750将异或门740的输出连接到两个延迟路径7301和7302,以使用例如上文结合图6所述的校准方法在延迟路径的校准期间监测输出信号。

64.在一些实施方案中,反馈路径750包括环形回路频率(rlf)框。rlf框包括通过围绕多个延迟元件闭合反转回路而形成的环形振荡器电路。回路元件的延迟的变化将导致频率的变化,从而允许精确测量时序延迟。示例性rlf具体实施在美国专利号9147620中详细描述,该专利全文通过引用并入本文。图7示出了半速率延迟路径7301、7302连接到反馈路径750以允许插入rlf信号来校准半速率延迟路径。提供控制单元752以用于将rlf信号插入到相应延迟路径7301、7302的两个drv_dd x{r,f}子线输入中。

65.以上描述本发明的至少一个实施例的多个方面,应当理解本领域的技术人员可易于进行各种改变、修改和改进。

66.例如,分离器由双向分离器示出。对于n路分离器,分离器可类似地起作用,将每个上升边缘和下降边缘分布到n个平行路径,其中对路径的上升边缘或下降边缘的每次应用

导致该路径内的状态变化。n可大于二的n相位除法器在本领域中是已知的,并且将是我们在说明书中所关注的两相位除法器的示例性概括。其将用作n路“反向异或”,并且在线路出口处,信号可与n路异或电路组合,这也是本领域已知的。

67.此类改变、修改和改进旨在作为本公开的一部分,并且被视为落入本发明的精神和范围内。此外,尽管指示出本发明的优点,但是应当理解,并非本文所述的技术的每个实施方案均将包括每个所述优点。一些实施方案可能无法实现本文有利地所述的任何特征,并且在一些情况下,可实现所述特征中的一个或多个以实现另外的实施方案。因此,上述的说明和附图仅作为举例的方式。

68.可单独地、结合地或以在上述实施例中未特别讨论的各种配置方式使用本发明的多种方面,因此其应用不受限于上述说明所述或附图中所示的组件的细节和配置。例如,在一个实施例中所述的方面可以任何方式与其他实施例中所述的方面结合。

69.另外,本发明可实施为一种方法,并且已提供其示例。作为该方法的一部分执行的操作可通过任何合适的方式来排序。因此,可构建以不同于所示的顺序执行操作的实施方案,这可包括同时执行某些操作,即使这些操作在各示例性实施方案中被示为顺序操作。

70.此类改变、修改和改进旨在作为本公开的一部分,并且被视为落入本发明的精神和范围内。此外,尽管指示出本发明的优点,但应当理解,并非本发明的每个实施例均将包括每个所述优点。一些实施例可未执行在本文中和在一些情况下有利的任何所述特征。因此,上述的说明和附图仅作为举例的方式。

71.在权利要求中使用诸如“第一”、“第二”、“第三”等序数术语修饰权利要求要素,其本身并不意味一个权利要求要素相对于另一个的任何优先权、优先序或顺序或者执行方法操作的时间顺序,而是仅用作将具有某个名称的一个权利要求要素与另一个具有相同名称(除了使用的序数术语)的要素加以区分的标签,以辨别权利要求要素。

72.另外,本文所用的短语和术语均是用于说明的目的,并且不应视为限制。本文中所使用的“包括”、“包含”或“具有”、“内含”、“涉及”和它们的变型形式均意味着包含其后所列的项目及其等同物以及额外的项目。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。