半导体存储器设备

1.交叉引用

2.本技术要求于2020年7月30日提交到韩国知识产权局的第10-2020-0094942号韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

3.本公开涉及半导体存储器设备,更具体涉及具有通孔导孔的堆叠式半导体存储器设备。

背景技术:

4.随着电子工业的不断发展,对电子元件的高功能性,高速度和小型化的需求不断增长。因此,已经对存储器单元是三维堆叠的半导体存储器设备进行了积极研究以改进半导体存储器设备的集成度,并且对存储器单元三维堆叠在用于操作半导体存储器设备的外围电路上的结构也已经进行了研究。

5.在存储器单元堆叠在外围电路上的半导体存储器设备的情况中,在外围电路上执行操作测试时,使用通孔导孔(thv)。然而,因为可放置在半导体存储器设备中的thv的总数是有限的,并且用于供应电源和操作存储器设备的信号的thv的数量随着集成度的增加而增加,所以对用于测试的thv的数量进行调整。

技术实现要素:

6.本公开的实施例提供一种半导体存储器设备,其包括用于检验状态机的输出序列的累加电路,该累加电路减少了用于测试的探测焊盘的数量以及连接到探测焊盘的通孔导孔(thvs)的数量。

7.然而,本公开的实施例不限于本文的那些实施例。通过参考下面给出的本公开的详细描述,本公开的上述和其他实施例对于本公开所属领域的普通技术人员而言将变得更加显而易见。

8.根据本公开的实施例,一种半导体存储器设备包括:包括存储器单元阵列的存储器单元区域;以及外围电路区域,其至少部分地与存储器单元区域重叠,并且包括配置成控制存储器单元阵列的操作的控制逻辑,其中控制逻辑包括状态机,被配置为响应于存储器单元区域的操作命令而输出多个状态信号,多个状态信号包括从第一输出端子输出的第一状态信号,以及从与第一输出端子不同的第二输出端子输出的第二状态信号,逻辑和计算器,被配置为基于第一状态信号或第二状态信号中的至少一个执行逻辑和计算,以及累加电路,被配置为接收逻辑和计算器的输出作为时钟信号,并响应于时钟信号而将触发信号输出到一个探测焊盘,累加电路通过穿透存储器单元区域的通孔导孔(thv)连接到探测焊盘。

9.根据本公开的实施例,一种半导体存储器设备包括:存储器单元阵列;状态机,被配置为响应于存储器单元阵列的操作命令而输出多个状态信号,并且包括第一触发器,其

输出多个状态信号中的第一状态信号,以及第二触发器,第二触发器输出第二状态信号,第二状态信号在输出多个状态信号中的第一状态信号之后被输出;逻辑和计算器,被配置为基于第一状态信号或第二状态信号中的至少一个执行逻辑和计算;以及累加电路,被配置为接收逻辑和计算器的输出作为时钟信号并输出触发信号,累加电路的输出被反馈并提供给累加电路。

10.根据本公开的实施例,一种半导体存储器设备包括:存储器单元区域,其包括第一导电元件;外围电路区域,其包括垂直地连接到第一导电元件的第二导电元件,并且通过第一导电元件和第二导电元件垂直地连接到存储器单元区域;多条单元串,单元串中的每一条包括存储器单元区域中的多个存储器单元,多条单元串包括连接到多个存储器单元的多条字线,连接到多条单元串一端的多条位线,以及连接到多条单元串的另一端的接地选择线;状态机,被配置为响应于外围电路区域内的多条单元串的操作命令而输出多个状态信号,其包括从第一输出端子输出的第一状态信号,以及在输出第一状态信号之后从不同于第一输出端子的第二输出端子输出的第二状态信号;逻辑和计算器,被配置为基于第一状态信号和第二状态信号中的至少一个执行逻辑和计算;以及控制逻辑,其包括累加电路,累加电路被配置为接收逻辑和计算器的输出作为时钟信号,并且响应于时钟信号而将触发信号输出到一个探测焊盘,累加电路通过穿透存储器单元区域的通孔导孔(thv)连接到探测焊盘。

附图说明

11.通过参考附图详细考虑本公开的实施例,本公开的上述和其他实施例将变得更加显而易见,其中:

12.图1为示出根据实施例的半导体存储器设备的框图;

13.图2为示出根据实施例的包括在半导体存储器设备中的多个存储器单元块中的单个存储器单元块的电路图;

14.图3为用于说明根据本公开的实施例的有限状态机的框图;

15.图4为用于说明根据本公开的实施例的有限状态机的框图;

16.图5为用于说明根据本公开的实施例的有限状态机和累加电路的框图;

17.图6为示出根据实施例的半导体存储器设备的透视图;

18.图7为示出沿图6的线a-a’所取的用于说明根据本公开的实施例的半导体存储器设备的剖面图;

19.图8为示出沿图6的线a-a’所取的用于说明根据本公开的一些其他实施例的半导体存储器设备的剖面图;

20.图9为用于说明根据本公开的实施例的累加电路的操作的时序图;

21.图10为用于说明根据本公开的实施例的累加电路的操作的框图;

22.图11为用于说明根据本公开的实施例的累加电路的操作的框图;

23.图12为用于说明根据本公开的实施例的累加电路的框图;以及

24.图13为用于说明根据本公开的实施例的累加电路的操作的时序图。

具体实施方式

25.下文中,可以在参考附图的同时描述根据本公开的发明构思的实施例。在图1-13的描述中,相同的附图标记可用于基本相同的组件,并且不需要提供组件的重复说明。另外,在本公开的各个附图中,相似的附图标记可用于相似的组件。

26.图1示出了根据实施例的半导体存储器设备10。

27.参考图1,半导体存储器设备10可以包括存储器单元阵列20和外围电路30。

28.存储器单元阵列20可以包括多个存储器单元块blk1到blkn。存储器单元块blk1到blkn中的每一个可以包括多个存储器单元。存储器单元块blk1到blkn可以通过位线bl,字线wl,至少一条串选择线ssl以及至少一条接地选择线gsl连接到外围电路30。

29.具体地,存储器单元块blk1到blkn可以通过字线wl,至少一条串选择线ssl和至少一条接地选择线gsl连接到外围电路30的行解码器33。另外,存储器单元块blk1到blkn可以通过位线bl连接到外围电路30的页缓冲器35。

30.外围电路30可以从半导体存储器设备10的外部接收地址addr,命令cmd和控制信号ctrl,并且可以向半导体存储器设备10外部的设备发送数据和/或从半导体存储器设备10外部的设备接收数据。外围电路30可以包括控制逻辑37、行解码器33、页缓冲器35、以及生成用于操作的各种电压的电压产生器38。

31.外围电路30还可以包括诸如输入/输出(i/o)电路的各种子电路,以及误差校正电路,其用于校正从半导体存储器设备10的存储器单元阵列20读取的数据中的误差。

32.控制逻辑37可以包括有限状态机(fsm)40和累加电路41。有限状态机40是电路,其根据从外部输入的命令cmd和/或控制信号ctrl和/或时间变化来输出状态信号。此外,控制逻辑37可以通过累加电路41监测要从有限状态机40输出的状态信号。在替代实施例中,有限状态机40和累加电路41可以被包括在外围电路30内部的另一配置中,并且本技术的发明构思不限于图1的布置。可以在下面进一步找到对有限状态机40和累加电路41更具体的说明。

33.控制逻辑37可以连接到行解码器33,电压产生器38,页缓冲器35和/或任何其他i/o电路。控制逻辑37可以控制半导体存储器设备10的总体操作。控制逻辑37可以响应于控制信号ctrl而生成在半导体存储器设备10中使用的各种内部控制信号。

34.例如,执行诸如程序操作或擦除操作的存储器操作时,控制逻辑37可以调整要提供给字线wl和位线bl的电压电平。

35.行解码器33可以响应于地址addr而选择多个存储器单元块blk1到blkn中的至少一个,并且可以选择所选的存储器单元块blk1到blkn的至少一条字线wl,至少一条串选择线ssl以及至少一条接地选择线gsl。行解码器33可以将用于执行存储器操作的电压发送到所选择的存储器单元块blk1到blkn的字线wl。

36.页缓冲器35可以通过位线bl连接到存储器单元阵列20。页缓冲器35可以用作写驱动器或感测放大器。具体地,在程序操作时,页缓冲器35用作写驱动器,并且可以根据要存储在存储器单元阵列20中的数据向位线bl施加电压。另一方面,在读取操作时,页缓冲器35用作感测放大器并且可以感测存储在存储器单元阵列20中的数据。

37.电压产生器38可以根据发送到控制逻辑37的信号向半导体存储器设备中的所有配置提供电压。尽管附图示出了将电压提供给行解码器33,但是半导体存储器设备10的操

作所需的电压还可以被提供给页缓冲器35和控制逻辑37,但不限于此。

38.图2示出了根据实施例的半导体存储器设备10中包括的多个存储器单元块blk1到blkn中的单个存储器单元块。图2的单个存储器单元块可以对应于图1所示的多个存储器单元块blk1到blkn中的一个。

39.参考图2,根据实施例的存储器单元块可以包括公共源极线csl、多条位线bl0、bl1和bl2以及放置在公共源极线csl和位线bl0、bl1和bl2之间的多条单元串cstr。

40.多条单元串cstr可以并联到位线bl0到bl2中的每一条。多条单元串cstr可以共同连接到公共源极线csl。例如,图2的实施例中,三条单元串cstr连接到位线中的每一条,但不限于此。也就是说,多条单元串cstr可以放置在多条位线bl0到bl2和一条公共源极线csl之间。多条公共源极线csl可二维放置。这里,相同的电压可被电施加到公共源极线csl,或者公共源极线csl中的每一条可被共同和/或单独电控制。

41.例如,每条单元串cstr可以由串联的串选择晶体管sst1和sst2,串联的存储器单元mct,以及接地选择晶体管gst组成。另外,每个存储器单元mct包括数据存储元件。

42.作为示例,每条单元串cstr可以包括串联的第一和第二串选择晶体管sst1和sst2,第二串选择晶体管sst2可以连接到位线bl0到bl2,并且接地选择晶体管gst可以连接到公共源极线csl。存储器单元mct可以串联在第一串选择晶体管sst1和接地选择晶体管gst之间。

43.此外,每条单元串cstr还可以包括连接在第一串选择晶体管sst1和存储器单元mct之间的虚设单元dmc。虚设单元dmc可以可替代地连接在接地选择晶体管gst和存储器单元mct之间。作为示例,在每条单元串cstr中,接地选择晶体管gst以及第一串选择晶体管sst1和第二串选择晶体管sst2每个可以由串联的多个金属氧化物半导体(mos)晶体管组成。作为替代示例,每条单元串cstr可以包括单个串选择晶体管。

44.根据实施例,第一串选择晶体管sst1可以由第一串选择线ssl1控制,并且第二串选择晶体管sst2可以由第二串选择线ssl2控制。存储器单元mct可以由多条字线wl0到wln控制,并且虚设单元dmc可以由虚设字线dwl控制。此外,接地选择晶体管gst可以由接地选择线gsl0、gsl1或gsl2控制。公共源极线csl可以公共地连接到接地选择晶体管gst的源极。

45.单条单元串cstr可以由具有与公共源极线csl不同距离的多个存储器单元mct组成。此外,多条字线wl0到wln和dwl可以放置在公共源极线csl与位线bl0到bl2之间。

46.基本放置在距公共源极线csl相同距离处的存储器单元mct的栅电极共同连接到字线wl0到wln和dwl中的一条,并且可以处于等电位状态。替代地,即使存储器单元mct的栅电极被放置在与公共源极线csl基本相同的水平时,可以独立控制放置在不同行或列中的栅电极。

47.接地选择线gsl0到gsl2以及串选择线ssl1和ssl2可以,例如,在与字线wl0到wln和dwl相同的方向上延伸。与公共源极线csl放置在基本相同的水平上的接地选择线gsl0到gsl2可以彼此电分离。同样,与公共源极线csl放置在不同水平的串选择线ssl1和ssl2可以彼此电分离。

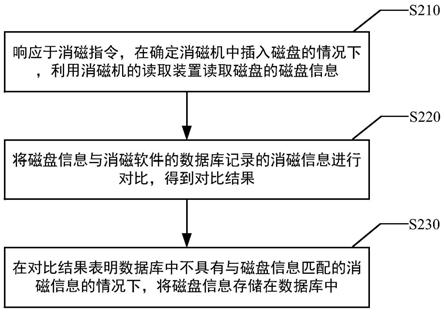

48.图3和图4用于说明根据本公开的实施例的图1的有限状态机40。图5用于说明根据本公开的实施例的有限状态机40和累加电路41。

49.参考图3和图4,有限状态机40是系统,其基于从根据实施例的半导体存储器设备

10的外部输入的命令(例如,图1的cmd)和/或控制信号(例如,图1的ctrl),和时间变化输出状态信号,其中有限状态机40可以包括下一状态逻辑401,当前状态电路402和输出逻辑403。

50.下一状态逻辑401和输出逻辑403可以包括算术逻辑单元,算术逻辑单元反过来每个可以包括具有加法器( )和减法器(-)作为硬件的算术计算器,和包括逻辑和运算符(or),逻辑积运算符(and)和互斥逻辑和运算符(xor)的逻辑计算器,并且每个可以是组合电路,其中它们的互连关系可以包括串联,并联及其组合。

51.下一状态逻辑401接收与命令信号(例如,图1的cmd)和/或控制信号(例如,图1的ctrl)相关联的输入信号400s和当前状态信号402s。对输入信号400s和当前状态信号402s进行诸如算术逻辑计算的处理以输出下一状态信号401s。

52.取决于有限状态机40的类型,可以向输出逻辑403提供输入信号400s。当有限状态机40是米利状态机,其中输出值由其当前状态和当前输入两者确定时,输出逻辑403一起接收输入信号400s和当前状态信号402s以输出输出信号403s。当有限状态机40是moore状态机,其中输出值仅由其当前状态确定时,输出逻辑403接收当前状态信号402s以输出输出信号403s。然而,本公开的发明构思不限于有限状态机40的前述类型。

53.当前状态电路402可以包括锁存器,其包括r-s锁存器,m-s锁存器等,其接收时钟信号clk的输入并且响应于时钟信号鉴于时间概念而处理数据,以及触发器,其包括d触发器,j-k触发器和边缘-触发触发器等,而且可以是顺序电路,其中它们的互连关系包括串联,并联和/或其组合。虽然图4示出了d触发器,这是为了易于解释,并且本公开的发明构思不限于此。

54.当前状态电路402可以包括第0触发器402_0,第一触发器402_1,第二触发器402_2,第三触发器402_3至第n-1触发器402_n-1以及第n触发器402_n。触发器之间的互连关系可以包括串联,并联和/或其组合。在图4中,尽管示出了当前状态电路402的触发器被提供有公共时钟信号clk,但是可以为每个触发器提供不同的时钟信号clk以控制多个当前状态信号402s中的每一个,多个当前状态信号402s中的每一个从根据本实施例的每个相应的触发器中输出。

55.第0触发器402_0的输出端子输出多个当前状态信号402s中的第0当前状态信号402_0s,第一触发器402_1的输出端子输出多个当前状态信号402s中的第一当前状态信号402_1s,并且第三至第n触发器402_3到402_n的输出端子也可以分别输出第三至第n当前状态信号402_3s到402_ns。

56.然而,对于根据实施例的当前状态电路402中包括的触发器,从第一触发器402_1输出的第一当前状态信号402_1s是在第0当前状态信号402_0s从第0触发器402_0输出之后输出的,并且从第二触发器402_2输出的第二当前状态信号402_2s是在第一当前状态信号402_1s从第一触发器402_1输出之后输出的。下文中,第三至第n触发器402_3到402_n中的每一个的第三至第n输出信号402_3s到402_ns也可以分别在输出先前的第二至第n-1输出信号402_2s到402_n-1s之后输出。也就是说,从第一至第n触发器402_1到402_n中的每一个输出的第一至第n当前状态信号402_1s到402_ns中的每一个可以分别在先前的当前状态信号402_0s到402_n-1s的输出之后顺序输出。

57.根据实施例的累加电路41_1可以包括第一逻辑和计算器411,第一累加触发器

413,第一互斥逻辑和计算器415,第二逻辑和计算器412,第二累加触发器414,以及第二互斥逻辑和计算器416。

58.第一逻辑和计算器411连接到偶数触发器的输出端子,该偶数触发器包括第0触发器402_0,第二触发器402_2,一直到第n-1触发器(如果n是奇数),并且可以向其提供第0当前状态信号402_0s,第二当前状态信号402_2s,一直到第n-1当前状态信号402_n-1s。第二逻辑和计算器412连接到奇数触发器的输出端子,该奇数触发器包括第一触发器402_1,第三触发器402_3,一直到第n触发器402_n(如果n是奇数),并且可以向其提供第一当前状态信号402_1s,第三当前状态信号402_3s一直到第n当前状态信号402_ns。然而,根据替代实施例,n可以是偶数,并且在这种情况下,第一逻辑和计算器411连接到第n触发器402_n的输出端子,第二逻辑和计算器412可以连接到第n-1触发器402_n-1的输出端子。

59.第一累加触发器413可以接收第一逻辑和计算器的输出作为时钟信号。第一累加触发器413接收第一互斥逻辑和计算器415的输出作为d信号。第一互斥逻辑和计算器415通过反馈接收第一累加触发器413的输出,与第一累加触发器413的输出一起接收电源电压vdd,并且总是接收至少一个数值1。从第一累加触发器413输出的第一触发信号441s可以提供给第一探测焊盘441。

60.实施例可以包括由金属制成的焊盘,但是不限于此。例如,尽管实施例可以涉及由金属制成的焊盘,但是应当理解的是这样的焊盘可以由任何导电材料形成,例如非金属导电材料和/或主要由非金属材料形成的化合物,没有限制。

61.第二累加触发器414可以接收第二逻辑和计算器412的输出作为时钟信号。第二累加触发器414接收第二互斥逻辑和计算器416的输出作为d信号。第二互斥逻辑和计算器416通过反馈接收第二累加触发器414的输出,与第二累加触发器414的输出一起接收电源电压vdd,并且总是接收至少一个数值1。从第二累加触发器414输出的第二触发信号442s可以提供给第二探测焊盘442。累加电路41_1的具体操作可以在下面作进一步详细说明。

62.图6为示出根据实施例的半导体存储器设备10的透视图。图7为沿图6的线a-a’所取的用来说明根据本公开的实施例的半导体存储器设备10_1的剖视图。

63.参考图6和图7,根据实施例的半导体存储器设备10可以包括外围电路区域ps和存储器单元区域cs。

64.外围电路区域ps可以包括埋置区域,从平面视角来看在第三方向d3上其与存储器单元区域cs重叠,以及非埋置区域,从平面视角来看在第三方向d3上其不与存储器单元区域cs重叠。此外,尽管不必将其包括在非埋置区域中,但是外围电路区域ps可以包括放置在存储器单元区域cs上的上方布线体的一部分。

65.存储器单元区域cs可以包括图1的存储器单元阵列20的多个存储器单元块blk1到blkn中的至少一个,并且外围电路区域ps可以包括图1的外围电路30。

66.参考图7,根据实施例的半导体存储器设备10_1可以具有芯片到芯片(c2c)结构。c2c结构可以意味着在第一晶片上制造包括存储器单元区域cs的上方芯片并且在与第一晶片不同的第二晶片上制造包括外围电路区域ps的下方芯片,其中上方芯片和下方芯片通过键合结构彼此连接。作为示例,键合结构可以包括导电通路,该导电通路将形成在上方芯片的最上面的金属层上的键合金属与形成在下方芯片的最上面的金属层上的键合金属彼此电连接。例如,当键合金属由铜(cu)形成时,键合结构可以是cu-cu键合结构,并且键合金属

还可以由铝或钨形成。

67.半导体存储器设备10_1的外围电路区域ps和存储器单元区域cs中的每一个可以包括外部焊盘键合区域pa,字线键合区域wlba和位线键合区域blba。

68.外围电路区域ps可以包括第一基底310,层间绝缘层315,形成在第一基底310上的多个电路元件320b和320c,包括在图5的第一累加触发器413中的第一元件421,包括在图5的第二累加触发器414中的第二元件422,连接到多个电路元件320b和320c、第一元件421和第二元件422中的每一个的第一金属层330a、330b和330c,第一元件421和第二元件422中,以及形成在第一金属层330a、330b和330c上的第二金属层340a、340b和340c。在一个实施例中,第一金属层330a、330b和330c可以由具有相对高电阻的钨形成,并且第二金属层340a、340b和340c可以由具有相对低电阻的铜形成。

69.尽管在本说明书中仅示出和说明了第一金属层330a、330b和330c以及第二金属层340a、340b和340c,但是本公开不限于此,并且还可以在第二金属层340a、340b和340c上形成至少一个或多个金属层。在第二金属层340a、340b和340c上形成的至少一个或多个金属层中的一些可以由铜等形成,其具有低于形成第二层金属层340a、340b和340c的材料的电阻,诸如铝等。

70.层间绝缘层315放置在第一基底310上以覆盖多个电路元件320b和320c,第一元件421,第二元件422,第一金属层330a、330b和330c以及第二金属层340a、340b、340c,并且可以包括绝缘材料,诸如氧化硅和/或氮化硅

71.下方键合金属371b和372b可以形成在字线键合区域wlba的第二金属层340b上。在字线键合区域wlba中,外围电路区域ps的下方键合金属371b和372b可以通过键合结构电连接到存储器单元区域cs的上方键合金属271b和272b,并且下方键合金属371b和372b和上方键合金属271b和272b可以由铝、铜、钨等形成。

72.存储器单元区域cs可以提供多个存储器单元块(例如,图1的blk1到blkn)中的至少一个。存储器单元区域cs可以包括第二基底210和公共源极线220。多条字线230(例如,231到238)可以沿着垂直于第二基底210的上表面的方向d3堆叠在第二基底210的下表面210b上。串选择线和接地选择线可以放置在字线230的上方和下方,并且多条字线230可以放置在字线选择线和接地选择线之间。

73.在位线键合区域blba中,通道结构ch在垂直于第二基底210的上表面的方向上延伸,并且可以穿透字线230,串选择线和接地选择线。通道结构ch可以包括数据存储层,通道层,埋置绝缘层等,并且通道层可以电连接到第一金属层250c和第二金属层260c。例如,第一金属层250c可以是位线接触,并且第二金属层260c可以是位线。在一个实施例中,位线260c可以沿着平行于第二基底210的上表面的第二方向d2延伸。

74.在图7所示的实施例中,其中布置有通道结构ch和位线260c的区域可以被定义为位线键合区域blba。位线键合区域blba中的位线260c可以电连接到在外围电路区域ps中提供页缓冲器35的电路元件320c。作为示例,位线260c连接至存储器单元区域cs中的上方键合金属271c和272c,并且上方键合金属271c和272c可以连接至连接到页缓冲器的电路元件320c的下方键合金属371c和372c。

75.在字线键合区域wlba中,字线230可以沿平行于第二基底210的上表面的第一方向d1延伸,并且可以连接到多个单元接触插塞240(例如,241到247)。字线230和单元接触插塞

240通过焊盘彼此连接,这些焊盘是由字线230中的至少一些沿第一方向d1以不同的长度延伸而提供的。第一金属层250b和第二金属层260b可以顺序连接到单元接触插塞240的顶部,单元接触插塞240连接到字线230。单元接触插塞240可以通过字线键合区域wlba中的存储器单元区域cs的上方键合金属271b和272b以及外围电路区域ps的下方键合金属371b和372b连接到外围电路区域ps。

76.单元接触插塞240可以电连接到在外围电路区域ps中提供行解码器33的电路元件320b。在一个实施例中,提供行解码器33的电路元件320b的工作电压可以与提供页缓冲器35的电路元件320c的工作电压不同。作为示例,提供页缓冲器35的电路元件320c的工作电压可以高于提供行解码器33的电路元件320b的工作电压。

77.公共源极线接触插塞280可以放置在外部焊盘键合区域pa中。公共源极线接触插塞280由诸如金属、金属化合物或多晶硅的导电材料形成,并且可以电连接至公共源极线220。第一金属层250a和第二金属层260a可以顺序堆叠在公共源极线接触插塞280的顶部。作为示例,可以将放置公共源极线接触塞280,第一金属层250a和第二金属层260a的区域定义为外部焊盘键合区域pa。

78.另一方面,可以将输入/输出(i/o)焊盘305以及第一和第二探测焊盘441和442放置在外部焊盘键合区域pa中。参考图7,可以在第一基底310的下方形成覆盖第一基底310的下表面的下方绝缘膜301,并且可以在下方绝缘膜301上形成第一i/o焊盘305。第一i/o焊盘305通过第一输入/输出接触插塞303附接到放置在外围电路区域ps中的多个电路元件320a,320b和/或320c中的至少一个,并且可以通过下方绝缘膜与第一基底310分离。此外,可以在第一i/o接触插塞303和第一基底310之间放置侧绝缘膜以将第一i/o接触插塞303和第一基底310彼此电分离。

79.参考图7,可以形成覆盖第二基底210的上表面210a的上方绝缘膜201,并且可以在上方绝缘膜201上放置第一和第二探测焊盘441和442。第一探测焊盘441和第二探测焊盘442中的每一个可以通过第一通孔导孔(thv)431和第二thv432中的每一个连接到放置在外围电路区域ps中的第一元件421和第二元件422,第一通孔导孔(thv)431和第二thv432穿透存储器单元区域cs。然而,thv与元件之间的互连关系仅仅是一个示例。替代地,第一元件421和第二thv432可以彼此连接,并且第二元件422和第一thv431可以彼此连接。

80.根据实施例,第二基底210和公共源极线220不需要放置在放置第一thv431的区域中。公共源极线220不需要放置在放置第二thv432的区域中。此外,第一探测焊盘441和第二探测焊盘442不需要在第三方向d3上与字线230重叠。参考图7,第一thv 431和第二thv432穿透存储器单元区域cs的层间绝缘膜215,并且可以分别连接到第一探测焊盘441和第二探测焊盘442的中的每一个。在图7中,尽管第二thv432穿透第二基底210,并且第一thv431不穿透第二基底210,但是thv和第二基底210之间的关系是一个示例,并且第一thv431和第二thv432都可以但不需要穿透第二基底210。

81.根据一个实施例,尽管可以选择性地形成第一i/o焊盘305并且仅将第一和第二探测焊盘441和442放置在第二基底210上,但是可以将另一个i/o焊盘放置在第一和第二探测焊盘441和442所在的位置。

82.最上面的金属层的金属图案作为虚设图案存在于包括在存储器单元区域cs和外围电路区域ps中的每一个中的外部焊盘键合区域pa和位线键合区域blba中的每一个中,或

者最上面的金属层可能是空的。

83.在外部焊盘键合区域pa中,半导体存储器设备101可以在外围电路区域ps的最上面的金属层上形成具有与存储器单元区域cs的上方金属图案272a基本相同形状的下方金属图案373a以对应于在存储器单元区域cs的最上面的金属层上形成的上方金属图案272a。在外围电路区域ps的最上面的金属层上形成的下方金属图案373a不需要连接到外围电路区域ps中的单独接触。类似地,在外部焊盘键合区域pa中,可以在单元区域cs的上金属层上形成具有与外围电路区域ps的下方金属图案相同形状的上方金属图案以对应于在外围电路区域ps的最上面的金属层上形成的下方金属图案。

84.下方键合金属371b和372b可以形成在字线键合区域wlba的第二金属层340b上。在字线键合区域wlba中,外围电路区域ps的下方键合金属371b和372b可以通过键合结构电连接到存储器单元区域cs的上方键合金属271b和272b。

85.此外,在位线键合区域blba中,可以在单元区域cs的最上面的金属层上形成具有与外围电路区域ps的下方金属图案352相同形状的上方金属图案292以对应于在外围电路区域ps的最上面的金属层上形成的下方金属图案352。不需要在形成在存储器单元区域cs的最上面的金属层上的上方金属图案292上形成接触。

86.图8为沿图6的线a-a’所取的用来说明本公开的实施例的半导体存储器设备10_2的剖面图;

87.在下文中,可以参考图8说明根据本公开的实施例的半导体存储器设备10_2。可以主要解释与图7所示的半导体存储器设备10_1的差异,并且可以省略基本上重复的描述。

88.当与图7的半导体存储器设备10_1比较时,放置在存储器单元区域cs和外围电路区域ps之间的下方键合金属371a到371c,372a到372c和373a以及外围电路区域ps的下方金属图案352,以及上方键合金属271a到271c和272a到272c以及存储器单元区域cs的上方金属图案292未被放置在图8的半导体存储器设备10_2中。

89.另外,公共源极线220,多条字线230(例如,231到238),多个单元接触插塞240(例如,241到247)和通道结构ch可以放置在外围电路区域ps的第二金属层340a、340b和340c与存储器单元区域cs的第二金属层260b和260c之间。

90.因此,基于第三方向d3,存储器单元区域cs的第一金属层250a、250b和250c以及第二金属层260b和260c可以放置在公共源极线220,多条字线230(例如,231到238),多个单元接触插塞240(例如,241到247)和通道结构ch的上方。

91.当与图7的半导体存储器设备10_1比较时,可以将水平半导体层221放置在公共源极线220的下方,而不是将第二基底210放置在公共源极线220的上方。

92.水平半导体层221可以包括下支撑半导体层和在下支撑半导体层上的公共源极板。水平半导体层221可以包括,例如,硅(si)、锗(ge)、硅锗(sige)、砷化镓(gaas)、砷化铟镓(ingaas)、砷化铝镓(algaas)中的至少一种,或其混合物。水平半导体层221可以具有晶体结构,其包括选自单晶,非晶和多晶中的至少一种。

93.此外,覆盖第二金属层260b和260c以及层间绝缘膜215的上方绝缘膜201可以放置在第二金属层260b和260c上。

94.图8中,尽管外围电路区域ps的第二金属层340b和340c与存储器单元区域cs的第二金属层260b和260c未彼此连接,但是外围电路区域ps的第二金属层340b和340c中的每一

个与存储器单元区域cs的第二金属层260b和260c中的每一个彼此电连接。

95.因此,行解码器33中包括的电路元件320b可以通过外围电路区域ps的第一和第二金属层330b和340b以及存储器单元区域cs的第一和第二金属层250b和260b电连接到多条字线230。类似地,页缓冲器35中包括的电路元件320c可以通过外围电路区域ps的第一和第二金属层330c和340c以及存储器单元区域cs的第一和第二金属层250c和260c电连接到信道结构ch。

96.参考图9和图11来说明根据本公开的实施例的累加电路41_1的操作。

97.参考图9至图11。为了便于说明,图9对多个当前状态信号402s中的第0至第三当前状态信号402_0s到402_3s的累加电路41_1的操作进行了说明。在下文中,也同样适用于与第四至第n当前状态信号402_4s到402_ns相关的累加电路41_1的操作。

98.如上所述,由于提供了多个当前状态信号402s,因此在输出第0当前状态信号402_0s之后,可以如图9所示顺序输出第n当前状态信号402_ns。作为示例,在t1时刻输出第0当前状态信号402_0s,并且当第0当前状态信号402_0s的输出在t2时刻一结束,就输出第一当前状态信号402_1s。当第一当前状态信号402_1s的输出在t3时刻一结束,就输出第二当前状态信号402_2s。当第二当前状态信号402_2s的输出在t4时刻一结束,就可以输出第三当前状态信号402_3s。

99.假设作为第一累加触发器413的输出的第一触发信号441s在t1时刻之前具有数值0的输出时,如果在t1时刻输出第0当前状态信号402_0s,则第一逻辑和计算器的输出在t1时刻从数值0变为1,并且响应于此,第一累加触发器413可以使第一触发信号441s等于第一互斥计算器415的输出。第一互斥计算器415可以接收vdd(例如,数值1)和数值0以输出数值1。因此,第一触发信号441s可以在t1时刻从数值0改变为数值1。

100.之后,尽管在t2时刻将第一逻辑和计算器411的输出从数值1改变为数值0,但是可以通过第一累加触发器413的操作来维持第一触发信号441s的数值1。

101.当在t3时刻输出第二当前状态信号402_2s时,第一逻辑和计算器411的输出在t3时刻从数值0改变为数值1,并且响应于此,第一累加触发器413可以使第一触发信号441s等于第一互斥计算器415的输出。第一互斥计算器415可以接收vdd(例如,数值1)和另一个数值1,并且可以输出数值0。因此,第一触发信号441s可以在t3时刻从数值1改变为数值0。

102.之后,尽管在t2时刻将第一逻辑和计算器411的输出从数值1改变为数值0,但是可以通过第一累加触发器413的操作来维持第一触发信号441s的数值1。

103.因为在t2和t4时刻的第二逻辑和计算器412,第二累加触发器414和第二互斥逻辑和计算器416的操作对应于在t1和t3时刻的第一逻辑和计算器411,第一累加触发器413以及第一互斥逻辑和计算器415的操作,上述操作说明可以同样适用于在t2和t4时刻的第二逻辑和计算器412,第二累加触发器414和第二互斥逻辑和计算器416的操作说明,并且可以省略基本上重复的描述。

104.因此,如果综合确定第一触发信号441s和第二触发信号442s的结果,有可能知道在t1和t2时刻之间输出了第0当前状态信号402_0s,在t2和t3时刻之间输出了第一当前状态信号402_1s,而且在t3和t4时刻之间输出了第二当前状态信号402_2s。

105.可以通过第一触发信号441s和第二触发信号442s来监测多个当前状态信号402s中的每一个的持续时间。第一触发信号441s和第二触发信号442s分别提供给第一探测焊盘

441和第二探测焊盘442,并且可以通过两个探测焊盘来监测有限状态机(fsm)40内部的状态信号。第一探测焊盘441和第二探测焊盘442可以对应于图7和图8的第一探测焊盘441和第二探测焊盘442。

106.因此,由于也可以将由每个探测焊盘连接的分配用于测试的thv的数量减少到两个,因此有可能增加分配用于有效地将电源和操作信号供应到半导体存储器设备10中的thv的数量和/或进一步使管芯规模最小化。

107.参考图12来说明根据本公开的实施例的累加电路41_2。

108.在下文中,可以参考图12说明根据本公开的实施例的累加电路41_2。可对如图5所示的累加电路41_1的差异进行主要解释,并且可以省略基本上重复的描述。

109.尽管在图5的当前状态电路402中,偶数触发器的输出端子和奇数触发器的输出端子连接到具有不同的逻辑和计算器的累加电路41_1,累加电路41_2的第三逻辑和计算器417可以连接到在当前状态电路402中连续的第k-1触发器402_k-1的输出端子和第k触发器402_k的输出端子(其中k是1或更大和n或更小的自然数)。

110.输入第k-1触发器402_k-1的第k-1当前状态信号401_k-1s作为缩减触发器402_k-1ff的d信号。缩减触发器402_k-1ff的输出与处于反相状态401_k-1s’的第k-1当前状态信号401_k-1s一起输入到缩减逻辑积计算器402_k-1and。

111.可以通过缩减触发器402_k-1ff和缩减逻辑积计算器402_k-1and将第k-1当前状态信号401_k-1s作为第k-1缩减状态信号402_k-1s'输入到第三逻辑和计算器417。

112.可以不经过缩减触发器和缩减逻辑积计算器而输入第k触发器402_k的第k当前状态信号401_ks。

113.第三累加触发器418和第三互斥逻辑和计算器419可以分别对应于图5的第一累加触发器413和第一互斥逻辑和计算器415。第三累加触发器418可以输出第三触发信号443s,并将其提供给第三探测焊盘433。

114.参考图13来说明根据本公开的实施例的累加电路41_2的操作。

115.参考图12和图13,如上述内容所述,由于提供了多个当前状态信号402s,因此在输出第k-1当前状态信号402_k-1s之后,可以如图11所示顺序输出第k当前状态信号402_ks。作为示例,在t5时刻输出第k-1当前状态信号402_k-1s,当在t7时刻第k-1当前状态信号402_k-1s的输出一结束,就可以输出第k当前状态信号402_ks。

116.作为第三累加触发器418的输出的第三触发信号443s在t5时刻之前具有数值0的输出,并且通过缩减触发器402_k-1ff和时钟信号clk的操作,缩减触发器402_k-1ff的输出具有数值0。

117.当在t5时刻输出第k-1当前状态信号402_k-1s时,缩减逻辑积计算器402_k-1and比缩减触发器402_k-1ff更早地操作,作为缩减触发器402_k-1ff的输出的反相值的数值1,以及第k-1当前状态信号402_k-1s的数值1被提供,并且在t5时刻具有数值1的第k-1缩减状态信号402_k-1s'可以输入到第三逻辑和计算器417。然而,当缩减触发器402_k-1ff工作并且缩减触发器402_k-1ff的输出变为数值1时,由于反相值变为0,所以此后,在t6时刻第k-1缩减状态信号402_k-1s’的值可以为0。

118.之后,由于缩减触发器402_k-1ff的输出从t6时刻到t7时刻保持在数值1,因此第k-1缩减状态信号402_k-1s'的输出持续时间d_402_k-1s'可以小于第k-1当前状态信号

402_k-1s的输出持续时间,并且可以小于或等于时钟信号clk的输出持续时间t_clk。此外,第k-1缩减状态信号402_k-1s'的输出持续时间d_402_k-1s'可以小于第k当前状态信号402_ks的输出持续时间d_402_ks。

119.因为第k-1缩减状态信号402_k-1s'的输出持续时间d_402_k-1s'可以通过缩减触发器402_k-1ff和缩减逻辑积计算器402_k-1and之间的操作速度差从t5保持到t6时刻,在第k-1缩减状态信号402_k-1s'的输出与第k当前状态信号402_ks的输出之间可能出现从t6到t7的时间容限。

120.由于在从t6到t7时刻的时间容限期间第三逻辑和计算器417的输出可以从数值1改变为数值0,所以此后,第三逻辑和计算器417的输出通过第k当前状态信号402_ks在t7时刻从数值0改变为数值1,并且第三累加触发器418可以工作。

121.因此,即使连续输出第k-1当前状态信号402_k-1s和第k当前状态信号402_ks,也可以将它们输入到相同的第三逻辑和计算器417。

122.基于此,根据实施例,当使多个当前状态信号402s的偶数信号或奇数信号经过累加电路41_2中的缩减触发器和缩减逻辑和计算器时,本公开的累加电路41_2的操作可以由一个第三逻辑和计算器417,第三累加触发器418和第三互斥逻辑和计算器419通过时间容限来执行。因此,第三累加触发器418可以通过第三触发信号来监测第三探测焊盘443上的多个当前状态信号402s中的每一个的持续时间。因此,可以有一个分配用于测试的thv。

123.然而,本发明构思的实施例不限于本文阐述的实施例。通过参考以下权利要求,基于本公开的范围和精神的上述和其他实施例对于相关领域的普通技术人员而言将变得更加显而易见。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。