1.本发明涉及一种动态随机存取存储器,尤其涉及一种具有强化存取暨回 复架构的动态随机存取存储器。

背景技术:

2.现有技术中,最广泛使用的动态随机存取存储器(dynamic random accessmemory,dram)单元(cell)包含一存取晶体管和一储存电容,其中存取晶体 管的源极连接储存电容,而存取晶体管的漏极则连接一位线。位线耦接第一 级传感放大器,而第一级传感放大器从动态随机存取存储器单元所读出 (read out)的信号通过列开关(column switches)后,再传送至一第二级传感放 大器,其中第二级传感放大器连接输入/输出线(也就是数据线)。dram在写 入操作(write operation)期间,由输入/输出缓冲器所驱动的信号会被稳定在 数据线,而输入/输出缓冲器驱动的信号会进一步通过第一级传感放大器后, 再过存取晶体管写入至储存电容。存取晶体管进行激活模式(active mode,也 就是对应述存取晶体管已开启稳定)后,存取晶体管可进行储存电容的读取操 作(read operation)或储存电容的写入操作(write operation)。而在存取晶体 管的非激活模式(inactive mode,也就是所述存取晶体管已开启关闭)下,存取 晶体管则可避免储存电容所储存的数据遗失。

3.在现有技术中,存取晶体管被设计具有一高的阈值电压,尽量将通过存 取晶体管的漏电流最小化,但随之而来的缺点是当存取晶体管开启时,存取 晶体管的性能降低。因此,连接存取晶体管的栅极的字线必须被升压或连接 至一高的电压vpp(通常来自一字线驱动电路)以允许存取晶体管具有高驱动 能力而将信号写入至所述储存电容,其中电压vpp是通过所述字线驱动电路 加载至字线或存取晶体管的栅极。因为电压vpp是施加在存取晶体管的高压, 所以存取晶体管的栅极的电介质材料(例如,一氧化层或一高电介常数材料) 必须比应用至动态随机存取存储器的其他外围电路(例如命令译码器,地址译 码器和其他输入/输出电路等)的栅极的电介质材料还要厚。因此,存取晶体管 的设计面临不是只能维持高性能、就是只能维持高可靠性的挑战,且须在存 取晶体管的可靠性和性能之间进行了艰难的权衡取舍。然而在现有技术中, 存取晶体管的设计更专注于达成存取晶体管的高可靠性,却同时必须牺牲存 取晶体管的性能。

4.关于前述既有的存取晶体管设计,存取晶体管必须具有高阈值电压以降 低存取晶体管的漏电流(其中降低存取晶体管的漏电流有助于延长储存电容 中所储存的电荷的保留时间),具有厚的栅极电介质材料则可承受高的字线电 压(例如电压vpp),以及牺牲所述存取晶体管的性能。因此,通过存取晶体 管对储存电容写入一高电平信号(也就是信号“one”,其中信号“one”通 常对应如图1a所示的电压vccsa)将会花较长的时间达到或无法完全达到 信号“one”所对应的电压vccsa。也就是说,将信号“one”所对应的电 压vccsa完全写入至所述储存电容所耗费的写入时间(write time)将较长。

5.另外,请再参照图1a,其中图1a是说明动态随机存取存储器单元最常 用的设计的

示意图,其中动态随机存取存储器单元包含存取晶体管11和储存 电容12。存取晶体管11的栅极耦接于字线wl,传感放大器20通过位线bl 耦接于存取晶体管11,其中传感放大器20可由p型金属氧化物半导体晶体 管p1、p2和n型金属氧化物半导体晶体管n1、n2所组成,且p型金属氧 化物半导体晶体管p1、p2和n型金属氧化物半导体晶体管n1、pn2的耦接 关系可参照图1a,在此不再赘述。动态随机存取存储器单元在写入操作 (write operation)期间利用存取晶体管11做为一开关以控制电荷通过位线 bl储存至储存电容12,或是在读取操作(read operation)期间传送储存电容 12所储存的电荷至位线bl,其中多个动态随机存取存储器单元分别连接位 线bl。例如,传感放大器20在读出操作期间通过放大动态随机存取存储器 单元传送至位线bl的信号以闩锁信号“one”(其中信号“one”可例如为 1.2v,信号“one”通常为传感放大器20所提供的电压vccsa)或信号“zero

”ꢀ

(其中信号“zero”可例如为0v,信号“zero”通常为传感放大器20所 提供的电压vss),或者在写入操作期间,储送信号“one”或信号“zero

”ꢀ

至传感放大器20,以储存正确的信号至动态随机存取存储器单元的储存电容 12。

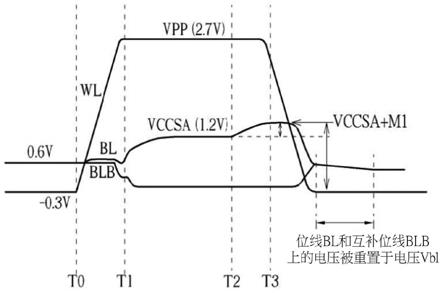

6.请参照图1b,图1b是说明动态随机存取存储器单元在存取(读取或写入) 操作期间的相关信号的波形的示意图。例如,动态随机存取存储器单元在 25nm制程的设计下,通常具有下列与动态随机存取存储器单元数组的相关参 数∶位线bl上的信号“one”的电压为1.2v,字线wl上的开启电压为 2.7v(也就是电压vpp为2.7v)以及字线wl上的等待(standby)电压约为-0.3v, 所述阈值电压介于0.7v和0.9v之间,存取晶体管11的栅极的电介质材料必 须承受2.7v的电压强度,其中在老化应力(burn-in stress)的条件下,存取晶体 管11的栅极的电介质材料更必须承受3.4v的电压强度以维持可接受的可靠 性裕度(reliability margin),以及必须采用厚的存取晶体管11的栅极的电介质 材料,其中厚的存取晶体管11的栅极的电介质材料会牺牲存取晶体管11的 性能。

7.如图1b所示,储存电容12在一开始是处于一等待模式(standby made)或 非激活模式(也就是说此时存取晶体管11完全关闭),且字线wl上的电压为

ꢀ-

0.3v(等待电压)。位线bl和互补位线blb上的电压被等化(equalized)在电压 vccsa的一半(即0.6v)。当储存电容12要进入激活模式(也就是存取晶体管 11以完全开启)时,字线wl上的电压先从所述等待电压(-0.3v)被提升至电压 vpp(例如2.7v),其中电压vpp大于电压vccsa(1.2v)和存取晶体管11的 阈值电压vt(可为0.7v或0.8v)的总和,以在存取晶体管11的栅源极电压(例 如2.7v-1.2v-0.8v=0.7v)上提供足够大的驱动力。另外,因为存取晶体管 11开启,所以位线bl可耦接储存电容12。如图1b所示,在存取(读出或写 入)操作期间,字线wl上的电压持续维持在电压vpp,且在存取操作期间之 后是伴随着一回复阶段(restore phase),或者是预充电阶段(prechargephase)。在回复阶段,传感放大器20将根据储存电容12所储存的信号“one

”ꢀ

或信号“zero”对储存电容12再充电。经过回复阶段,字线wl上的电压 将从电压vpp下拉至所述等待电压(-0.3v),导致存取晶体管11再次处于所 述非激活模式。

8.综上所述,电压vpp所造成的高压应力将使得存取晶体管11的栅极被 设计成具有较厚的电介质材料,其中存取晶体管11的栅极的电介质材料比应 用在动态随机存取存储器单元的外围电路中的晶体管的栅极的电介质材料还 要厚,然而存取晶体管11的栅极所具有较厚的电介质材料将降低存取晶体管 11的性能(例如存取晶体管11的短信道效应更严重,存取晶体管11的开启/ 关闭电流的比值更小,以及衡量存取晶体管11的开启/关闭的

回应能力的摆 幅斜率(swing slope)变差等)。另外,虽然阈值电压是比应用在动态随机存取 存储器单元的外围电路中的晶体管的阈值电压还要高,但在等待模式或非激 活模式期间,通过存取晶体管11的漏电流仍然很大到可降低储存电容12中 用于传感所需的储存电荷。尤其是在12nm或7nm的鳍式场效晶体管(finfield-effect transistor,finfet)制程技术中,当电压vccsa较低(例如0.6~0.8v) 时,存取晶体管11在所述等待模式或所述非激活模式期间的漏电流会变得更 更严重。

技术实现要素:

9.本发明的第一实施例公开一种动态随机存取存储器(dynamic randomaccess memory,dram)。所述动态随机存取存储器包含第一维持电压源, 其中第一维持电压源用于产生一第一电压,且所述第一电压高于应用在动态 随机存取存储器中一高电平信号或one信号的电压。而动态随机存取存储器 进一步包含一动态随机存取存储器单元,其中动态随机存取存储器单元包含 一存取晶体管和一储存电容,且所述第一电压是于存取晶体管关闭之前被储 存在动态随机存取存储器单元。

10.在所述第一实施例中,所述动态随机存取存储器另包含一字线,其中所 述字线耦接于所述存取晶体管的栅极,所述字线于一第一时间区间与一第二 时间区间被选择开启所述存取晶体管,所述第二时间区间位于所述第一时间 区间之后,以及在所述第二时间区间中所述第一电压被储存在所述动态随机 存取存储器单元。所述动态随机存取存储器单元在所述第一时间区间是可被 存取的。所述动态随机存取存储器另包含一传感放大器,其中所述传感放大 器通过一位线电连接所述动态随机存取存储器单元,所述第一维持电压源在 所述第二时间区间连接于所述传感放大器,以及所述第一电压通过所述传感 放大器和所述位线提供给所述动态随机存取存储器单元。另外,所述动态随 机存取存储器另包含一电压源,其中所述电压源在所述第一时间区间连接于 所述传感放大器,在所述第二时间区间与所述传感放大器断开,以及所述电 压源所提供的供电电压等于所述高电平信号的电压。

11.本发明的第二实施例公开一种动态随机存取存储器。所述动态随机存取 存储器包含一动态随机存取存储器单元和一传感放大器,其中所述传感放大 器通过一位线电连接所述动态随机存取存储器单元。所述动态随机存取存储 器单元包含一存取晶体管和一电容。一第一维持电压源及/或一第二维持电压 源选择性地耦接于所述传感放大器,其中所述第一维持电压源产生一第一电 压,其中所述第一维持电压源产生一第一电压以及所述第二维持电压源产生 一第二电压,其中所述第一电压高于应用在所述动态随机存取存储器中一高 电平信号的电压,以及所述第二电压低于应用在所述动态随机存取存储器中 一低电平信号的电压。

12.在所述第二实施例中,所述第一电压或所述第二电压于所述存取晶体管 关闭之前被储存在所述动态随机存取存储器单元。所述动态随机存取存储器 另包含一字线,其中所述字线耦接于所述存取晶体管的栅极,所述字线于一 第一时间区间与一第二时间区间被选择以开启所述存取晶体管,所述第二时 间区间位于所述第一时间区间之后,所述第一电压或所述第二电压在所述第 二时间区间内被储存在所述动态随机存取存储器单元,以及所述动态随机存 取存储器单元在所述第一时间区间是可被存取的。另外,所述第二维持

电压 源在所述第二时间区间连接于所述传感放大器,以及所述第二电压通过所述 传感放大器和所述位线提供给所述动态随机存取存储器单元。另外,动态随 机存取存储器另包含一电压源,其中所述电压源在所述第一时间区间连接于 所述传感放大器,在所述第二时间区间与所述传感放大器断开,以及所述电 压源所提供的供电电压等于所述低电平信号的电压。

13.本发明的第三实施例公开一种动态随机存取存储器。所述动态随机存取 存储器包含一动态随机存取存储器单元和一字线。所述动态随机存取存储器 单元包含一存取晶体管和一储存电容,所述字线耦接于所述存取晶体管的栅 极。在所述字线被选择以开启所述存取晶体管以及所述字线不被选择以关闭 所述存取晶体管之间,一第一电压或一第二电压被储存在所述动态随机存取 存储器单元,其中所述第一电压高于应用在所述动态随机存取存储器中一高 电平信号的电压,以及所述第二电压低于应用在所述动态随机存取存储器中 一低电平信号的电压。另外,所述动态随机存取存储器另包含一传感放大器, 其中所述传感放大器电连接所述动态随机存取存储器单元,以及产生所述第 一电压的一第一维持电压源以及产生所述第二电压的一第二维持电压源选择 性地耦接于所述传感放大器。

14.本发明的另一实施例公开一种动态随机存取存储器。所述动态随机存取 存储器包含一第一动态随机存取存储器单元组和一第二动态随机存取存储器 单元组,其中每一动态随机存取存储器单元包含一存取晶体管和一储存电容。 所述动态随机存取存储器另包含一第一字线和一第二字线,其中所述第一字 线耦接于所述第一动态随机存取存储器单元组内的每一动态随机存取存储器 单元的存取晶体管的栅极,以及所述第二字线耦接于所述第二动态随机存取 存储器单元组内的每一动态随机存取存储器单元的存取晶体管的栅极。在所 述第一字线被选择以开启所述第一动态随机存取存储器单元组内的每一动态 随机存取存储器单元的存取晶体管以及所述第一字线不被选择以关闭所述第 一动态随机存取存储器单元组内的每一动态随机存取存储器单元的存取晶体 管之间,一第一电压或一第二电压被储存在所述第一动态随机存取存储器单 元组内的每一动态随机存取存储器单元每一动态随机存取存储器单元,其中 所述第一电压高于应用在所述动态随机存取存储器中一高电平信号的电压, 以及所述第二电压低于应用在所述动态随机存取存储器中一低电平信号的电 压。

15.在另一实施例中,所述动态随机存取存储器另包含一第一传感放大器组 和一第二传感放大器组,其中所述第一传感放大器组电连接所述第一动态随 机存取存储器单元组,所述第二传感放大器组电连接所述第二动态随机存取 存储器单元组,且所述第一电压或所述第二电压通过所述第一传感放大器组 提供给所述第一动态随机存取存储器单元组内的每一动态随机存取存储器单 元。另外,当所述第一字线被选择时,所述第二字线不被选择以及所述第二 传感放大器组是耦接于一第一电压源和一第二电压源,其中所述第一电压源 所提供的电压等于所述高电平信号的电压,以及所述第二电压源所提供的电 压等于所述低电平信号的电压。

16.本发明公开一种动态随机存取存储器,所述动态随机存取存储器是在动 态随机存取存储器单元内的存取晶体管关闭(或耦接于所述动态随机存取存 储器单元的字线关闭)之前,恢复或储存高于应用在动态随机存取存储器中一 高电平信号的第一电压至所述

动态随机存取存储器单元。同样地,动态随机 存取存储器是在所述动态随机存取存储器单元内的存取晶体管关闭(或耦接 于所述动态随机存取存储器单元的字线关闭)之前,可恢复或储存低于应用在 所述动态随机存取存储器中一低电平信号的第二电压至所述动态随机存取存 储器单元。因此,在所述动态随机存取存储器单元内的存取晶体管关闭后, 即使仍有漏电流通过所述动态随机存取存储器单元内的存取晶体管,但所述 动态随机存取存储器单元内的储存电容所储存的电荷仍可比现有的动态随机 存取存储器的架构维持更长的一段时间。

附图说明

17.图1a是说明所述动态随机存取存储器单元最常用的设计的示意图。

18.图1b是说明所述动态随机存取存储器单元在存取(读出或写入)操作期间的相 关信号的波形的示意图。

19.图2是说明本发明的第一实施例所公开的所述动态随机存取存储器单元在存 取(读出或写入)操作期间的相关信号的波形的示意图。

20.图3a是说明传感放大器选择性地耦接于一第一维持电压源的示意图。

21.图3b是说明传感放大器选择性地耦接于所述第二维持电压源的示意图

22.图4是说明本发明的第二实施例所公开的所述动态随机存取存储器单元在存 取(读出或写入)操作期间的相关信号的波形的示意图。

23.图5是本发明的第三实施例所公开的用于预充电操作的电路和功能框图的示 意图

24.图6是说明耦接于所述第一动态随机存取存储器单元的传感放大器在所述预 充电操作中的示意图。

25.图7是说明本发明另一实施例的dram单元于操作期间的相关信号波形。

26.图8a是说明本发明另一实施例的dram单元于操作期间的相关信号波形。

27.图8b是说明本发明另一实施例的dram单元于操作期间的相关信号波形。

28.图8c是说明本发明另一实施例的dram单元于操作期间的相关信号波形。

29.图8d是说明本发明另一实施例的dram单元于操作期间的相关信号波形。

30.图9是说明本发明dram单元于操作期间的不同指令加压周期与位线信号之 间的关系。

31.其中,附图标记说明如下:

32.11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存取晶体管

33.12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

储存电容

34.13、14、23、24

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

开关

35.20、41、42

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

传感放大器

36.30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预充电脉冲信号

37.bl、blb、bl1、bl9、bl1b、bl9b

ꢀꢀꢀ

位线

38.lslp、lsln

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

节点

39.n3、n4、n7、n8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

n型金属氧化物半导体晶体管

40.p1、p2、p5、p6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

p型金属氧化物半导体晶体管

41.sn1、n9

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

储存节点

42.sec

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储区

43.t0、t1、t2、t3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间

44.vccsa、vss、vpp1、m1、vbl、

ꢀꢀꢀꢀ

电压

45.m2、k

46.vpl

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

共同电压

47.vhsa

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三电压

48.wl、wl100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

字线

具体实施方式

49.本发明公开一种具有强化存取暨回复架构的动态随机存取存储器 (dynamic random access memory,dram),其中维持电压源在所述动态随机 存取存储器单元所包含的存取晶体管关闭之前,电连接所述动态随机存取存 储器单元所包含的储存电容,其中所述维持电压源所提供的电压是高于 dram中的高电平信号(即信号“one”)电压值,或小于低电平信号(即信号

ꢀ“

zero”)电压值。又于动态随机存取存储器进行其他特定操作时(例如进行 自动预充电阶段(auto-precharge phase),回复阶段(restore phase),刷新阶段 (refresh phase),以及预充电阶段),也将使动态随机存取存储器单元中存取晶 体管被开启,因此,在存取晶体管开启期间,所述维持电压源将电连接至储 存电容,所以即使在存取晶体管关闭后仍有漏电流通过存取晶体管,但储存 电容所储存的电荷仍可比现有的动态随机存取存储器的架构维持更长的一段 时间。

50.本发明的第一实施例∶

51.图2是说明第一实施例的动态随机存取存储器单元在存取(读出或写入) 操作期间的相关信号的波形的示意图,其中动态随机存取存储器单元可参照 图1a。如图2所示,所述动态随机存取存储器在一开始是处于一等待模式 (standby mode)或一非激活模式(inactive mode),且字线wl被偏压在一等待电 压(-0.3v)以完全关闭存取晶体管11。在所述第一实施例中,电压vccsa为 1.2v,电压vss为0v,信号“one”(也就是一高电平信号)为1.2v,以及 信号“zero”为0v(也就是一低电平信号,且等于地端所具有的电位)。另 外,在所述第一实施例中,位线bl和位线blb上的电压被均等在0.6v,也 就是说位线bl和位线blb上的电压介于信号“one”(1.2v)和信号“zero

”ꢀ

(0v)之间。

52.在一时间t0,字线wl上的电压将从等待电压(-0.3v)提升至电压 vpp(2.7v)以开启存取晶体管11,其中电压vpp(2.7v)是远大于电压 vccsa(1.2v)和存取晶体管11的阈值电压vt(0.8v)的总和,也就是说电压 vpp(2.7v)可为开启的存取晶体管11提供足够的驱动力以将信号“one”或 信号“zero”传送到位线bl和位线blb。然后传感放大器20被启动以放 大位线bl和位线blb上的信号直到位线bl和位线blb上的信号被发展到 一定大小,其中传感放大器20可为一交叉耦合传感放大器。在时间t1之后 一段时间,可执行读取操作(通过传感放大器20放大位线bl和位线blb上 从动态随机存取存储器单元所读出的信号),或所述写入操作(外界写入信号

ꢀ“

one”或信号“zero”至传感放大器20以储存正确的信号至动态随机存 取存储器单元的储存电容12)。在存取操作期间中,一电压源通过开启一开关 14(如图3a所示)电连接或耦接传感放大器20以耦接于储存电容12。所述电 压源可提供电压“zero”时,在所述回复阶段,第二电压vss-m2(-0.6v)是从所述第二维持 电压源通过传感放大器20和位线bl传送并储存至储存电容12。也就是说如 图2所示,在时间t3后完全关闭存取晶体管11前(其中当关闭存取晶体管11 时,字线wl上的电压将从电压vpp逐渐被下拉至字线wl处于所述等待模 式的等待电压),储存电容12可由第二维持电压源提供第二电压vss-m2(也 就是说在时间t3关闭存取晶体管11前,储存电容12是储存第二电压 vss-m2),其中第二电压vss-m2低于信号“zero”(也就是所述低电平信 号)。在本发明的一实施例中,在关闭存取晶体管11后或在所述回复阶段后, 第二维持电压源可断开传感放大器20。

55.另外,在本发明的另一实施例中,在回复阶段,第一维持电压源和所述 第二维持电压源都耦接于所述动态随机存取存储器单元的储存电容12。因此, 在字线wl上的电压从电压vpp被下拉至字线wl处于所述等待模式的等待 电压之前,当储存电容12最初是储存信号“one”时,第一电压 vccsa m1(1.2v 0.6v)是从所述第一维持电压源通过传感放大器20传送并 储存至储存电容12;或当储存电容12最初是储存信号“zero”时,第二电 压vss-m2(-0.6v)是从所述第二维持电压源通过传感放大器20传送并储存至 储存电容12。

56.本发明的第二实施例∶

57.为了减少漏电流以保持储存电容12所储存的电荷不会通过存取晶体管 11被泄漏出,通常存取晶体管11被设计成具有非常高的阈值电压。当电压 vccsa降至0.6v时,在所述动态随机存取存储器的设计中,7奈米或5奈 米工艺的tri-gate晶体管或鳍式场效晶体管将被应用至所述动态随机存取存 储器单元的外围电路,其中应用至所述外围电路的晶体管的阈值电压将会对 应地缩小,例如应用至所述外围电路的晶体管的阈值电压被降至0.3v。然而 在本发明的第二实施例中,存取晶体管11的阈值电压可根据上述减少漏电流 的概念被有意地提高至0.5v-0.6v。因此,从储存电容12流出的漏电流可被 大幅地减少至少3~4个数量级(如果用于衡量漏电流的s因子为68mv/数量级 (decade)且存取晶体管11的阈值电压被提高至0.6v,则从储存电容12流出的 漏电流将比应用至所述外围电路的tri-gate晶体管的漏电流低4个数量级;如 果存取晶体管11的阈值电压提高至0.5v,则从储存电容12流出的漏电流将 比应用至所述外围电路的tri-gate晶体管的漏电流降低2~3个数量级)。因此, 在本发明的第二实施例中,存取晶体管11的阈值电压将被提高到接近电压 vccsa或至少超过0.6v的80%。另外,在本发明的第二实施例中,存取晶 体管11(例如鳍式场效晶体管或tri-gate晶体管)的栅极的电介质材料的厚度仍 然和应用至所述外围电路的晶体管的栅极的电介质材料的厚度相同或几乎相 同,所以存取晶体管11使用tri-gate结构的高性能的优点仍可被维持住。

58.图4是说明所述第二实施例所公开的所述动态随机存取存储器单元在存 取(读出或写入)操作期间的相关信号的波形的示意图,其中在第二实施例中, 信号“one”为0.6v以及信号“zero”为0v(也就是所述地端所具有的电 位)。在回复阶段,一第一维持电压源耦接于所述动态随机存取存储器单元的 储存电容12。所述第一维持电压源可提供高于电压vccsa(0.6v)或信号

ꢀ“

one”(0.6v)的一第一电压vccsa k,其中所述第一维持电压源可通过电 连接或耦接传感放大器20以耦接储存电容12,且电压k为一正电压。在本 发明的一实施例中,电压k可介于电压vccsa(0.6v)的1/3和电压 vccsa(0.6v)的2/3之间,例如0.3v或0.4v。另外,在本发明的另一实施例 中,电压k也可以是0.05v~0.4v之间的任一值,如0.05v,0.1v,0.2v,0.3v 或0.4v等。因此,当储存电容12最初是储存信号“one”(0.6v)时,在

所述 回复阶段,第一电压vccsa k(0.6v 0.4v)是提供给储存电容12。也就是说 如图4所示,在时间t3后完全关闭存取晶体管11前(其中当关闭存取晶体管 11时,字线wl上的电压将从电压vpp被下拉至字线wl处于所述等待模式 的等待电压),储存电容12可由第一维持电油压源提供第一电压vccsa k, 其中第一电压vccsa k高于信号“one”(0.6v)。因此,当储存电容12最 初是储存信号“one”(0.6v)时,在字线wl上的电压被上拉至电压vpp后 且在被下拉至所述等待电压前,第一电压vccsa k(1v)可被储存至储存电 容12。另外,在本发明的一实施例中,在所述回复阶段后,位线bl和位线 blb可耦接于用以提供电压vbl的所述位线电压源,所以位线bl和位线blb 上的电压在所述回复阶段后将被重置于电压vbl(如图4所示)。另外,如前面 所述,当储存电容12最初是储存信号“zero”时,在字线wl上的电压将 从电压vpp被下拉至字线wl处于所述等待模式的等待电压前,所述第二维 持电压源所提供的第二电压可被储存至储存电容12,其中所述第二维持电压 源所提供的第二电压是低于储存信号“zero”,例如-0.4v。另外,在本发明 的另一实施例中,所述第二电压也可以是-0.05v~-0.4v之间的任一值,如

ꢀ-

0.05v,-0.1v,-0.2v,或-0.3v等。

59.本发明的第三实施例∶

60.图5是本发明的第三实施例所公开的用于预充电(precharge)操作的电路 和功能框图的示意图,其中在所述第三实施例中,电压vccsa为0.6v以及 电压vss为0v(也就是所述地端的电位)。在预充电操作中,所有在存储区 5(sec 5)中连接被选择的字线的动态随机存取存储器单元(之后称为第一动态 随机存取存储器单元)将被预充电,以及在其他在存储区(例如sec4,sec6等) 连接未被选择的字线的动态随机存取存储器单元(之后称为第二动态随机存 取存储器单元)将处于空闲状态(idle state)。

61.传感放大器41、42(耦接于所述第一动态随机存取存储器单元)将根据一 预充电脉冲信号30连接一第三维持电压源,其中所述第三维持电压源可提供 一第三电压vhsa(0.6v k),所以可以加速恢复所述第一动态随机存取存储 器单元在预充电阶段时的信号。第三电压vhsa高于电压vccsa(0.6v)约几 百毫伏(mv),例如0.3v或0.4v。另外,在被选择的字线关闭之前(也就是所 述第一动态随机存取存储器单元内的存取晶体管完全关闭之前),第三电压 vhsa(0.6v 0.4v)是高于随后要储存至所述第一动态随机存取存储器单元内 的储存电容的信号“one”。另一方面,第二动态随机存取存储器单元仍然接 收电压vccsa。

62.另外,请参照图6,图6是说明耦接于所述第一动态随机存取存储器单 元的传感放大器在所述预充电操作中的示意图,其中用于辅助说明图6的符 号的说明如下∶

63.lslp∶连接所述第一动态随机存取存储器单元的传感放大器中用于接 收高电压的节点;

64.lsln∶连接所述第一动态随机存取存储器单元的传感放大器中用于接 收低电压的节点;

65.vpl∶电路板上的共同电压;

66.sn∶储存节点;

67.wl∶字线;

68.bl∶位线;

69.vsg1,2∶连接所述第一动态随机存取存储器单元的传感放大器中的p型 金属氧化

物半导体晶体管p1、p2的源栅极电压;

70.vgs3,4∶连接所述第一动态随机存取存储器单元的传感放大器中的n型 金属氧化物半导体晶体管n3、n4的栅源极电压;

71.vsg5,6∶连接所述第一动态随机存取存储器单元的传感放大器中的p型 金属氧化物半导体晶体管p5、p6的源栅极电压;

72.vgs7,8∶连接所述第一动态随机存取存储器单元的传感放大器中的n型 金属氧化物半导体晶体管n7、n8的栅源极电压。

73.请再参照图6,字线wl100耦接于多个储存节点,例如储存节点sn1、 sn9。当信号“one”(0.6v)储存在连接字线wl100的储存节点sn1时,且 在预充电指令被开启以及在字线wl100被选择(也就是字线wl100开启)后, 节点lslp接收第三电压vhsa(1.0v)以及节点lsln上的电压仍维持0v, 也就是节点lslp上的电压从0.6v被提升至1.0v。因此,p型金属氧化物半 导体晶体管p1关闭以及源栅极电压vsg1为0v。同样地,p型金属氧化物半 导体晶体管p2开启以及源栅极电压vsg2从0.6v被提升至1.0v,以及1.0v 的电压通过位线bl1被完全充电至储存节点sn1。此时,n型金属氧化物半 导体晶体管n3开启以及栅源极电压vgs3也从0.6v被提升至1.0v。另外, n型金属氧化物半导体晶体管n4关闭以及栅源极电压vgs4为0v。

74.当信号“zero”(0v)储存在连接字线wl100的储存节点sn9时,且在 所述预充电指令被开启以及在字线wl100被选择后,节点lslp接收第三电 压vhsa(1.0v)以及节点lsln上的电压仍维持0v。因此,p型金属氧化物 半导体晶体管p5开启以及源栅极电压vsg5从0.6v被提升至1.0v。同样地, p型金属氧化物半导体晶体管p6关闭以及源栅极电压vsg6为0v。此时,n 型金属氧化物半导体晶体管n7关闭以及栅源极电压vgs7为0v。另外,n 型金属氧化物半导体晶体管n8开启以及栅源极电压vgs8从0.6v被提升至 1.0v,以及储存节点sn9的电压通过位线bl9被强力地恢复至0v。当然, 如前所述,在所述预充电操作中,当图6所示的储存电容最初是储存信号

ꢀ“

zero”时,节点lsln可接收其他维持电压源所提供的一电压 vlsn(0v-k),其中电压vlsn是低于信号“zero”,以及例如电压vlsn 可为-0.4v。然后,在所述预充电操作中,储存节点sn9的电压通过位线bl9 被强力地恢复至-0.4v。

75.在本发明的另一实施例中,只要在耦接于所述动态随机存取存储器单元 的字线完全关闭之前(或进行关闭期间),提供所述第一电压(高于信号“one”) 的所述第一维持电压源耦接于所述传感放大器(或所述动态随机存取存储器 单元),则耦接所述第一维持电压源至所述传感放大器(或所述动态随机存取存 储器单元)的概念也可被应用至所述刷新阶段(refresh phase)或其他操作(例如 具有自动预充电阶段(auto-precharge phase)的存取操作(read/write))。同样 地,只要在耦接于所述动态随机存取存储器单元的字线完全关闭之前(或进行 关闭期间),提供所述第二电压(低于信号“zero”)的所述第二维持电压源耦 接于所述传感放大器(或所述动态随机存取存储器单元),则耦接所述第二维 持电压源至所述传感放大器(或所述动态随机存取存储器单元)的概念也可被 应用至所述刷新阶段或其他操作。

76.本发明的第四实施例∶

77.图7是说明本发明关于dram单元操作过程的相关信号波形的另一实施 例。一开始当dram单元处于等待状态时,字线wl被施加负偏压以完全关 闭dram单元的存取晶体管。在本实施例中,vccsa可被设置为1.1v而 vss被设置为0v,因此信号one的电位为1.1v,信号

zero的电位为 0v(gnd);而位线(bl)和互补位线(blb)进行等化处理,使两者电位在 vccsa=1.1v的信号one电位和vss=0v的信号zero电位之间。在t0之 后,字线电压逐渐上升至一高电压值以便开启drram单元的存取晶体管。 在t1和t2之间的期间可对dram单元执行一个激活(active)指令,而在激 活指令期间,并将相应的第一维持电压源(vccsa m1)连接到感应放大器(如 图3a所示,可将开关14关闭并将开关13打开)。因此,在激活命令执行期 间,位线的信号至少被加压到vccsa m1一段时间。

78.同时,伴随着激活命令的行地址(row address)信息也会被输入到dram 中,以选择合适的字线。因此,也可在dram接收到行地址信息后,相应的 第一维持电压源(vccsa m1)连接到感应放大器。因此,相应的第一维持电 压源(vccsa m1)可以根据以下的一连接到感测放大器:(1)激活命令;(2) 行地址信息;(3)激活命令和行地址信息的组合。因此,在执行激活命令的过 程中,位线的信号将至少被加压(提升或踢升”kick”)至vccsa m1的电平, 或者在dram接收到行地址信息后,位线的信号将至少加压或踢升至 vccsa m1。这种对位线信号的加压或踢升可以命名为激活(active)-行(row) 踢,或简称为a-r kick。

79.在激活命令执行完毕后,常规电压源vccsa则连接到感应放大器(可参 考图3a,即将开关13关闭并将开关14打开),则位线的信号即回到vccsa 的电平。利用这种加压或提升位线的信号电压电平方式,将可加快位线信号 的感应速度。

80.同样,在t2时间后的restore操作时间(或进行预充电时),本实施例 仍在restore阶段将第一维持电压源vccsa m1(或比vccsa高的不同维 持电压)耦合到dram单元的电容器上。也就是说,在restore(或预充电) 阶段,原vccsa电压源与感测放大器断开(例如,通过关闭图3a中所示的 开关14),而第一维持电压源vccsa m1将连接到感测放大器(例如,通过打 开图3a中所示的开关13)。位线的信号将至少被加压或提升到vccsa m1。 因此,在字线wl电位被拉低至负电位以完全关闭dram单元的存取晶体管 之前,dram单元的存储电容被供给比常规信号one(即vccsa电位)更高 的第一维持电压源的vccsa m1电位,与传统dram结构相比,即使dram 单元有漏电流通过存取晶体管,dram单元的存储电容也能维持更长的时间。

81.本发明的第五实施例∶

82.图8a是说明本发明关于dram单元操作过程的相关信号波形的又一实 施例。类似于前述的第四实施例,本实施例可在t1和t2之间的期间,在对 dram单元执行一个激活指令。如前述,此时可将相应的第一维持电压源 (vccsa m1)连接到感应放大器,因此在激活命令期间(或dram接收到行 地址信息后),位线的信号将至少被加压或踢升到vccsa m1的电平。激活 指令执行完毕后,常规电压源vccsa连接到感应放大器,使位线信号回到 vccsa的电平。

83.在激活命令之后而在t2之前,如对dram单元执行一个(或多个)读取 (read)或写入(write)命令,并于读取命令期间本发明将第一维持电压源 (vccsa m1)再次连接到感测放大器。是以在读取或写入命令期间内,位线 的信号至少会被加压或提升到vccsa m1的电平。之后,读取或写入命令 可以称为数据存取命令。

84.同时,伴随着数据存取命令的列地址(column address)信息也会被输入到 dram中,以选择合适的位线(或驱动合适的位线开关)。因此,也可在dram 接收到列地址信息后,相应的第一维持电压源(vccsa m1)连接到感应放大 器。因此,相应的第一维持电压源

(vccsa m1)可以根据以下的一连接到感 测放大器:(1)数据存取命令;(2)列地址信息;(3)数据存取命令和列地址信 息的组合。因此,在执行数据存取命令的过程中,位线的信号将至少被加压(提 升或踢升”kick”)至vccsa m1的电平,或者在dram接收到列地址信息 后,位线的信号将至少加压或踢升至vccsa m1。这种对位线信号的加压或 踢升可以命名为存取(access)-列(column)踢,或简称为a-c kick。

85.而于数据存取命令执行后,常规电压源vccsa再次连接到感测放大器 (通过关闭开关13和打开开关14,如图3a所示),然后位线的信号将回到 vccsa的电平。在读取命令期间利用这种加压或提升位线的信号电压电平方 式,将可改善信号发展时间(signal development time)。例如,在vccsa为1.1v 和m1为0.2v的情况下,在读取命令期间内有加压的信号发展时间,比在读 取命令期间内没有加压的信号发展时间快约20%~30%左右。

86.同样,在t2时间后的restore操作时间(或进行预充电时),本实施例 仍将原来的vccsa电压源与感测放大器断开,使第一维持电压源 vccsa m1将连接到感测放大器,如此位线的信号将至少被加压到 vccsa m1电平。因此,dram单元的存储电容将被提供比常规信号 one(vccsa)高的第一维持电压源的vccsa m1电位。

87.然而,在另一个实施例中如图8b所示,在激活指令与读取命令期间位线 的信号被加压到vccsa m1电平,但在t2时间后的restore操作时间(或 进行预充电时),原来的vccsa电压源(而不是vccsa m1)仍然连接到感应 放大器,即位线的信号不被加压到vccsa m1电平。

88.此外,在另一实施例中,在激活命令期间,位线的信号不被加压到 vccsa m1电平;但在数据存取命令期间(或列地址数据被dram接收后), 位线的信号则被加压到vccsa m1电平,而在t2时间后的restore操作 时间(或进行预充电时),第一维持电压源vccsa m1也连接到感测放大器, 使得位线的信号将至少被加压到vccsa m1电平,如图8c所示。

89.本发明的第六实施例∶

90.图8d是本发明dram单元操作相关信号波形的另一实施例。类似于图 8a,在t1和t2之间的期间,当对于dram单元依序执行一激活指令和至 少一个数据存取指令时,在激活指令操作期间可以将相应的第一维持电压源 (vccsa m1)连接到感测放大器(通过打开开关13,如图3a所示)。此外,在 数据存取指令执行期间(或接收到列地址后),再一次将相应的第一维持电压源 (vccsa m1)连接到感测放大器。进一步,在上述激活命令执行期间、和数 据存取命令执行期间(或接收到列地址后),也将相应的第二维持电压源 (vss-m2)连接到感测放大器(通过打开如图3b所示的开关23)。

91.因此,在激活命令期间位线(bl)的信号将至少被加压到vccsa m1电 平,而互补位线(blb)的信号也被加压到vss-m2电平,而在数据存取命令期 间(或接收到列地址后),位线(bl)的信号将再一次至少被加压到vccsa m1 电平,而互补位线(blb)的信号也再一次被加压到vss-m2电平。

92.在执行完激活命令和数据存取命令后,随即将常规电压源vccsa连接 到感测放大器上(通过关闭开关13,打开开关14,如图3a所示),也同时将 常规电压源vss连接到感测放大器上(通过关闭开关23,打开开关24,如图 3b所示),则位线的信号将回到vccsa电平,而互补位线的信号将回到vss 电平。

93.同样,在t2时间后的restore操作时间(或进行预充电时),原vccsa 和vss电压源

与感测放大器被断开(例如,分别关闭如图3a和图3b中的开 关14和开关24),并将第一维持电压源vccsa m1将连接到感测放大器(即 打开图3a中的开关13),而第二维持电压源vss-m2也连接到感测放大器(即 打开图3b中的开关23),因此位线的信号将至少被加压到vccsa m1电平, 而互补位线的信号将至少被加压到vss-m2电平。

94.图9显示在dram单元的操作期间,加压期间与位线信号之间的关系。 于图9中,对应于restore阶段(或预充电)的加压期间k4时,位线信号可 被加压至vccsa m1电平,而对应于激活命令的加压期间k1时位线信号也 被加压至vccsa m1电平,又对应于读取命令的加压期间k2(或k3)时位线 信号也被加压至vccsa m1电平。但加压期间k4可大于加压期间k1,而 加压期间k1可等于加压期间k2(或k3)。

95.综上所述,本发明所公开的动态随机存取存储器,可以在动态随机存取 存储器单元内的存取晶体管关闭(或耦接于所述动态随机存取存储器单元的 字线施加负偏压)之前,将高于one信号电位的第一电压储存或耦接至动态 随机存取存储器单元内。同样地,也可在动态随机存取存储器单元内的存取 晶体管关闭(或耦接于所述动态随机存取存储器单元的字线施加负偏压)之前, 将低于zero信号电位的第二电压储存或耦接至动态随机存取存储器单元 内。因此,在动态随机存取存储器单元内的存取晶体管关闭后,即使仍有储 存电容的漏电流通过动态随机存取存储器单元内的存取晶体管,但动态随机 存取存储器单元内的储存电容所储存的电荷仍可比所述现有的动态随机存取 存储器的架构维持更长的一段时间。

96.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本 领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和 原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护 范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。