生成多电平信号的方法和基于多电平信号发送数据的方法

1.本技术要求于2020年8月21日在韩国知识产权局(kipo)提交的第10-2020-0105470号韩国专利申请的优先权,该韩国专利申请的公开通过引用全部包含于此。

技术领域

2.发明构思的示例性实施例总体上涉及半导体集成电路,更具体地,涉及生成多电平信号的方法以及使用生成多电平信号(multi-level signal)的方法来发送数据的方法。

背景技术:

3.根据半导体存储器装置在从电源断开时是否保留存储的数据,半导体存储器装置通常可以被划分为两种类别。这些类别包括易失性存储器装置和非易失性存储器装置,易失性存储器装置在从电源断开时丢失存储的数据,非易失性存储器装置在从电源断开时保留存储的数据。易失性存储器装置可以以高的速度执行读取操作和写入操作,而存储在其中的内容可在断电时丢失。非易失性存储器装置即使在断电时也可以保留存储在其中的内容,这意味着非易失性存储器装置可以用于存储必须保留而与它们是否被供电无关的数据。

4.近来,随着半导体存储器装置的性能已经提高,存储器控制器与半导体存储器装置之间的通信速度(或p接口速度)也已经增大。因此,已经研究了在一个单位时间间隔(ui)期间发送多个位(bit)的多电平信令(multi-level signaling)。

技术实现要素:

5.根据发明构思的示例性实施例,在生成具有彼此不同的三个或更多个电压电平中的一个电压电平的多电平信号的方法中,包括两个或更多个位的输入数据被接收。两个或更多个驱动路径中的至少一个驱动路径的驱动强度基于所述两个或更多个位被改变,使得第一转变时间被改变,在第一转变时间期间输出数据信号从第一电压电平被转变为第二电压电平。作为多电平信号的输出数据信号被生成,使得输出数据信号的第一转变时间被改变并且第二转变时间被保持,在第二转变时间期间输出数据信号从第一电压电平被转变为与第二电压电平不同的第三电压电平。

6.根据发明构思的示例性实施例,在基于具有彼此不同的三个或更多个电压电平中的一个电压电平的多电平信号来发送数据的方法中,作为多电平信号的第一输出数据信号基于第一输入数据被生成。作为多电平信号的第二输出数据信号基于第二输入数据被生成。第一输出数据信号和第二输出数据信号分别通过彼此不同的第一通道和第二通道被发送。当生成第一输出数据信号时,包括两个或更多个位的第一输入数据被接收。两个或更多个驱动路径中的至少一个驱动路径的驱动强度基于包括在第一输入数据中的所述两个或更多个位被改变,使得第一转变时间被改变,在第一转变时间期间,第一输出数据信号从第一电压电平被转变为第二电压电平。第一输出数据信号被生成,使得第一输出数据信号的第一转变时间被改变并且第二转变时间被保持,在第二转变时间期间,第一输出数据信号

从第一电压电平被转变为与第二电压电平不同的第三电压电平。

7.根据发明构思的示例性实施例,在生成具有彼此不同的第一电压电平、第二电压电平、第三电压电平和第四电压电平中的一个电压电平的多电平信号的方法中,包括彼此不同的第一位和第二位的输入数据被接收。输入数据被划分为第一位和第二位。基于第一位和第二位,确定输出数据信号从第一电压电平被转变为第二电压电平所处于的第一边沿是否被检测到。当第一边沿被检测到时,第一预加重控制信号和第二预加重控制信号中的至少一个预加重控制信号被激活。第一预加重控制信号被施加到基于第一位进行操作的第一驱动路径,并且第二预加重控制信号被施加到基于第二位进行操作的第二驱动路径。第一驱动路径和第二驱动路径中的至少一个驱动路径的驱动强度基于第一预加重控制信号和第二预加重控制信号中的激活的至少一个预加重控制信号而增大,使得第一转变时间减少,在第一转变时间期间输出数据信号从第一电压电平被转变为第二电压电平。作为多电平信号的输出数据信号基于第一驱动路径和第二驱动路径被生成,使得输出数据信号的第一转变时间被改变并且第二转变时间被保持,在第二转变时间期间输出数据信号从第一电压电平被转变为第三电压电平。

附图说明

8.通过参照附图详细地描述发明构思的示例性实施例,将更清楚地理解发明构思的以上和其他特征。

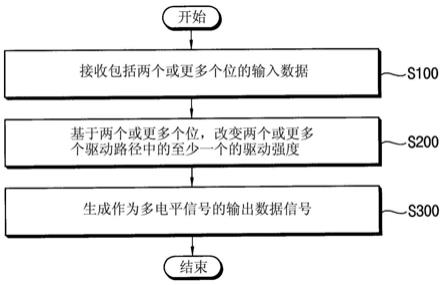

9.图1是示出根据发明构思的示例性实施例的生成多电平信号的方法的流程图。

10.图2是示出根据发明构思的示例性实施例的图1中的改变两个或更多个驱动路径中的至少一个的驱动强度的示例的流程图。

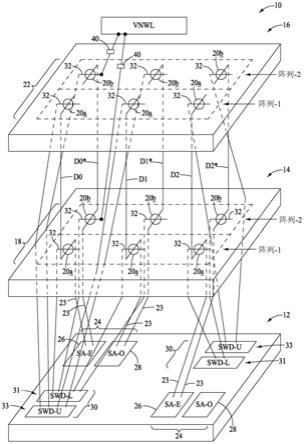

11.图3是示出根据发明构思的示例性实施例的存储器系统的框图。

12.图4a和图4b是示出根据发明构思的示例性实施例的存储器系统的框图。

13.图5是示出根据发明构思的示例性实施例的包括在存储器系统中的存储器控制器的框图。

14.图6是示出根据发明构思的示例性实施例的包括在存储器系统中的存储器装置的框图。

15.图7a、图7b和图7c是用于描述根据发明构思的示例性实施例的通过生成多电平信号的方法而生成的数据信号的示图。

16.图8是示出根据发明构思的示例性实施例的发送器的框图。

17.图9是示出根据发明构思的示例性实施例的包括在图8的发送器中的边沿检测逻辑的框图。

18.图10a和图10b是示出根据发明构思的示例性实施例的包括在图9的边沿检测逻辑中的边沿检测电路的框图。

19.图11a、图11b、图11c、图11d、图11e和图12是用于描述根据发明构思的示例性实施例的通过生成多电平信号的方法和发送器来执行的操作的示图。

20.图13是示出根据发明构思的示例性实施例的图1中的改变两个或更多个驱动路径中的至少一个的驱动强度的示例的流程图。

21.图14是用于描述根据发明构思的示例性实施例的通过生成多电平信号的方法而

生成的数据信号的示图。

22.图15是示出根据发明构思的示例性实施例的发送器的框图。

23.图16和图17是示出根据发明构思的示例性实施例的发送数据的方法的流程图。

24.图18a和图18b是示出根据发明构思的示例性实施例的存储器系统的框图。

25.图19是示出根据发明构思的示例性实施例的计算系统的框图。

26.图20是示出根据发明构思的示例性实施例的通信系统的框图。

具体实施方式

27.发明构思的示例性实施例提供了在信号基于多电平信令被生成时使用选择性均衡化来生成能够具有提高的或增强的信号特性的多电平信号(multi-level signal,又称为多级信号)的方法。

28.发明构思的示例性实施例还提供了使用生成多电平信号的方法来发送数据的方法。

29.发明构思的示例性实施例还分别提供了执行发送数据的方法和生成多电平信号的方法的发送器和存储器系统。

30.在下文中将参照附图更充分地描述发明构思的示例性实施例。贯穿本技术,同样的参考标号可以指同样的元件。

31.图1是示出根据发明构思的示例性实施例的生成多电平信号的方法的流程图。

32.参照图1,根据发明构思的示例性实施例的生成多电平信号的方法被执行以在一个单位时间间隔(ui)期间发送或发出具有三个或更多个不同的电压电平之一的多电平信号,并且由生成或发送多电平信号的发送器执行。发送器可以被包括在各种通信系统和/或信号发送系统中,并且可以被包括在例如存储器系统中。稍后将详细地描述发送器、存储器系统和多电平信号的配置。

33.在根据发明构思的示例性实施例的生成多电平信号的方法中,接收包括两个或更多个位的输入数据(操作s100)。例如,输入数据可以是用于生成多电平信号的多位数据。

34.基于包括在输入数据中的两个或更多个位来改变两个或更多个驱动路径(或数据路径)中的至少一个的驱动强度(操作s200)。例如,两个或更多个驱动路径可以被包括在发送器中,并且两个或更多个驱动路径中的每个可以基于两个或更多个位中的相应的位进行操作。例如,两个或更多个驱动路径中的至少一个的驱动强度可以被改变,使得输出数据信号在其期间从第一电压电平被转变为第二电压电平的第一转变时间被改变(例如,使得输出数据信号以其从第一电压电平被转变为第二电压电平的第一斜率被改变)。第一转变时间可以表示用于将输出数据信号从第一电压电平转变为第二电压电平的时间间隔。改变驱动强度的操作可以被称为均衡化操作或均衡化。将参照图2和图13描述操作s200。

35.基于输入数据和操作s200来生成作为多电平信号的输出数据信号(操作s300)。例如,当生成输出数据信号时,用于从第一电压电平转变为第二电压电平的第一转变时间可以被改变(例如,第一斜率可以被改变),并且输出数据信号在其期间从第一电压电平被转变为第三电压电平(不同于第二电压电平)的第二转变时间可以被保持或不改变(例如,输出数据信号以其从第一电压电平被转变为第三电压电平的第二斜率可以被保持)。第二转变时间可以表示用于将输出数据信号从第一电压电平转变为第三电压电平的时间间隔。换

言之,当输出数据信号从第一电压电平被转变为第二电压电平时,均衡化操作可以被执行,并且当输出数据信号从第一电压电平被转变为第三电压电平时,均衡化操作可以不被执行。

36.在根据发明构思的示例性实施例的方法中,输出数据信号基于多电平信令方案被生成。多电平信令方案可以用作压缩带宽以按给定的位速率(bit rate,或比特率)发送数据的方法。在简单的二进制方案中,两个单一符号(通常地,两个电压电平)可以用于表示“1”和“0”,因此,符号速率可以等于位速率。相比之下,多电平信令方案的原理可以是使用m个符号的较大符号系统(alphabet)来表示数据,使得每个符号可以表示多于一位的数据。结果,需要被发送的符号的数量可以小于位的数量(例如,符号速率可以小于位速率),因此,带宽可以被压缩。符号的符号系统可以由多个不同的电压电平构成。例如,在四电平方案中,两个数据位的组可以被映射到四个符号中的一个。针对每对数据位,仅一个符号需要被发送,因此,符号速率可以是位速率的一半。

37.换言之,多电平信令方案可以用于增大数据发送(或传送)速率而不增大数据发送的频率和/或传递的数据的发送功率。一种类型的多电平信令方案的示例可以是其中多电平信号的唯一符号可表示多个位的数据的脉幅调制(pulse-amplitude modulation,pam)方案。数字pam方案中的可行的脉幅的数量可以是2的某个幂。例如,在4电平pam中(例如,在pam4中)可以存在22个可行的离散脉幅,在8电平pam中(例如,在pam8中)可以存在23个可行的离散脉幅,并且在16电平pam中(例如,在pam16中)可以存在24个可行的离散脉幅。然而,发明构思不限于此,并且发明构思的示例性实施例可以应用于或被采用为具有k个可行的脉幅的k电平pam(例如,pam(k)),其中,k是大于或等于3的自然数。

38.在根据发明构思的示例性实施例的生成多电平信号的方法中,选择性的或适应性的均衡化方案可以被实施。在选择性均衡化方案中,现有的或常规的驱动路径可以按原样被使用,并且均衡化操作可以仅当在输出数据信号上发生特定电平转变时被执行。换言之,均衡化操作可以仅对能够发生在多电平信号上的一些电平转变执行。因此,与均衡化操作对所有的电平转变执行的示例相比,可以降低功耗,并且可以有效地提高或增强信号特性。

39.图2是示出根据发明构思的示例性实施例的图1中的改变两个或更多个驱动路径中的至少一个的驱动强度的示例的流程图。

40.参照图1和图2,当改变两个或更多个驱动路径中的至少一个的驱动强度(图1的操作s200)时,可以将输入数据划分为两个或更多个位(操作s210)。可以基于两个或更多个位来确定输出数据信号从第一电压电平被转变为第二电压电平所处于的第一边沿是否被检测到(操作s220)。

41.根据发明构思的示例性实施例,第一电压电平可以对应于最低电压电平,第二电压电平可以对应于最高电压电平。然而,发明构思不限于此。例如,第一电压电平可以不对应于最低电压电平,或者第二电压电平可以不对应于最高电压电平。

42.当检测到第一边沿(操作s220:是)时,可以激活两个或更多个预加重控制信号中的至少一个(操作s230),并且可以基于激活的预加重控制信号而增大两个或更多个驱动路径中的所述至少一个的驱动强度,使得减少输出数据信号的第一转变时间(例如,使得增大输出数据信号的第一斜率)(操作s240)。换言之,均衡化操作可以对第一边沿执行。

43.在发明构思的示例性实施例中,如将参照图8所述,两个或更多个驱动路径中的每

个可以包括两个或更多个预加重驱动器电路中的相应的预加重驱动器电路,两个或更多个预加重驱动器电路可以基于两个或更多个预加重控制信号中的相应的预加重控制信号进行操作。当特定的预加重控制信号被激活时,对应的预加重驱动器电路可以被启用,驱动强度可以通过启用的预加重驱动器电路而增大。例如,驱动强度的递增量(例如,第一转变时间的递减量和/或第一斜率的递增量)可以基于激活的预加重控制信号的数量和类型而被确定。

44.当未检测到第一边沿(操作s220:否)时(例如,当检测到输出数据信号从第一电压电平被转变为第三电压电平所处于的第二边沿时),可以对两个或更多个预加重控制信号中的全部进行去激活,并且可以保持两个或更多个驱动路径中的全部的驱动强度,使得保持输出数据信号的第二转变时间(例如,使得保持输出数据信号的第二斜率)(操作s250)。换言之,均衡化操作可以不对第二边沿执行。

45.如上所述,当均衡化操作对第一边沿执行时,与当均衡化操作不对第一边沿执行时相比,第一转变时间可以减小,第一斜率可以增大。此外,当均衡化操作不对第二边沿执行时,第二转变时间和第二斜率可以被保持。因此,如将参照图11a所述,当选择性均衡化方案根据发明构思的示例性实施例被执行时,第一转变时间和第二转变时间可以变得彼此不同。

46.尽管图2示出了选择性均衡化方案仅对单个边沿(例如,对第一边沿)执行的示例,但发明构思不限于此,并且如将参照图13所述,选择性均衡化方案可以对两个或更多个边沿执行。

47.图3是示出根据发明构思的示例性实施例的存储器系统的框图。

48.参照图3,存储器系统10包括存储器控制器20和存储器装置40。存储器系统10还可以包括将存储器控制器20与存储器装置40电连接的多条信号线30。

49.存储器装置40由存储器控制器20控制。例如,基于来自主机的请求,存储器控制器20可以将数据存储(例如,写入或编程)到存储器装置40中,或者可以从存储器装置40获取(例如,读取或感测)数据。

50.多条信号线30可以包括控制线、命令线、地址线、数据输入/输出(i/o)线和电源线。存储器控制器20可以分别经由命令线、地址线和控制线将命令cmd、地址addr和控制信号ctrl发送到存储器装置40,可以经由数据i/o线与存储器装置40交换数据信号mldat,并且可以经由电源线将电源电压pwr传输到存储器装置40。例如,数据信号mldat可以是根据发明构思的示例性实施例而生成和发送的多电平信号。多条信号线30还可以包括用于发送数据选通信号(dqs)的dqs线。

51.在发明构思的示例性实施例中,信号线30中的至少一部分或全部可以被称为通道。如在此使用的术语“通道”可以表示包括用于发送数据信号mldat的数据i/o线的信号线。然而,发明构思不限于此,并且通道还可以包括用于发送命令cmd的命令线和/或用于发送地址addr的地址线。

52.图4a和图4b是示出根据发明构思的示例性实施例的存储器系统的框图。

53.参照图4a和图4b,存储器系统11包括存储器控制器21、存储器装置41以及多个通道31a、31b和31c。例如,通道31a、31b和31c的数量可以为n,其中,n是大于或等于2的自然数。

54.存储器控制器21可以包括多个发送器25a、25b和25c、多个接收器27a、27b和27c以及多个数据i/o垫29a、29b和29c。存储器装置41可以包括多个发送器45a、45b和45c、多个接收器47a、47b和47c以及多个数据i/o垫49a、49b和49c。

55.多个发送器25a、25b、25c、45a、45b和45c中的每个可以生成多电平信号,可以执行参照图1描述的根据发明构思的示例性实施例的生成多电平信号的方法,并且可以是将参照图8和图15描述的根据发明构思的示例性实施例的发送器。多个接收器27a、27b、27c、47a、47b和47c中的每个可以接收多电平信号。多个发送器25a、25b、25c、45a、45b和45c以及多个接收器27a、27b、27c、47a、47b和47c可以通过多个通道31a、31b和31c执行将参照图16和图17描述的根据发明构思的示例性实施例的发送数据的方法。

56.多个数据i/o垫29a、29b、29c、49a、49b和49c中的每个可以连接到多个发送器25a、25b、25c、45a、45b和45c中的相应的发送器以及多个接收器27a、27b、27c、47a、47b和47c中的相应的接收器。

57.多个通道31a、31b和31c可以将存储器控制器21与存储器装置41连接。多个通道31a、31b和31c中的每个可以通过多个数据i/o垫29a、29b和29c中的相应的数据i/o垫,连接到多个发送器25a、25b和25c中的相应的发送器以及多个接收器27a、27b和27c中的相应的接收器。此外,多个通道31a、31b和31c中的每个可以通过多个数据i/o垫49a、49b和49c中的相应的数据i/o垫,连接到多个发送器45a、45b和45c中的相应发送器以及多个接收器47a、47b和47c中的相应的接收器。多电平信号可以通过多个通道31a、31b和31c中的每个被发送。

58.图4a示出了将数据从存储器控制器21传送到存储器装置41的操作。例如,发送器25a可以基于输入数据dat11生成作为多电平信号的输出数据信号ds11,输出数据信号ds11可以通过通道31a从存储器控制器21被发送到存储器装置41,接收器47a可以接收输出数据信号ds11以获得与输入数据dat11对应的数据odat11。相似地,发送器25b可以基于输入数据dat21生成作为多电平信号的输出数据信号ds21,输出数据信号ds21可以通过通道31b被发送到存储器装置41,接收器47b可以接收输出数据信号ds21以获得与输入数据dat21对应的数据odat21。发送器25c可以基于输入数据datn1生成作为多电平信号的输出数据信号dsn1,输出数据信号dsn1可以通过通道31c被发送到存储器装置41,接收器47c可以接收输出数据信号dsn1以获得与输入数据datn1对应的数据odatn1。例如,输入数据dat11、dat21和datn1可以是将要写入存储器装置41中的写入数据。

59.图4b示出了将数据从存储器装置41传送到存储器控制器21的操作。例如,发送器45a可以基于输入数据dat12生成作为多电平信号的输出数据信号ds12,输出数据信号ds12可以通过通道31a从存储器装置41被发送到存储器控制器21,接收器27a可以接收输出数据信号ds12以获得与输入数据dat12对应的数据odat12。相似地,发送器45b可以基于输入数据dat22生成作为多电平信号的输出数据信号ds22,输出数据信号ds22可以通过通道31b被发送到存储器控制器21,接收器27b可以接收输出数据信号ds22以获得与输入数据dat22对应的数据odat22。发送器45c可以基于输入数据datn2生成作为多电平信号的输出数据信号dsn2,输出数据信号dsn2可以通过通道31c被发送到存储器控制器21,接收器27c可以接收输出数据信号dsn2以获得与输入数据datn2对应的数据odatn2。例如,输入数据dat12、dat22和datn2可以是从存储器装置41获取的读取数据。

60.图5是示出根据发明构思的示例性实施例的包括在存储器系统中的存储器控制器的框图。

61.参照图5,存储器控制器100可以包括至少一个处理器110、缓冲存储器120、主机接口(i/f)130、纠错码(ecc)(块)140和存储器接口(i/f)150。

62.处理器110可以响应于经由主机接口130从外部主机接收的命令和/或请求,控制存储器控制器100的操作。例如,处理器110可以通过采用用于操作存储器装置(例如,图3中的存储器装置40)的固件,来控制相应的组件。

63.缓冲存储器120可以存储由处理器110运行和处理的指令和数据。例如,缓冲存储器120可以利用易失性存储器装置(诸如,动态随机存取存储器(dram)、静态随机存取存储器(sram)、高速缓冲存储器等)被实现。

64.主机接口130可以提供外部主机与存储器控制器100之间的物理连接。主机接口130可以针对外部主机与存储器控制器100之间的通信而提供与外部主机的总线格式对应的接口。在发明构思的示例性实施例中,外部主机的总线格式可以是小型计算机系统接口(scsi)或串行连接scsi(sas)接口。在发明构思的示例性实施例中,外部主机的总线格式可以是通用串行总线(usb)、外围组件互连(pci)快速(pcie)、高级技术附件(ata)、并行ata(pata)、串行ata(sata)、非易失性存储器(nvm)快速(nvme)等格式。

65.用于纠错的ecc块140可以使用bose-chaudhuri-hocquenghem(bch)码、低密度奇偶校验(ldpc)码、turbo码、reed-solomon码、卷积码、递归系统卷积码(rsc)、网格编码调制(tcm)、块编码调制(bcm)等来执行编码调制,或者可以使用上述码或其他纠错码来执行ecc编码和ecc解码。

66.存储器接口150可以与存储器装置交换数据。存储器接口150可以将命令和地址发送到存储器装置,并且可以将数据发送到存储器装置或接收从存储器装置读取的数据。例如,根据发明构思的示例性实施例的生成多电平信号的发送器(例如,图4a中的发送器25a)和接收多电平信号的接收器(例如,图4a中的接收器27a)可以被包括在存储器接口150中。

67.图6是示出根据发明构思的示例性实施例的包括在存储器系统中的存储器装置的框图。

68.参照图6,存储器装置200包括控制逻辑210、刷新控制电路215、地址寄存器220、存储体控制逻辑230、行地址复用器240、列地址锁存器250、行解码器、列解码器、存储器单元阵列、感测放大器单元、输入/输出(i/o)门控电路290、数据i/o缓冲器295、片上端接(on-die termination,odt)电路297和数据i/o垫299。在发明构思的示例性实施例中,存储器装置200可以是例如易失性存储器装置。例如,存储器装置200可以是诸如动态随机存取存储器(dram)的各种易失性存储器装置之一。

69.存储器单元阵列可以包括多个存储器单元。存储器单元阵列可以包括多个存储体阵列,例如,第一存储体阵列280a、第二存储体阵列280b、第三存储体阵列280c和第四存储体阵列280d。行解码器可以包括多个存储体行解码器,例如,分别连接到第一存储体阵列280a、第二存储体阵列280b、第三存储体阵列280c和第四存储体阵列280d的第一存储体行解码器260a、第二存储体行解码器260b、第三存储体行解码器260c和第四存储体行解码器260d。列解码器可以包括多个存储体列解码器,例如,分别连接到第一存储体阵列280a、第二存储体阵列280b、第三存储体阵列280c和第四存储体阵列280d的第一存储体列解码器

270a、第二存储体列解码器270b、第三存储体列解码器270c和第四存储体列解码器270d。感测放大器单元可以包括多个存储体感测放大器,例如,分别连接到第一存储体阵列280a、第二存储体阵列280b、第三存储体阵列280c和第四存储体阵列280d的第一存储体感测放大器285a、第二存储体感测放大器285b、第三存储体感测放大器285c和第四存储体感测放大器285d。

70.第一存储体阵列280a至第四存储体阵列280d、第一存储体行解码器260a至第四存储体行解码器260d、第一存储体列解码器270a至第四存储体列解码器270d以及第一存储体感测放大器285a至第四存储体感测放大器285d可以分别形成第一存储体至第四存储体。例如,第一存储体阵列280a、第一存储体行解码器260a、第一存储体列解码器270a和第一存储体感测放大器285a可以形成第一存储体;第二存储体阵列280b、第二存储体行解码器260b、第二存储体列解码器270b和第二存储体感测放大器285b可以形成第二存储体;第三存储体阵列280c、第三存储体行解码器260c、第三存储体列解码器270c和第三存储体感测放大器285c可以形成第三存储体;第四存储体阵列280d、第四存储体行解码器260d、第四存储体列解码器270d和第四存储体感测放大器285d可以形成第四存储体。

71.地址寄存器220可以从存储器控制器(例如,图3中的存储器控制器20)接收包括存储体地址bank_addr、行地址row_addr和列地址col_addr的地址addr。地址寄存器220可以将接收的存储体地址bank_addr提供到存储体控制逻辑230,可以将接收的行地址row_addr提供到行地址复用器240,并且可以将接收的列地址col_addr提供到列地址锁存器250。

72.存储体控制逻辑230可以响应于存储体地址bank_addr的接收,生成存储体控制信号。第一存储体行解码器260a至第四存储体行解码器260d中的与接收的存储体地址bank_addr对应的存储体行解码器可以响应于由存储体控制逻辑230生成的存储体控制信号而被激活,第一存储体列解码器270a至第四存储体列解码器270d中的与接收的存储体地址bank_addr对应的存储体列解码器可以响应于由存储体控制逻辑230生成的存储体控制信号而被激活。

73.刷新控制电路215可以响应于刷新命令的接收或任何自刷新模式的进入,生成刷新地址ref_addr。例如,刷新控制电路215可以包括刷新计数器,刷新计数器被配置为将刷新地址ref_addr从存储器单元阵列的第一地址顺序地改变到存储器单元阵列的最后的地址。刷新控制电路215可以从控制逻辑210接收控制信号。

74.行地址复用器240可以从地址寄存器220接收行地址row_addr,并且可以从刷新控制电路215接收刷新地址ref_addr。行地址复用器240可选择性地输出行地址row_addr或刷新地址ref_addr。从行地址复用器240输出的行地址(例如,行地址row_addr或刷新地址ref_addr)可以被施加到第一存储体行解码器260a至第四存储体行解码器260d。

75.第一存储体行解码器260a至第四存储体行解码器260d中的激活的存储体行解码器可以对从行地址复用器240输出的行地址进行解码,并且可以激活与行地址对应的字线。例如,激活的存储体行解码器可以将字线驱动电压施加到与行地址对应的字线。

76.列地址锁存器250可以从地址寄存器220接收列地址col_addr,并且可以临时存储接收的列地址col_addr。列地址锁存器250可以将临时存储的或接收的列地址col_addr施加到第一存储体列解码器270a至第四存储体列解码器270d。

77.第一存储体列解码器270a至第四存储体列解码器270d中的激活的存储体列解码

器可以对从列地址锁存器250输出的列地址col_addr进行解码,并且可以控制i/o门控电路290输出与列地址col_addr对应的数据。

78.i/o门控电路290可以包括用于对i/o数据进行门控的电路。例如,i/o门控电路290可以包括输入数据掩码逻辑、用于存储从第一存储体阵列280a至第四存储体阵列280d输出的数据的读取数据锁存器以及用于将数据写入第一存储体阵列280a至第四存储体阵列280d的写入驱动器。

79.将要从第一存储体阵列280a至第四存储体阵列280d中的一个存储体阵列读取的数据dq可以通过结合到所述一个存储体阵列的感测放大器被感测,并且可以被存储在读取数据锁存器中。存储在读取数据锁存器中的数据dq可以经由数据i/o缓冲器295和数据i/o垫299被提供到存储器控制器。经由数据i/o垫299接收的将要写入第一存储体阵列280a至第四存储体阵列280d中的一个存储体阵列的数据dq可以从存储器控制器被提供到数据i/o缓冲器295。经由数据i/o垫299接收且提供到数据i/o缓冲器295的数据dq可以经由i/o门控电路290中的写入驱动器被写入所述一个存储体阵列。例如,根据发明构思的示例性实施例的生成多电平信号的发送器(例如,图4a中的发送器45a)和接收多电平信号的接收器(例如,图4a中的接收器47a)可以被包括在数据i/o缓冲器295中。

80.控制逻辑210可以控制存储器装置200的操作。例如,控制逻辑210可以生成用于存储器装置200的控制信号,以执行数据写入操作或数据读取操作。控制逻辑210可以包括命令解码器211和模式寄存器212,命令解码器211对从存储器控制器接收的命令cmd进行解码,模式寄存器212设置存储器装置200的操作模式。

81.odt电路297可以连接到数据i/o垫299和数据i/o缓冲器295。当odt电路297被启用时,odt操作可以被执行。odt操作可以通过使用端接电阻器(termination resistor)来减少(和/或防止)信号被反射,以提高信号完整性。

82.尽管根据发明构思的示例性实施例的包括在存储器系统中的存储器装置基于dram被描述,但存储器装置可以是任何易失性存储器装置和/或任何非易失性存储器装置,例如,闪存、相变随机存取存储器(pram)、电阻式随机存取存储器(rram)、纳米浮栅存储器(nfgm)、聚合物随机存取存储器(poram)、磁性随机存取存储器(mram)、铁电随机存取存储器(fram)、晶闸管随机存取存储器(tram)等。

83.在下文中,将基于多电平信令方案(例如,pam方案)的各种示例和根据多电平信令方案的发送器的各种示例来详细地描述发明构思的示例性实施例。

84.图7a、图7b和图7c是用于描述根据发明构思的示例性实施例的通过生成多电平信号的方法而生成的数据信号的示图。

85.图7a示出了基于4电平方案(例如,pam4方案)生成的数据信号(例如,pam4信号)的理想眼图。图7b是示出图7a的眼图的简化图。图7c是示出根据发明构思的一个示例性实施例的选择性均衡化方案的示图。

86.参照图7a,眼图可以用于指示高速发送中的信号的质量。例如,眼图可以表示信号的四个符号(例如,“00”、“01”、“10”和“11”),四个符号中的每个可以由不同的电压电平(例如,电压振幅)vl11、vl21、vl31和vl41中的相应的电压电平表示。眼图可以用于提供信号完整性的健康度(health)的视觉指示,并且可以指示数据信号的噪声裕度。

87.为了生成眼图,示波器或其他计算装置可以根据采样周期sp(例如,单位时间间隔

或位周期)对数字信号进行采样。采样周期sp可以由与测量的信号的发送相关联的时钟定义。示波器或其他计算装置可以在采样周期sp期间测量信号的电压电平,以形成多条迹线(trace)trc。与测量的信号相关联的各种特性可以通过使多条迹线trc重叠而被确定。

88.眼图可以用于确认通信信号的多个特性(诸如,抖动、串扰、电磁干扰(emi)、信号损失、信噪比(snr)、其他特性或它们的组合)。

89.例如,眼图中的眼的宽度w可以用于指示测量的信号的时序同步或测量的信号的抖动效应。例如,眼图可以指示眼开度op,眼开度op表示各种电压电平vl11、vl21、vl31和vl41之间的峰到峰(peak-to-peak)电压差。眼开度op可以与用于在测量的信号的不同的电压电平vl11、vl21、vl31和vl41之间进行区别的电压裕度相关。例如,眼图可以用于确认从第一振幅到第二振幅的转变的上升时间rt和/或下降时间ft。上升时间rt或下降时间ft可以指示用于从一个电压电平转变为另一电压电平的时间,可以分别与上升沿和下降沿相关或相关联,并且可以与参照图1描述的第一转变时间和第二转变时间对应。在其他方面之中,迹线trc在上升时间rt或下降时间ft期间的斜率可以指示信号对时序误差的敏感度。

90.例如,眼图可以用于确认测量的信号中的抖动jt的量。抖动jt可以指由上升时间和下降时间的未对齐导致的时序误差。当在与由数据时钟定义的理想时间不同的时间出现上升沿或下降沿时,可发生抖动jt。抖动jt可由信号反射、符号间干扰(intersymbol interference)、串扰、工艺-电压-温度(pvt)变化、随机抖动、加性噪声(additive noise)或它们的组合导致。

91.参照图7b,示出了作为pam4信号的数据信号的不同的第一电压电平vl11、第二电压电平vl21、第三电压电平vl31和第四电压电平vl41,并且示出了数据信号的第一眼eye11、第二眼eye21和第三眼eye31。由粗实线示出的部分表示眼eye11、eye21和eye31的尺寸。

92.第一电压电平vl11可以比第二电压电平vl21低,第二电压电平vl21可以比第三电压电平vl31低,第三电压电平vl31可以比第四电压电平vl41低。此外,第一眼eye11可以位于第一电压电平vl11与第二电压电平vl21之间,第二眼eye21可以位于第二电压电平vl21与第三电压电平vl31之间,第三眼eye31可以位于第三电压电平vl31与第四电压电平vl41之间。

93.并非所有的边沿都可影响眼eye11、eye21和eye31的特性。换言之,仅一些边沿可影响眼eye11、eye21和eye31的特性。例如,第一眼eye11的特性可以通过从第四电压电平vl41到第一电压电平vl11的下降沿(例如,“11

”‑

》“00”)、从第一电压电平vl11到第二电压电平vl21的上升沿(例如,“00

”‑

》“01”)、从第一电压电平vl11到第四电压电平vl41的上升沿(例如,“00

”‑

》“11”)以及从第二电压电平vl21到第一电压电平vl11的下降沿(例如,“01

”‑

》“00”)而被确定。相似地,第二眼eye21的特性可以通过第二电压电平vl21与第四电压电平vl41之间的上升沿和下降沿(例如,“01”《-》“11”)以及第一电压电平vl11与第三电压电平vl31之间的上升沿和下降沿(例如,“00”《-》“10”)而被确定。第三眼eye31的特性可以通过第三电压电平vl31与第四电压电平vl41之间的上升沿和下降沿(例如,“10”《-》“11”)以及第一电压电平vl11与第四电压电平vl41之间的上升沿和下降沿(例如,“00”《-》“11”)而被确定。

94.当均衡化操作对所有的边沿(例如,所有的电平转变)执行时,均衡化操作还可对

不影响眼特性的边沿执行。不适合于眼特性的均衡化操作可导致不必要的功耗,并且在一些情况下可使眼特性退化或劣化。另一方面,当根据发明构思的示例性实施例仅对一些边沿(例如,一些电平转变)执行均衡化操作时,可以降低功耗,并且可以有效地提高或增强信号特性。

95.参照图7c,根据均衡化操作的次数的功耗和抖动量的变化被示出为曲线图。水平轴表示均衡化操作(eql)被执行的次数或其中均衡化操作被执行的电平转变的数量。竖直轴表示功耗(pwr_c)和抖动量(jt_a)。

96.随着均衡化操作被执行的次数增加,功耗可增大,并且抖动量可减少以提高抖动特性。均衡化操作的目标和数量可以考虑数据信号被发送所通过的通道的功耗和特性而设置,因此,选择性均衡化方案可以针对最优性能而被实现。

97.图8是示出根据发明构思的示例性实施例的发送器的框图。

98.参照图8,发送器500包括复用器(mux)510、边沿检测逻辑520以及两个或更多个驱动路径540和550。发送器500还可以包括数据i/o垫580。根据发明构思的示例性实施例,边沿检测逻辑520可以是电路。

99.复用器510接收包括两个或更多个位d0和d1的输入数据dat1,并且将输入数据dat1划分为两个或更多个位d0和d1。边沿检测逻辑520基于两个或更多个位d0和d1检测第一边沿,并且在第一边沿被检测到时激活两个或更多个预加重控制信号pecs1和pecs2中的至少一个。第一边沿表示输出数据信号ds1从第一电压电平被转变为第二电压电平所处于的边沿。两个或更多个驱动路径540和550基于两个或更多个位d0和d1以及两个或更多个预加重控制信号pecs1和pecs2,生成作为多电平信号的输出数据信号ds1。数据i/o垫580可以输出输出数据信号ds1。

100.当第一边沿被检测到时,输出数据信号ds1通过以下步骤被生成:改变两个或更多个驱动路径540和550中的至少一个的驱动强度,使得输出数据信号ds1在其期间从第一电压电平被转变为第二电压电平的第一转变时间被改变。输出数据信号ds1在其期间从第一电压电平被转变为与第二电压电平不同的第三电压电平的第二转变时间被保持。换言之,发送器500可以执行根据发明构思的示例性实施例的生成多电平信号的方法。

101.边沿检测逻辑520可以被设置为基于多个边沿检测启用信号eden来检测包括在输出数据信号ds1中的多个边沿之中的第一边沿。换言之,第一电压电平和第二电压电平可以基于多个边沿检测启用信号eden被确定。在发明构思的示例性实施例中,多个边沿检测启用信号eden可以被预设(或被预先地设置),第一电压电平和第二电压电平可以基于发送输出数据信号ds1的通道的特性而被预确定(或被预先地确定)。在发明构思的示例性实施例中,多个边沿检测启用信号eden可以被实时地设置(或在运行时期间被设置),第一电压电平和第二电压电平可以基于表示发送输出数据信号ds1的通道的特性且从外部接收的特性数据而被实时地确定。例如,如将参照图18a和图18b所述,特性数据可以从包括在接收输出数据信号ds1的接收器中的眼监测器电路被提供。

102.在图8的示例中,输入数据dat1可以包括彼此不同的第一位d0和第二位d1,复用器510可以基于四相位时钟信号ck_4p将输入数据dat1划分为第一位d0和第二位d1。两个或更多个驱动路径540和550可以包括第一驱动路径540和第二驱动路径550,第一驱动路径540基于第一位d0和第一预加重控制信号pecs1进行操作,第二驱动路径550基于第二位d1和第

二预加重控制信号pecs2进行操作。输出数据信号ds1可以与图7a和图7b中示出的数据信号对应,并且可以在一个单位时间间隔期间具有彼此不同的第一电压电平vl11、第二电压电平vl21、第三电压电平vl31和第四电压电平vl41中的一个。

103.在发明构思的示例性实施例中,第一位d0可以是输入数据dat1的最低有效位(lsb),第二位d1可以是输入数据dat1的最高有效位(msb)。第一驱动路径540可以是针对lsb的数据路径,第二驱动路径550可以是针对msb的数据路径。

104.第一驱动路径540可以包括数据缓冲器(例如,第一数据缓冲器)541、驱动器电路(例如,第一驱动器电路)543和预加重驱动器电路(例如,第一预加重驱动器电路)545。第一数据缓冲器541可以临时存储第一位d0。第一驱动器电路543可以基于第一数据缓冲器541的输出,生成用于生成输出数据信号ds1的第一驱动电流i1。第一预加重驱动器电路545可以基于第一预加重控制信号pecs1,生成用于使第一驱动路径540的第一驱动强度增大的第一电流ip1。

105.第二驱动路径550可以包括数据缓冲器(例如,第二数据缓冲器)551、驱动器电路(例如,第二驱动器电路)553、驱动器电路(例如,第三驱动器电路)555和预加重驱动器电路(例如,第二预加重驱动器电路)557。第二数据缓冲器551可以临时存储第二位d1。第二驱动器电路553可以基于第二数据缓冲器551的输出,生成用于生成输出数据信号ds1的第二驱动电流i2。第三驱动器电路555可以基于第二数据缓冲器551的输出,生成用于生成输出数据信号ds1的第三驱动电流i3。第二预加重驱动器电路557可以基于第二预加重控制信号pecs2,生成用于使第二驱动路径550的第二驱动强度增大的第二电流ip2。

106.第二驱动器电路553和第三驱动器电路555可以基于第二数据缓冲器551的输出而被基本同时地启用或禁用。作为针对msb的数据路径的第二驱动路径550应具有比作为针对lsb的数据路径的第一驱动路径540的驱动能力大的驱动能力。因此,第二驱动路径550可以包括比第一驱动路径540的驱动器电路多的驱动器电路,例如,基本同时地启用/禁用的两个驱动器电路553和555。

107.因此,第一驱动路径540和第二驱动路径550基于由驱动器电路(例如,543、553和555)生成的驱动电流(例如,i1、i2和i3)以及由第一预加重驱动器电路和第二预加重驱动器电路(例如,545和557)生成的第一电流和第二电流(例如,ip1和ip2),生成作为多电平信号的输出数据信号ds1。

108.通过激活施加到第一驱动路径540的第一预加重控制信号pecs1以增大第一驱动路径540的第一驱动强度,和/或通过激活施加到第二驱动路径550的第二预加重控制信号pecs2以增大第二驱动路径550的第二驱动强度,第一驱动路径540和第二驱动路径550中的至少一个的驱动强度被改变。

[0109]“预加重”是一种类型的均衡化操作。对信号进行预加重可以包括对信号的高频分量进行提高以补偿在通道中发生的衰减。通常,“预加重”指在信号的转变之后将信号振幅增大。在该上下文中的预加重可以通过放大信号的高频分量(例如,增大高频分量的能含量(energy content)以补偿那些分量的由于通道损失而引起的劣化)而被实现,这增大了信号的总振幅。此外,信号的驱动强度指示信号的电压或电流,例如,当预加重被执行时,信号的驱动强度可以增大。尽管基于预加重描述了根据发明构思的示例性实施例的均衡化操作,但均衡化操作不限于此。

[0110]

在发明构思的示例性实施例中,至少一个预驱动器电路可以设置在数据缓冲器541和551与驱动器电路543、553和555之间以及/或者在边沿检测逻辑520与预加重驱动器电路545和557之间。预驱动器电路可以在将接收的信号传递到下一级之前影响或修改接收的信号(例如,预驱动器可以修改接收的信号以提高通信信号的特性或质量)。预驱动器电路可以附加地或可选地用作选择器。

[0111]

尽管图8示出了用于增大驱动强度的配置530包括第一驱动路径540中所包括的一个预加重驱动器电路545和第二驱动路径550中所包括的一个预加重驱动器电路557,但发明构思不限于此,并且预加重驱动器电路的数量可以被改变。相似地,驱动器电路543、553和555的数量也可以被改变,并且驱动器电路543、553和555的数量与预加重驱动器电路545和557的数量可以彼此相等或不同。

[0112]

图9是示出根据发明构思的示例性实施例的包括在图8的发送器中的边沿检测逻辑的框图。

[0113]

参照图9,边沿检测逻辑520可以包括多个边沿检测电路521、522、523、524、525、526、531、532、533、534、535和536。

[0114]

边沿检测电路521、522、523、524、525和526可以分别基于边沿检测启用信号eden_r1、eden_r2、eden_r3、eden_r4、eden_r5和eden_r6而被选择性地启用。当边沿检测电路521、522、523、524、525和526中的每个被启用时,边沿检测电路521、522、523、524、525和526中的每个可以基于第一位d0和第二位d1检测输出数据信号ds1的相应的上升沿,以激活预加重控制信号pecs1和pecs2中的至少一个。例如,边沿检测电路521可以基于边沿检测启用信号eden_r1而被启用。例如,当边沿检测电路521被启用时,边沿检测电路521可以检测其中输出数据信号ds1从作为最低电压电平的第一电压电平vl11被转变为作为最高电压电平的第四电压电平vl41所处于的第一上升沿(例如,“00

”‑

》“11”)。例如,当第一上升沿由边沿检测电路521检测到时,边沿检测电路521可以激活预加重控制信号pecs1和pecs2两者。

[0115]

边沿检测电路531、532、533、534、535和536可以分别基于边沿检测启用信号eden_f1、eden_f2、eden_f3、eden_f4、eden_f5和eden_f6而被选择性地启用。当边沿检测电路531、532、533、534、535和536中的每个被启用时,边沿检测电路531、532、533、534、535和536中的每个可以基于第一位d0和第二位d1检测输出数据信号ds1的相应的下降沿,以激活预加重控制信号pecs1和pecs2中的至少一个。例如,边沿检测电路531可以基于边沿检测启用信号eden_f1而被启用。例如,当边沿检测电路531被启用时,边沿检测电路531可以检测输出数据信号ds1从第四电压电平vl41被转变为第一电压电平vl11所处于的第一下降沿(例如,“11

”‑

》“00”)。例如,当第一下降沿被边沿检测电路531检测到时,边沿检测电路531可以激活预加重控制信号pecs1和pecs2两者。

[0116]

在发明构思的示例性实施例中,当输出数据信号ds1从最低电压电平(例如,第一电压电平vl11)和最高电压电平(例如,第四电压电平vl41)中的一个被转变为最低电压电平和最高电压电平中的另一个时,两个预加重控制信号pecs1和pecs2中的两者可以被激活。在其他情况下,预加重控制信号pecs1和pecs2中的仅一个可以被激活。

[0117]

图10a和图10b是示出根据发明构思的示例性实施例的包括在图9的边沿检测逻辑中的边沿检测电路的框图。

[0118]

参照图10a,边沿检测电路521可以包括nor(或非)门611、and(与)门613、延迟电路

615和复用器617。

[0119]

nor门611可以对第一位d0和第二位d1执行nor运算。and门613可以对第一位d0和二位d1执行and运算。延迟电路615可以延迟nor门611的输出。复用器617可以基于边沿检测启用信号eden_r1,输出延迟电路615的输出和and门613的输出中的一个作为第一预加重控制信号pecs1和第二预加重控制信号pecs2。例如,复用器617可以在边沿检测启用信号eden_r1被激活时输出延迟电路615的输出,并且可以在边沿检测启用信号eden_r1被去激活时输出and门613的输出。此外,当边沿检测启用信号eden_r1被激活时并且当输出数据信号ds1从第一电压电平vl11被转变为第四电压电平vl41所处于的第一上升沿被检测到时,复用器617可以输出激活的第一预加重控制信号pecs1和第二预加重控制信号pecs2。

[0120]

参照图10b,边沿检测电路524可以包括nor门621、and门623、延迟电路625和复用器627。将省略已经参照图10a描述的元件的描述。

[0121]

nor门621和延迟电路625可以分别与图10a中的nor门611和延迟电路615基本相同。and门623可以对第一位d0的反转位和第二位d1执行and运算。复用器627可以基于边沿检测启用信号eden_r4,输出延迟电路625的输出和and门623的输出中的一个作为第二预加重控制信号pecs2。例如,当边沿检测启用信号eden_r4被激活时并且当输出数据信号ds1从第二电压电平vl21被转变为第四电压电平vl41所处于的第四上升沿被检测到时,复用器627可以输出激活的第二预加重控制信号pecs2。在边沿检测电路524中,第一预加重控制信号pecs1可以不被生成或者可以始终被去激活。

[0122]

剩余的边沿检测电路522、523、525、526、531、532、533、534、535和536也可以被实现为检测对应的边沿,并且可以具有与图10a和图10b的配置相似的配置。

[0123]

图11a、图11b、图11c、图11d、图11e和图12是用于描述根据发明构思的示例性实施例的通过生成多电平信号的方法和发送器来执行的操作的示图。

[0124]

图11a、图11b、图11c、图11d和图11e是图7b中的部分“a”的放大图。在图11a、图11b、图11c、图11d和图11e中,左侧的曲线图示出了未应用根据发明构思的示例性实施例的选择性均衡化方案的情况,右侧的曲线图示出了应用了根据发明构思的示例性实施例的选择性均衡化方案的情况。

[0125]

参照图11a,在左侧的情况下,所有的边沿可以具有相同的转变时间tt1和tt2。在右侧的情况下,边沿检测电路521可以被启用,从第一电压电平vl11转变为第四电压电平vl41的第一上升沿(例如,“00

”‑

》“11”)的斜率可以增大,第一上升沿的转变时间可以从tt1减少到tt11。因此,眼eye31的抖动特性可以从jt_h0被提高到jt_h1。

[0126]

参照图11b,与图11a中的右侧的情况相比,在图11b中的右侧的情况下,边沿检测电路527可以被附加地启用,从第四电压电平vl41转变为第一电压电平vl11的第一下降沿(例如,“11

”‑

》“00”)的斜率可以进一步增大,第一下降沿的转变时间可以进一步减少。因此,眼eye11的抖动特性可以从jt_l0被进一步提高到jt_l2。

[0127]

参照图11c,与图11b中的右侧的情况相比,在图11c中的右侧的情况下,边沿检测电路522和532可以被附加地启用。如此,从第一电压电平vl11转变为第三电压电平vl31的第二上升沿(例如,“00

”‑

》“10”)的斜率和从第四电压电平vl41转变为第二电压电平vl21的第二下降沿(例如,“11

”‑

》“01”)的斜率可以进一步增大,第二上升沿的转变时间和第二下降沿的转变时间可以进一步减少。因此,眼eye21的抖动特性可以从jt_m0被进一步提高到

jt_m3。

[0128]

参照图11d,与图11c中的右侧的情况相比,在图11d中的右侧的情况下,边沿检测电路523、524、525、533、534和535可以被附加地启用。如此,从第一电压电平vl11转变为第二电压电平vl21的第三上升沿(例如,“00

”‑

》“01”)的斜率、从第二电压电平vl21转变为第四电压电平vl41的第四上升沿(例如,“01

”‑

》“11”)的斜率、从第二电压电平vl21转变为第三电压电平vl31的第五上升沿(例如,“01

”‑

》“10”)的斜率、从第四电压电平vl41转变为第三电压电平vl31的第三下降沿(例如,“11

”‑

》“10”)的斜率、从第三电压电平vl31转变为第一电压电平vl11的第四下降沿(例如,“01

”‑

》“01”)的斜率以及从第三电压电平vl31转变为第二电压电平vl21的第五下降沿(例如,“01

”‑

》“01”)的斜率可以进一步增大,并且第三上升沿的转变时间、第四上升沿的转变时间、第五上升沿的转变时间、第三下降沿的转变时间、第四下降沿的转变时间和第五下降沿的转变时间可以进一步减少。因此,眼eye11的抖动特性可以被进一步提高到jt_l4,眼eye31的抖动特性可以被进一步提高到jt_h4。

[0129]

参照图11e,在右侧的情况下,所有的边沿检测电路521、522、523、524、525、526、531、532、533、534、535和536可以被启用,所有的上升沿和下降沿的斜率可以增大,所有的上升沿和下降沿的转变时间可以减少。因此,所有的眼eye11、eye21和eye31的抖动特性可以从jt0被提高到jt5。

[0130]

参照图12,图11a、图11b、图11c、图11d和图11e中的右侧的情况在图7c的曲线图中分别被表示为情况1、情况2、情况3、情况4和情况5。如上所述,均衡化操作的目标和数量可以考虑通道的功耗和特性而设置。

[0131]

图13是示出根据发明构思的示例性实施例的图1中的改变两个或更多个驱动路径中的至少一个的驱动强度的示例的流程图。将省略已经参照图2描述的元件的描述。

[0132]

参照图1和图13,当改变两个或更多个驱动路径中的至少一个的驱动强度(图1的操作s200)时,图13中的操作s210、操作s230、操作s240和操作s250可以分别与图2中的操作s210、操作s230、操作s240和操作s250基本相同。

[0133]

当检测到输出数据信号上的两个或更多个目标边沿中的一个(操作s225:是)时,可以激活两个或更多个预加重控制信号中的至少一个(操作s230),并且可以基于激活的预加重控制信号而增大两个或更多个驱动路径中的至少一个的驱动强度,使得减少输出数据信号的针对检测到的目标边沿的转变时间(操作s240)。

[0134]

图2的示例可以与仅对一个边沿执行均衡化操作的图11a对应,图13的示例可以与对两个或更多个边沿执行均衡化操作的图11b、图11c、图11d和图11e对应。

[0135]

图14是用于描述根据发明构思的示例性实施例的通过生成多电平信号的方法而生成的数据信号的示图。将省略已经参照图7b描述的元件的描述。

[0136]

参照图14,示出了基于8电平方案(例如,pam8方案)生成的数据信号(例如,pam8信号)的不同的第一电压电平vl12、第二电压电平vl22、第三电压电平vl32、第四电压电平vl42、第五电压电平vl52、第六电压电平vl62、第七电压电平vl72和第八电压电平vl82,并且示出了数据信号的第一眼eye12、第二眼eye22、第三眼eye32、第四眼eye42、第五眼eye52、第六眼eye62和第七眼eye72。如上所述,均衡化操作可以仅对影响眼特性的一些边沿选择性地执行。

[0137]

图15是示出根据发明构思的示例性实施例的发送器的框图。将省略已经参照图8

描述的元件的描述。

[0138]

参照图15,发送器700包括复用器(mux)710、边沿检测逻辑720以及两个或更多个驱动路径740、750和760。发送器700还可以包括数据i/o垫780。复用器710、边沿检测逻辑720、驱动路径740、750和760以及数据i/o垫780可以分别与图8中的复用器510、边沿检测逻辑520、驱动路径540和550以及数据i/o垫580对应。

[0139]

在图15的示例中,输入数据dat2可以包括彼此不同的第一位d0、第二位d1和第三位d2,复用器710可以基于八相位时钟信号ck_8p将输入数据dat2划分为第一位d0、第二位d1和第三位d2。两个或更多个驱动路径740、750和760可以包括第一驱动路径740、第二驱动路径750和第三驱动路径760,第一驱动路径740基于第一位d0和第一预加重控制信号pecs1进行操作,第二驱动路径750基于第二位d1和第二预加重控制信号pecs2进行操作,第三驱动路径760基于第三位d2和第三预加重控制信号pecs3进行操作。输出数据信号ds2可以与图14中示出的数据信号对应,并且可以在一个单位时间间隔期间具有彼此不同的第一电压电平vl12、第二电压电平vl22、第三电压电平vl32、第四电压电平vl42、第五电压电平vl52、第六电压电平vl62、第七电压电平vl72和第八电压电平vl82中的一个。

[0140]

在发明构思的示例性实施例中,第一位d0可以是输入数据dat2的lsb,第二位d1可以是输入数据dat2的中心有效位(csb),第三位d2可以是输入数据dat2的msb。

[0141]

第一驱动路径740可以包括数据缓冲器(例如,第一数据缓冲器)741、驱动器电路(例如,第一驱动器电路)743和预加重驱动器电路(例如,第一预加重驱动器电路)745。第二驱动路径750可以包括数据缓冲器(例如,第二数据缓冲器)751、驱动器电路(例如,第二驱动器电路)753、驱动器电路(例如,第三驱动器电路)755和预加重驱动器电路(例如,第二预加重驱动器电路)757。第三驱动路径760可以包括数据缓冲器(例如,第三数据缓冲器)761、驱动器电路(例如,第四驱动器电路)763、驱动器电路(例如,第五驱动器电路)765、驱动器电路(例如,第六驱动器电路)767、驱动器电路(例如,第七驱动器电路)769和预加重驱动器电路(例如,第三预加重驱动器电路)771。数据缓冲器741、751和761的操作、分别生成驱动电流i1、i2、i3、i4、i5、i6和i7的驱动器电路743、753、755、763、765、767和769的操作以及生成电流ip1、ip2和ip3的预加重驱动器电路745、757和771的操作可以与参照图8描述的操作基本相同。

[0142]

尽管图15示出了用于增大驱动强度的配置730包括驱动路径740、750和760中所包括的预加重驱动器电路745、757和771,但发明构思不限于此。

[0143]

图16和图17是示出根据发明构思的示例性实施例的发送数据的方法的流程图。

[0144]

参照图16,在根据发明构思的示例性实施例的发送数据的方法中,基于第一输入数据生成作为多电平信号的第一输出数据信号(操作s1100)。基于第二输入数据生成作为多电平信号的第二输出数据信号(操作s1200)。分别通过第一通道和第二通道发送第一输出数据信号和第二输出数据信号(操作s1300)。

[0145]

参照图17,在根据发明构思的示例性实施例的发送数据的方法中,图17中的操作s1100和操作s1200可以分别与图16中的操作s1100和操作s1200基本相同。基于第n输入数据生成作为多电平信号的第n输出数据信号(操作s1400)。分别通过第一通道至第n通道发送第一输出数据信号至第n输出数据信号(操作s1500)。

[0146]

操作s1100、操作s1200和操作s1400中的每个可以基于参照图1至图15描述的根据

发明构思的示例性实施例的生成多电平信号的方法而被执行。

[0147]

例如,如上所述,两个或更多个驱动路径中的至少一个的驱动强度可以基于包括在第一输入数据中的两个或更多个位被改变,使得第一输出数据信号在其期间从第一电压电平被转变为第二电压电平的第一转变时间被改变。第一输出数据信号可以被生成,使得第一输出数据信号的第一转变时间被改变,并且第一输出数据信号在其期间从第一电压电平被转变为与第二电压电平不同的第三电压电平的第二转变时间被保持。

[0148]

相似地,两个或更多个驱动路径中的至少一个的驱动强度可以基于包括在第二输入数据中的两个或更多个位被改变,使得第二输出数据信号在其期间从第一电压电平被转变为第二电压电平的第三转变时间被改变。第二输出数据信号被生成,使得第二输出数据信号的第三转变时间被改变,并且第二输出数据信号在其期间从第一电压电平被转变为第三电压电平的第四转变时间被保持。

[0149]

作为另一示例,两个或更多个驱动路径中的至少一个的驱动强度可以基于包括在第二输入数据中的两个或更多个位被改变,使得第二输出数据信号在其期间从与第一电压电平不同的第四电压电平被转变为第二电压电平的第三转变时间被改变。第二输出数据信号可以被生成,使得第二输出数据信号的第三转变时间被改变,并且第二输出数据信号在其期间从第四电压电平被转变为第三电压电平的第四转变时间被保持。

[0150]

在发明构思的示例性实施例中,图16中的第一通道和第二通道的特性可以彼此基本相同,图17中的第一通道至第n通道的特性可以彼此基本相同。例如,所有的输出数据信号可以具有基本相同的波形(例如,图11a至图11e中的波形之一)。

[0151]

在发明构思的示例性实施例中,图16中的第一通道和第二通道的特性可以彼此不同,图17中的第一通道至第n通道的特性可以彼此不同。例如,考虑到通道的特性,输出数据信号可以具有不同的波形(例如,图11a至图11e中的波形之中的不同的波形)。

[0152]

在发明构思的示例性实施例中,图16和图17的发送数据的方法可以由根据发明构思的示例性实施例的存储器系统执行。例如,如参照图4a所述,输出数据信号可以由存储器控制器21(例如,由发送器25a、25b和25c)生成。作为另一示例,如参照图4b所描述,输出数据信号可以由存储器装置41(例如,由发送器45a、45b和45c)生成。

[0153]

图18a和图18b是示出根据发明构思的示例性实施例的存储器系统的框图。将省略已经参照图4a和图4b描述的元件的描述。

[0154]

参照图18a,存储器系统12包括存储器控制器22、存储器装置42以及多个通道31a、31b和31c。

[0155]

除了存储器装置42还包括眼监测器电路51a并且存储器控制器22还包括启用信号生成电路53a之外,存储器系统12可以与图4a的存储器系统11基本相同。

[0156]

眼监测器电路51a可以连接到多个通道31a、31b和31c,并且可以基于接收的输出数据信号ds11、ds21和ds31来生成表示通道31a、31b和31c的特性的特性数据cdat1。启用信号生成电路53a可以基于特性数据cdat1生成边沿检测启用信号eden。基于通道31a、31b和31c的特性,可以实时地确定均衡化操作将要对哪个边沿执行。

[0157]

参照图18b,存储器系统13包括存储器控制器23、存储器装置43以及多个通道31a、31b和31c。

[0158]

除了存储器控制器23还包括生成特性数据cdat2的眼监测器电路51b并且存储器

装置43还包括启用信号生成电路53b之外,存储器系统13可以与图4b的存储器系统11基本相同。眼监测器电路51b和启用信号生成电路53b可以分别与图18a中的眼监测器电路51a和启用信号生成电路53a基本相同。

[0159]

在发明构思的示例性实施例中,眼监测器电路51a和51b以及启用信号生成电路53a和53b可以针对每个通道被提供和/或可以设置在存储器控制器和存储器装置外部。

[0160]

图19是示出根据发明构思的示例性实施例的计算系统的框图。

[0161]

参照图19,计算系统1300包括处理器1310、系统控制器1320和存储器系统1330。计算系统1300还可以包括输入装置1350、输出装置1360和存储装置1370。

[0162]

存储器系统1330包括多个存储器装置1334以及用于控制存储器装置1334的存储器控制器1332。存储器控制器1332可以被包括在系统控制器1320中。存储器系统1330可以是根据发明构思的示例性实施例的存储器系统,并且可以执行根据发明构思的示例性实施例的生成多电平信号的方法和发送数据的方法。

[0163]

处理器1310可以执行各种计算功能,诸如,运行用于执行特定计算或任务的特定软件指令。处理器1310可以经由处理器总线连接到系统控制器1320。系统控制器1320可以经由扩展总线连接到输入装置1350、输出装置1360和存储装置1370。如此,处理器1310可以使用系统控制器1320来控制输入装置1350、输出装置1360和存储装置1370。

[0164]

图20是示出根据发明构思的示例性实施例的通信系统的框图。

[0165]

参照图20,通信系统2000包括第一通信装置(例如,通信装置1)2100、第二通信装置(例如,通信装置2)2200和通道2300。

[0166]

第一通信装置2100包括第一发送器2110和第一接收器2120。第二通信装置2200包括第二发送器2210和第二接收器2220。第一发送器2110和第一接收器2120通过通道2300连接到第二发送器2210和第二接收器2220。在发明构思的示例性实施例中,第一通信装置2100和第二通信装置2200中的每个可以包括多个发送器和多个接收器,通信系统2000可以包括用于将多个发送器和多个接收器连接的多个通道。

[0167]

发送器2110和2210可以是根据发明构思的示例性实施例的发送器,并且可以执行根据发明构思的示例性实施例的生成多电平信号的方法和发送数据的方法。

[0168]

发明构思可以应用于包括存储器装置和存储器系统的各种装置和系统。例如,发明构思可以应用于诸如以下的系统:个人计算机(pc)、服务器计算机、数据中心、工作站、移动电话、智能电话、平板计算机、膝上型计算机、个人数字助理(pda)、便携式多媒体播放器(pmp)、数码相机、便携式游戏机、音乐播放器、摄录像机、视频播放器、导航装置、可穿戴装置、物联网(iot)装置、万物联网(ioe)装置、电子书阅读器、虚拟现实(vr)装置、增强现实(ar)装置、机器人装置、无人机等。

[0169]

在根据发明构思的示例性实施例的生成多电平信号的方法、发送数据的方法以及发送器和存储器系统中,选择性的或适应性的均衡化方案可以被实现。在选择性均衡化方案中,现有的或常规的驱动路径可以按原样被使用,均衡化操作可以仅当在输出数据信号上发生特定电平转变时被执行。换言之,均衡化操作可以仅对能够在多电平信号上发生的一些电平转变执行。因此,与均衡化操作对所有的电平转变执行的情况相比,可以降低功耗,并且可以有效地提高或增强信号特性。

[0170]

尽管已经参照发明构思的示例性实施例示出和描述了发明构思,但对本领域普通

技术人员而言将清楚的是,在不脱离如由所附权利要求阐述的发明构思的精神和范围的情况下,可以对其作出形式上和细节上的各种修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。