叠对测量目标设计

1.相关申请案的交叉参考

2.本技术案主张于2019年7月24日提出申请且被指派给美国申请案第62/877,898号的临时专利申请案的优先权,所述临时专利申请案的公开内容特此以引用方式并入。

技术领域

3.本发明涉及一种半导体计量。

背景技术:

4.半导体制造产业的演化对合格率管理且特定来说对计量及检验系统提出更高要求。临界尺寸不断收缩,但产业需要减少实现高合格率、高价值生产的时间。最小化从检测合格率问题到解决所述问题的总时间确定半导体制造商的投资回报率。

5.制作半导体装置(例如逻辑及存储器装置)通常包含使用许多制作过程来处理半导体晶片以形成半导体装置的各种特征及多个层级。举例来说,光刻是涉及将图案从光罩转印到布置于半导体晶片上的光致抗蚀剂的半导体制作工艺。半导体制作工艺的额外实例包含但不限于晶片清洁、热氧化、化学机械抛光(cmp)、蚀刻、介电及导电薄膜沉积、选择性外延生长、离子植入及快速热退火(rtp)。制作于单个半导体晶片上的多个半导体装置的布置可被分离成个别半导体装置。

6.半导体装置内的结构的相对位置被称为叠对(ovl)。晶片上的连续经图案化层之间的叠对误差的测量是集成电路制造中的过程控制技术。叠对准确度通常关于第一经图案化层相对于安置于其上方或下方的第二经图案化层如何准确地对准的确定以及第一图案相对于安置于同一层上的第二图案如何准确地对准的确定。

7.在半导体制造过程期间的各种步骤处使用计量过程来监测并控制一或多个半导体层过程。叠对误差是经监测及经控制的特性中的一者。叠对误差通常利用具有形成于工件(例如,半导体晶片)的一或多个层上的结构的叠对目标来确定。如果两个层或图案经适当地形成,那么一个层或图案上的结构相对于另一层或图案上的结构往往是对准的。如果两个层或图案并非经适当地形成,那么一个层或图案上的结构相对于另一层或图案上的结构往往是偏移或不对准的。叠对误差是在半导体制作过程的不同阶段所使用的图案中的任一者之间的不对准。

8.叠对计量目标经印刷以测量两个或更多个层之间的配准。晶片上的结构可呈光栅形式,且这些光栅可以是周期性的。如果两个层或图案经适当地形成,那么一个层或图案上的结构相对于另一层或图案上的结构可以是对准的。

9.叠对测量在集成电路制造过程中可以是重要的,这是因为其确保掩模层彼此对准。主要使用光学仪器对经设计测量目标执行叠对测量。设计测量目标通常位于晶片上的裸片之间的切割线上。随着特征大小深度地按比例调整成纳米范围,从切割线中的测试图案测量的叠对有时与真实装置的叠对并不相关,这是因为所述测试图案之间的图案差异及特征大小差异。这可导致集成电路制造中的合格率损失。

10.基于扫描电子显微镜(sem)图像的叠对测量是用于进阶纳米节点处的集成电路过程控制的选项。图1展示sem系统及sem图像的示意图,所述sem图像具有可用于叠对测量的先前层(层1)及当前层(层2)两者。电子束图像已用于在蚀刻装置区域之后测量叠对。显影后检验(adi)叠对测量在不类似真实装置的特定设计的叠对目标上的切割线中使用光学系统。另一先前方法使用高着陆能量(le)电子束以在adi处测量装置上的叠对方向。

11.叠对计量随着特征大小收缩而变得更加重要。光学叠对目标上的通常使用的光学计量可不能够与装置的叠对结果相关,这是因为光学目标的特征大小通常大于真实装置,且光学目标通常位于裸片的切割线中,远离真实装置。测试具有sem的装置上的图案蚀刻后叠对测量通常称作蚀刻后检验(aei)。装置测量上的aei sem-ovl与光刻过程后光学叠对测量(通常称作adi)之间的差异称作非零偏移(nzo)。进阶纳米技术节点的更多集成电路制造设施是使用nzo来校准及控制叠对的。随着技术进一步进展,如果可能,那么集成电路制造商可需要装置上在adi处的sem叠对测量。然而,使用adi层,先前层被掩埋在范围介于从数十纳米到数百纳米(取决于装置及层)的一或多个膜下边。在aei处,先前层通常已通过蚀刻工艺暴露。先前层图案可位于距表面数百纳米的沟槽或孔的底部处,例如当前层图案所位于的地方。为了利用sem测量叠对,电子需要具有足够能量以到达经掩埋图案,其中束斑点紧密得足以分辨所述经掩埋图案且仍具有足够能量以从样品表面返回。为分辨所述经掩埋图案,图案材料与背景材料之间应存在足够对比度。电子束在进入样品之后分散。电子束前进得越深,分散直径就越大。初级束的经增加着陆能量可帮助减少束分散,但高能量电子容易穿透经掩埋图案且减少经掩埋图案的对比度。对于一些动态随机存取存储器(dram)adi层,先前层被深深地掩埋且电子束在空间上分散太多。因此,先前层图案无法在装置区域中进行分辨且在装置区域中测量叠对可为困难的。

12.切割线中的目标上的adi光学叠对测量有时与真实装置中的叠对误差并不相关。集成电路制造商需要等待基于sem的装置上叠对测量结果来进行校正。对于电子束adi装置上叠对测量,光致抗蚀剂将被电子束损坏且高能电子也可能损坏集成电路装置。来自电子束的损坏可摧毁装置。

13.叠对测量通常在光致抗蚀剂蚀刻之后执行。如果光致抗蚀剂未对准那么就对晶片进行返工,但光致抗蚀剂图案在其被电子束命中时可受影响。因此,可执行光学成像以避免对装置的损坏。然而,用于光学成像的叠对目标必须大于在电子束成像中所使用的那些叠对目标。空间在半导体晶片上有限,而这会使用更多空间。

14.随着集成电路装置变得更复杂,需要测量的经改进目标设计及方法。

技术实现要素:

15.在第一实施例中,提供一种装置。所述装置包含:装置区域中的基垫,所述基垫具有四个侧;及第一层中的多个延伸部,所述多个延伸部延伸超出所述基垫的所述侧。所述基垫包含至少第一光致抗蚀剂层及安置于所述第一层上的第二光致抗蚀剂层。所述第一层中的所述延伸部中的每一者包含第一层计量目标。所述第一层计量目标具有小于所述基垫的所述第二层中的装置间距的松弛间距。所述第二层可界定孔口图案。所述第二层覆盖每一第一层计量目标的至少一部分。

16.所述装置区域可以是dram装置的一部分。

17.所述装置可包含所述第二层的多个延伸部。所述第二层的所述延伸部中的每一者是所述第二层在所述基垫的所述四个侧中的一者的边缘处的一部分。所述第二层中的所述延伸部可延伸超出所述基垫的所述侧。

18.所述基垫在高度及宽度上可小于60μm。所述第一层的所述延伸部可小于所述基垫。

19.所述装置可包含安置于所述第二层的与所述第一层相对的侧上的第三层。所述第三层可包含所述第三层的多个延伸部。所述第三层的所述延伸部中的每一者可位于所述基垫的所述四个侧中的一者的边缘处。所述第三层可界定多个孔口。

20.所述松弛间距可以是所述装置间距的四分之一。在例子中,所述松弛间距是所述装置间距的八分之一。所述松弛间距可大于40nm。

21.在第二实施例中,提供一种方法。所述方法包含提供装置。所述装置包含:装置区域中的基垫,所述基垫具有四个侧;及第一层中的多个延伸部,所述多个延伸部延伸超出所述基垫的所述侧。所述基垫包含至少第一光致抗蚀剂层及安置于所述第一层上的第二光致抗蚀剂层。所述第一层中的所述延伸部中的每一者包含第一层计量目标。所述第一层计量目标具有小于所述基垫的所述第二层中的装置间距的松弛间距。所述第二层界定孔口图案。所述第二层覆盖每一第一层计量目标的至少一部分。

22.第一层叠对目标中的至少一者的图像是利用电子束计量工具获得的。所述获得包含同时获得所述第二层的次级电子图像及获得具有所述松弛间距的所述第一层的背向散射电子图像。使用处理器,利用图像执行计量。所述计量可以是叠对或临界尺寸。

23.所述第二层的所述次级电子图像可与所述第一层的所述背向散射电子图像相距非零距离。所述第二层的所述次级图像可与所述侧中的最靠近者相距非零距离。

24.所述松弛间距可不由所述电子束计量工具分辨且所述装置间距可由所述电子束计量工具分辨。

25.所述装置区域可以是dram装置的一部分。

26.所述方法可包含具有所述第二层的多个延伸部的装置。所述第二层的所述延伸部中的每一者是所述第二层在所述基垫的所述四个侧中的一者的边缘处的一部分。所述第二层的延伸部延伸超出所述基垫的所述侧。

27.所述装置可包含安置于所述第二层的与所述第一层相对的侧上的第三层。所述第三层包含所述第三层的多个延伸部。所述第三层的所述延伸部中的每一者是所述第三层在所述基垫的所述四个侧中的一者的边缘处的一部分。所述第三层界定多个孔口。所述方法进一步包括:获得具有所述孔口图案的第三层的次级电子图像;及获得所述第一层的背向散射电子图像,可同时获得所述次级电子图像及所述背向散射电子图像。

28.所述基垫在高度及宽度上可小于60μm。所述第一层的所述延伸部可小于所述基垫。所述松弛间距可大于40nm。

29.一种电子束计量工具可用于第二实施例的方法。

附图说明

30.为了更全面地理解本发明的性质及目的,应参考结合附图做出的以下详细说明,在附图中:

31.图1是图解说明使用sem的叠对测量的图式;

32.图2是第一层中的装置附接的叠对目标设计的实施例;

33.图3是第二层中的装置附接的叠对目标设计的实施例;

34.图4是第三层中的装置附接的叠对目标设计的实施例;

35.图5展示第一层与第二层之间的边界区;

36.图6图解说明示范性间距;

37.图7图解说明图6的在自对准四重图案化之后的间距;

38.图8图解说明当前层图案对经掩埋先前层图案;

39.图9图解说明当前层的aci对图8的经掩埋先前层图案;

40.图10图解说明第二层对先前层图案的另一实例;

41.图11图解说明第三层对图10的第二层及第一层;

42.图12是第二层中的装置附接的叠对目标设计的另一实施例;及

43.图13是根据本公开的方法的实施例的流程图。

具体实施方式

44.尽管将依据某些实施例描述所主张标的物,但包含不提供本文中所陈述的全部益处及特征的实施例的其它实施例也在本发明的范围内。可在不脱离本发明的范围的情况下做出各种结构、逻辑、过程步骤及电子改变。因此,本发明的范围仅通过参考所附权利要求书来界定。

45.本文中所公开的实施例利用叠对计量解决数个问题。首先,光学叠对目标通常定位成远离装置区域,且光学叠对目标设计不同于真实装置布局。设计的距离及差异有助于光学叠对测量与真实装置中的叠对值之间的相关问题。本文中所公开的实施例使得能够在adi叠对测量期间在真实装置图案中通过基于sem的叠对测量系统来经掩埋先前层成像。经掩埋先前图案的间距距致密真实装置图案是松弛的,这意味着其可相对地成像,以用于叠对测量。利用大视野(fov)sem系统,可在不移动载台的情况下测量使用本文中所公开的实施例的层的所有四个目标。这允许在x方向及y方向两者上的高效叠对测量。

46.本文中所公开的实施例可实现使用实际装置布局来形成电子束叠对测量目标以形成当前层(其是在adi步骤处的光致抗蚀剂图案),且在具有松弛间距的外围处延伸到经掩埋先前层。因此,电子束可分辨图案,即使在高能量电子束穿透深入到样品中以到达先前层时分辨率已经折衷。这可与自对准四重图案化(saqp)一起使用,这是因为多个图案化辅助层需要在光致抗蚀剂涂布及图案化之前沉积。

47.saqp可在一行中应用自对准双重图案化(sadp)两次以实现有效间距四等分。利用sadp,通过膜在先前图案上的沉积或反应,后续接着蚀刻以移除水平表面上的所有膜材料来形成间隔件。这在侧壁上仅留下材料。通过移除原始经图案化特征,仅留下间隔件。然而,由于对于每条线存在两个间隔件,因此线密度现在已加倍。当saqp应用sadp两次时,临界尺寸(cd)及特征之间的间隔各自由第一间隔件或第二间隔件界定。

48.图2是第一层中的装置附接的叠对目标设计的实施例。所述第一层包含基垫100中的装置阵列,所述基垫至少部分地由光致抗蚀剂制成。基垫100中的每一者具有四个侧,但具有较多侧的多边形基垫是可能的。基垫100还可被称为块。“基垫”可以是存储器装置的一

部分(例如dram结构),但本文中所公开的实施例可应用于具有类似形状或装置结构的其它设计。第一层中的基垫100中的至少一者包含延伸部101。延伸部101各自位于基垫100的四个侧中的一者的边缘处。可使用saqp来形成基垫100及/或延伸部101。

49.延伸部101中的每一者包含第一层计量目标102。第一层计量目标102可包含通常定向在x方向或y方向上的结构(例如,线或光栅),尽管其它定向是可能的。

50.虽然在图2中图解说明四个延伸部101,但仅可使用两个。可使用具有y方向上的计量目标结构的一个延伸部101以及具有x方向上的计量目标结构的一个延伸部101。还可使用具有x方向及y方向上的计量目标结构的单个延伸部101。

51.图3是第二层中的装置附接的叠对目标设计的实施例。基垫200上的装置阵列包含第二层。第二层也至少部分地由光致抗蚀剂制成。第二层安置于第一层上。第二层可界定孔口图案。孔口可以是装置结构的一部分。

52.基垫100及/或第一层计量目标102可具有小于基垫200或延伸部201的装置间距的松弛间距。基垫100及/或第一层计量目标102的间距可以是松弛的,这是因为所述间距是掩埋的。松弛间距可帮助通过装置层的进行分辨。举例来说,第一层计量目标102可具有是装置间距(例如在图11中)的四分之一或是装置间距(例如在图8中)的八分之一的松弛间距。

53.第二层的延伸部201各自位于基垫200的四个侧中的一者的边缘处。延伸部201具有基垫200的装置间距。

54.如图3中所展示,延伸部101延伸超出基垫200。超出基垫200的延伸部101并非由基垫200或延伸部201覆盖。第一层计量目标102中的至少一些计量目标由基垫200覆盖。少于全部的第一层计量目标102由基垫200覆盖。

55.图4是第三层中的装置附接的叠对目标设计的实施例。第三层也至少部分地由光致抗蚀剂制成。第三层安置于第二层上。第三层可界定孔口图案。

56.第三层的延伸部301各自位于基垫300的四个侧中的一者的边缘处。延伸部301具有基垫300的装置间距。

57.如图4中所展示,延伸部201延伸超出基垫300。超出基垫300的延伸部201并非由基垫300、延伸部101或延伸部201覆盖。第一层计量目标102中的至少一些计量目标由基垫300覆盖。少于全部的第一层计量目标102由基垫300覆盖。

58.虽然仅展示三个层,但四个层、五个层或多于五个层是可能的。所述层中的每一者可包含基垫及延伸部,所述延伸部类似于第一层、第二层或第三层中所描述的那些延伸部。

59.延伸部201及延伸部301可包含较之稍后形成的层具有松弛间距的计量目标。

60.本文中所公开的实施例的至少第二层及第三层是真实装置。因此,延伸部被定位成接近真实装置。装置的设计的改变可并非是必需的。

61.延伸部101的松弛间距可以是基垫200或基垫300中的装置的图案间距的至少四倍。举例来说,松弛间距可大于40nm或大于100nm。

62.延伸部101、延伸部201及延伸部301延伸超出基垫300到装置结构之间的区中。

63.在例子中,基垫100在高度及宽度上是60μm或更少。在另一例子中,基垫100在高度及宽度上小于50μm。基垫200及基垫300与基垫100可以是大约相同大小。各种计量目标具有小于基垫100的尺寸的尺寸。sem扫描场在尺寸上通常小于2μm。

64.图5展示第一层100与第二层200之间的边界区。第二层的基垫200定位于具有第一

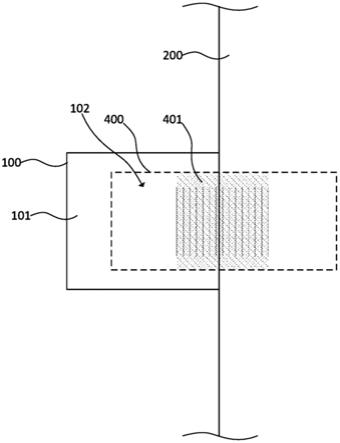

层计量目标102的第一层100之上。电子束的扫描场400(用虚线展示)可使基垫200的延伸部101及装置阵列两者成像。然而,扫描区域可排除位于基垫200与延伸部101之间的边缘处的区401(用影线展示)。将区401排除可避免负载效果。举例来说,扫描场400可以是1μm乘以2μm且区401可以是大约1μm乘以大约1μm。

65.如用图5所展示,可使第一层100及第二层200同时成像。第一层计量目标102于扫描场400中成像。第一层计量目标102中的某一部分是在第二层200之下。因此,通过第二层200中的孔口使第二层200之下的第一层计量目标102成像。这展示于图8中。

66.当制作图2到4的结构时,光刻工艺图案化装置区域同时清除外围区域中的光致抗蚀剂。如图5中所展示,电子束可使装置区域及外围区域两者同时成像。

67.图2到5中的叠对目标的装置区域可以是以下各项的一部分:dram装置、静态随机存取存储器(sram)装置、磁性随机存取存储器(mram)装置或其它存储器装置。逻辑装置或其它集成电路装置也可受益于本文中所公开的实施例。

68.图6到8的设计是用于dram作用区域(aa)形成。图6展示线450右边的致密单元区域及线450左边的松弛间距451的布局。线450右边的区域具有装置间距452。举例来说,松弛间距451可以是装置间距452的两倍。在例子中,装置间距452是实际装置结构且松弛间距451是与具有不同间距的装置间距452类似的结构,以用于叠对测量。

69.图7展示在saqp之后的先前层图案。图8图解说明右边的当前层图案及左边的经掩埋先前图案,所述经掩埋先前图案具有来自图7的松弛间距。在450右边具有孔口的光致抗蚀剂是在通过孔口且在450左边看的在先前图案上方的当前层图案。孔口可允许蚀刻工艺切割先前图案以形成dram装置的最终作用区域。为执行叠对,将第一层计量目标与第二层的装置结构进行比较。因此,将第一层计量目标的松弛间距与第二层的装置间距进行比较,例如通过第二层中的孔口。

70.sem的次级电子(se)图像可用于获得图像且以高分辨率来测量当前层(例如,基垫200),并且最小化来自当前层下边的先前层的干扰。同时,sem的背向散射电子(bse)图像可用于使具有松弛间距的经掩埋先前图案(例如,延伸部101)成像。图9图解说明当前层的aci对图8的经掩埋先前层图案。

71.图10及11展示具有三个层的实例。图10图解说明第二层对先前层图案的另一实例。线表示第一层的间距。块表示通过第二层中的孔口成像的区域。在例子中,图10图解说明图3的下部块201。

72.图11图解说明第三层对图10的第二层及第一层。垂直矩形表示第三层。当比较三个层的叠对时,可将第三层的装置间距与第二层的装置间距进行比较。可将第一层的松弛间距与第二层的装置间距或第三层的装置间距进行比较。

73.图12是第二层中的装置附接的叠对目标设计的另一实施例。延伸部101与延伸部201的松弛间距位于原始装置区域内部。注意,表示原始装置区域的虚线框。原始装置区域与图12中展示的其它基垫大小相同,尽管不同装置区域是可能的。在图12的实施例中,延伸部101及延伸部201是装置区域的延伸部或者是从当前层的拉回部。图12的实施例将减少对邻近基垫的外围电路的效果。

74.先前,不同于真实装置,光学目标设计有图案。这些光学目标被放置于切割线中,远离真实装置。不同于先前光学目标,本文中所公开的实施例将真实装置布局用于光致抗

蚀剂图案及经掩埋先前层,所述经掩埋先前层也是具有松弛间距的与外围装置相似的装置。所述经掩埋先前层可放置成靠近真实装置。装置可具有致密、重复图案且可定位成彼此接近,这减少了误差。这些目标上的叠对及临界尺寸均匀性(cdu)测量可与真实装置中的叠对值相关。

75.因此,本文中所公开的实施例可使用装置区域中的整个基垫的装置布局来形成多个计量目标以测量并控制adi层中的光刻过程。这可用于测量例如叠对及cd等参数。cd测量了可位于单个层中的两个点之间的距离。叠对测量了两个层中的结构之间的对准,这可通过使用算法寻找每一层的重心而确定。可比较这些重心。

76.使用真实装置图案或装置相似图案的目标可获得装置有关或装置相关的测量结果。对于基于电子束的叠对计量,真实装置层可用于当前层。先前层图案化中的具有松弛间距的装置相似布局可定位于基垫的一或多个侧处,例如在装置阵列基垫的所有四个侧上。

77.半导体制造商可将目标设计成装置布局。电子束叠对系统可用于在adi步骤期间成像及测量叠对。

78.图13是方法500的实施例的流程图。在501处提供装置。叠对目标可位于基垫的延伸部中。所述基垫可以是具有四个侧的装置区域,例如图3中所展示的基垫。所述基垫可包含至少第一光致抗蚀剂层及安置于第一层上的第二光致抗蚀剂层。叠对目标还包含多个第一层计量目标,例如在延伸部中。第一层计量目标中的每一者是第一层在基垫的四个侧中的一者的边缘处的一部分。第一层计量目标具有小于基垫的装置间距的松弛间距。第二层界定孔口图案。叠对目标具有通常在x方向及y方向两者上延伸的结构。

79.在502处获得利用电子束计量工具的第一层叠对目标的图像。获得图像包含同时获得第二层的se图像及获得具有松弛间距的第一层的bse图像。

80.在503处利用图像执行计量。所述计量可以是叠对或临界尺寸。举例来说,可在第一层与第二层、第二层与第三层或第三层与第一层之间测量叠对。

81.在例子中,第二层的次级电子图像与第一层的背向散射电子图像相距非零距离。第二层的次级图像与基垫的侧中的最靠近者相距非零距离。举例来说,图5展示矩形扫描场。第二层的次级电子图像通过经排除区与第一层的背向散射电子图像分离。

82.松弛间距可不由电子束计量工具分辨。装置间距可由电子束计量工具分辨。

83.叠对目标可包含第二层的多个延伸部。第二层的延伸部中的每一者是第二层在基垫的四个侧中的一者的边缘处的部分。第二层的延伸部延伸超出基垫的侧。

84.叠对目标可包含第三层,像图4中所图解说明那样。所述第三层安置于第二层的与第一层相对的侧上。第三层包含第三层的多个延伸部。第三层的延伸部中的每一者是第三层在基垫的四个侧中的一者的边缘处的一部分。第三层界定多个孔口。执行计量可包含:获得具有孔口图案的第三层的次级电子图像;及获得具有松弛间距的第一层的背向散射电子图像,所述获得可同时发生。

85.第二层的延伸部及第三层的延伸部可任选地包含可具有松弛间距或装置间距的计量目标。

86.电子束计量工具可用于执行方法500。电子束计量工具可与处理器电子通信,所述处理器经组态以发送用于成像的指令及/或对所得图像执行计量。这可包含使用个人计算机脑系统、图像计算机、大型计算机系统、工作站、网络器具、互联网器具或其它装置。

87.尽管已关于一或多个特定实施例描述本公开,但应理解可在不脱离本发明的范围的情况下执行本发明的其它实施例。因而,本公开被视为仅受所附权利要求书及其合理阐释限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。