1.本发明涉及通信技术领域,具体涉及一种具有帧计数功能的跨时钟域数据处理方法。

背景技术:

2.在利用fpga进行系统设计时,为了提高系统的稳定性和可靠性一般都采用同步设计方法。同步设计方法是整个系统都在时钟的作用下工作。对于只有一个时钟的单时钟域数据处理系统,所有的数据都在同一个时钟的作用下工作,不存在跨时钟域处理问题。对于复杂的系统为了满足系统设计需求一般存在多个时钟域,当数据从一个时钟域产生需要传递到另外一个时钟域使用时,若数据传输不满足寄存器的时序要求就会产生亚稳态,产生亚稳态后寄存器的输出端在状态稳定之前可能出现毛刺、震荡或固定在某一个电压值等问题。当数据到达新的时钟域后,有的数据会被判断为0有的会被判断为1,造成数据在新的时钟域下逻辑混乱,从而引起系统数据传输错误。

3.目前跨时钟域的处理方法主要有:

①

增加两级寄存器:该方法主要适用于单bit的数据,而对于多bit的数据不适用。当多bit的数据都增加两级寄存器后,不同bit的数据延迟可能不同,对低速的数据传输没有问题,但对于高速的数据传输可能会引起亚稳态。此外,对于单bit增加两级寄存器的跨时钟域处理方式也不能完全消除亚稳态。

②

增加异步双口ram:该方法是目前应用最广泛的跨时钟处理方式,主要适用于多bit数据的跨时钟域处理;一般采用一大块连续的ram循环存储数据,当有一帧数据要写入到连续的ram时,系统首先产生并记录要写入一帧数据的开始地址,当一帧数据写入完成后记录数据写入的结束地址,同时将存储这帧数据ram的开始地址和结束地址存储在两个寄存器数组中,当系统检测到有数据需要读出时,从寄存器数组中取出数据的开始地址和结束地址,根据取到的开始和结束地址从ram中读取相应的数据。由于采用寄存器数组来存储一帧数据的开始地址和结束地址,当系统内有连续的多包数据要存储时,后面数据的开始地址和结束地址可能会覆盖掉没有读出数据的开始地址和结束地址,从而造成链路上的数据错误。

技术实现要素:

4.本发明所要解决的是的跨时钟域数据处理系统容易引起亚稳态从而造成链路上的数据错误的问题,提供一种具有帧计数功能的跨时钟域数据处理方法。

5.为解决上述问题,本发明是通过以下技术方案实现的:

6.具有帧计数功能的跨时钟域数据处理方法,包括步骤如下:

7.1)数据写入过程:

8.步骤1.1、在空闲状态下,系统判断当前是否有数据帧写入请求:

9.如果没有数据帧写入请求时,则保持空闲状态;

10.如果有数据帧写入请求时,则根据上次数据帧写入的结束地址加载本次数据帧写入的开始地址,然后将本次数据帧写入数据缓存模块中,在本次数据帧写入的过程中,数据

缓存模块的地址在每个写时钟周期进行加1操作;当本次数据帧写入数据缓存模块结束后,将数据缓存模块的当前地址作为本次数据帧写入的结束地址,并执行步骤1.2;

11.步骤1.2、根据本次数据帧写入的开始地址和本次数据帧写入的结束地址判断本次写入的数据帧是否满足预定的数据帧长度:

12.如果数据帧长度不满足要求,则将本次数据帧作为不合格数据帧丢弃,并进入空闲状态;

13.如果数据帧长度满足要求,则先将本次数据帧写入的开始地址和数据帧写入的结束地址进行拼接,并将拼接完的地址数据写入地址存储模块;同时,将数据缓存模块的有效帧计数器进行加1操作;再将当前数据缓存模块的地址加1作为下次数据帧写入的开始地址,最后回到空闲状态;

14.2)数据读出过程:

15.步骤2.1、在空闲状态下,系统判断当前是否有数据帧读出请求:

16.如果没有数据帧读出请求时,则保持空闲状态;

17.如果有数据帧读出请求时,则进一步判断数据缓存模块的有效帧计数器的计数值是否等于0:

18.若数据缓存模块的有效帧计数器的值等于0,则说明数据缓存模块中没有要读取的数据帧,则保持空闲状态;

19.若数据缓存模块的有效帧计数器的值大于0,则从地址存储模块中读出一个地址数据,并将该地址数据拆分为本次数据帧读出的开始地址和本次数据帧读出的结束地址,并执行步骤2.2;

20.步骤2.2、根据本次数据帧读出的开始地址和本次数据帧读出的结束地址判断本次读出的数据帧是否满足预定的数据帧长度:

21.如果数据帧长度不满足要求,则放弃本次读操作,并进入空闲状态;

22.如果数据帧长度满足要求,则根据本次数据帧读出的开始地址从数据缓存模块中读出本次数据帧,在本次数据帧读出的过程中,数据缓存模块的地址在每个读时钟进行加1操作;当数据缓存模块的地址等于本次数据帧读出的结束地址时,停止本次数据帧的读取;同时,将数据缓存模块的有效帧计数器进行减1操作;最后进入帧间隔延时,当达到设定的帧间隔延时后,回到空闲状态。

23.上述方案中,地址存储模块为fifo先进先出存储器。

24.与现有技术相比,本发明具有如下特点:

25.1、开辟一大块ram作为数据缓存模块,将数据循环的写入数据缓存模块中;

26.2、采用一个地址存储模块(fifo先进先出存储器)来存储每帧数据在数据缓存模块中的开始地址和结束地址,这样就保证当有连续的多帧数据(数据帧的个数小于fifo的深度)写入时,后面写入数据的开始地址和结束地址不会覆盖掉前面数据的开始地址和结束地址;

27.3、采用帧计数功能,当一帧数据写入数据缓存模块且地址写入地址存储模块后有效帧计数器加1,当一帧从数据缓存模块中成功读出后,有效帧计数器减1,这样就能实时监测数据缓存模块中有多少帧数据没有读出。当有效帧计数器为0时,数据缓存模块中没有要读出的数据,当有效帧计数器大于0时,说明数据缓存模块中有可读出的数据。数据读取过

程:系统先从地址存储模块中读取一帧数据的开始地址和结束地址,根据读出的开始地址和结束地址从数据缓存模块中读出相应的数据帧。

附图说明

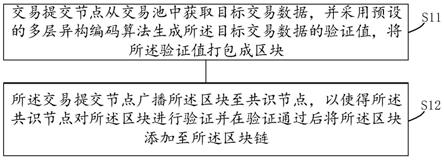

28.图1为具有帧计数功能的跨时钟域数据处理系统的数据写入流程图。

29.图2为具有帧计数功能的跨时钟域数据处理系统的数据读出流程图。

具体实施方式

30.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实例,对本发明进一步详细说明。

31.一种具有帧计数功能的跨时钟域数据处理方法,包括步骤如下:

32.步骤1、数据写入过程,如图1所示:

33.步骤1.1、在空闲状态下,系统判断当前是否有数据帧写入请求:

34.如果没有数据帧写入请求时,则保持空闲状态;

35.如果有数据帧写入请求时,则根据上次数据帧写入的结束地址加载本次数据帧写入的开始地址,然后将本次数据帧写入数据缓存模块中,在本次数据帧写入的过程中,数据缓存模块的地址在每个写时钟周期进行加1操作;当本次数据帧写入数据缓存模块结束后,将数据缓存模块的当前地址作为本次数据帧写入的结束地址,并执行步骤1.2;

36.步骤1.2、根据本次数据帧写入的开始地址和本次数据帧写入的结束地址判断本次写入的数据帧是否满足预定的数据帧长度,即通过将本次数据帧写入的结束地址减本次数据帧写入的开始地址,得到本次写入的数据帧的数据个数,通过判断数据个数,将不合格的数据帧丢弃;如:以太网最小要求包长为64个字节,如果写入的数据长度小于64字节,认为是一个不合格的数据帧将被丢弃:

37.如果数据帧长度不满足要求,则将本次数据帧作为不合格数据帧丢弃,并进入空闲状态;

38.如果数据帧长度满足要求,则先将本次数据帧写入的开始地址和数据帧写入的结束地址进行拼接,并将拼接完的地址数据写入地址存储模块(fifo先进先出存储器);同时,将数据缓存模块的有效帧计数器进行加1操作;再将当前数据缓存模块的地址加1作为下次数据帧写入的开始地址,最后回到空闲状态;

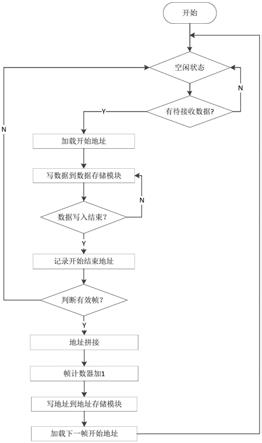

39.步骤2、数据读出过程,如图2所示:

40.步骤2.1、在空闲状态下,系统判断当前是否有数据帧读出请求:

41.如果没有数据帧读出请求时,则保持空闲状态;

42.如果有数据帧读出请求时,则进一步判断数据缓存模块的有效帧计数器的计数值是否等于0:

43.若数据缓存模块的有效帧计数器的值等于0,则说明数据缓存模块中没有要读取的数据帧,则保持空闲状态;

44.若数据缓存模块的有效帧计数器的值大于0,则从地址存储模块(fifo先进先出存储器)中读出一个地址数据,并将该地址数据拆分为本次数据帧读出的开始地址和本次数据帧读出的结束地址,并执行步骤2.2;

45.步骤2.2、根据本次数据帧读出的开始地址和本次数据帧读出的结束地址判断本次读出的数据帧是否满足预定的数据帧长度,即通过将本次数据帧读出的结束地址减本次数据帧读出的开始地址,得到本次读出的数据帧的数据个数,通过判断数据个数,将不合格的数据帧丢弃;如:以太网最小要求包长为64个字节,如果读出的数据长度小于64字节,认为是一个不合格的帧将放弃本次读出):

46.如果数据帧长度不满足要求,则放弃本次读操作,并进入空闲状态;

47.如果数据帧长度满足要求,则根据本次数据帧读出的开始地址从数据缓存模块中读出本次数据帧,在本次数据帧读出的过程中,数据缓存模块的地址在每个读时钟进行加1操作;当数据缓存模块的地址等于本次数据帧读出的结束地址时,停止本次数据帧的读取;同时,将数据缓存模块的有效帧计数器进行减1操作;最后进入帧间隔延时,当达到设定的帧间隔延时后,又回到空闲状态。

48.需要说明的是,尽管以上本发明所述的实施例是说明性的,但这并非是对本发明的限制,因此本发明并不局限于上述具体实施方式中。在不脱离本发明原理的情况下,凡是本领域技术人员在本发明的启示下获得的其它实施方式,均视为在本发明的保护之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。