用于超声设备的对称接收器开关

1.相关申请的交叉引用

2.本技术根据35u.s.c.

§

119(e)要求2019年9月19日在代理人案卷号b1348.70132us00下提交的名称为“symmetric receiver switch for ultrasound devices[用于超声设备的对称接收器开关]”的美国临时专利申请序列号62/902,769的优先权权益,该美国临时专利申请特此通过引用以其整体并入本文。

技术领域

[0003]

本技术的技术涉及使用双极性脉冲进行超声成像的超声设备,并且涉及使用双极性脉冲以用于高强度聚焦超声应用的超声设备。

背景技术:

[0004]

一些常规超声设备包括被配置为向超声换能器提供脉冲的脉冲电路。超声换能器通常具有两种操作模式:从换能器发射超声波的发射模式和由换能器接收超声波的接收模式。

技术实现要素:

[0005]

本技术的实施例和方面提供了一种片上超声设备,该片上超声设备包括具有带反馈的脉冲发生器的集成电路系统。对称开关也设置在片上超声设备中并耦合到超声换能器的输出,以便于使用如两级脉冲发生器和多级脉冲发生器等脉冲发生器来驱动超声换能器。所制造的对称开关布置可能会产生阱电容,该阱电容可能是由半导体衬底中的一个或多个掺杂阱中的对称开关的设备结构产生的。可以提供用于阱开关的电路系统,该阱开关可以用于去除设备的信号路径中的较大阱电容。

[0006]

根据本技术的一些实施例,一种装置可以包括耦合在接收装置与超声换能器阵列之间的对称接收器开关阵列。对称接收器开关阵列的第一对称接收器开关可以包括包含第一栅极和第一源极的第一晶体管以及包含第二栅极和第二源极的第二晶体管。第一栅极和第二栅极可以彼此耦合,并且第一源极和第二源极可以彼此耦合。在装置的脉冲发射(tx)模式期间,第一对称接收器开关可以是断开的,并且在装置的接收(rx)模式期间,第一对称接收器开关可以是接通的。

[0007]

在第一方面,在tx模式期间,第一栅极和第二栅极以及第一源极和第二源极可以处于相同电势。

[0008]

在第一方面的变型中,在rx模式期间,第一栅极和第二栅极可以处于浮动电势。在进一步的变型中,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于相同电势;相同电势可以是浮动电势、或接地电势、或固定的非接地电势。在另一个进一步的变型中,第一源极和第二源极以及第一基体和第二基体可以处于相同电势。在另一个进一步的变型中,第一晶体管可以是nmos晶体管并且可以进一步包括第一基体,第二晶体管可以是nmos晶体管并且可以进一步

包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于比第一栅极和第二栅极的浮动电势低的电势。在另一个进一步的变型中,第一晶体管可以是pmos晶体管并且可以进一步包括第一基体,第二晶体管可以是pmos晶体管并且可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于比第一栅极和第二栅极的浮动电势高的电势。

[0009]

在第一方面的另一个变型中,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于浮动电势。第一栅极和第二栅极也可以处于浮动电势。

[0010]

在第二方面,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体。在tx模式期间,第一源极和第二源极以及第一基体和第二基体可以处于相同电势。第一栅极和第二栅极也可以处于这种相同电势。

[0011]

在第三方面,第一晶体管可以进一步包括连接到阵列的超声换能器的第一漏极,并且第二晶体管可以进一步包括连接到接收装置的第二漏极。

[0012]

根据本技术的一些实施例,一种装置可以包括耦合在接收装置与超声换能器阵列之间的对称接收器开关阵列。对称接收器开关阵列的第一对称接收器开关可以包括具有第一栅极、第一源极、第一基体和第一漏极的第一晶体管以及具有第二栅极、第二源极、第二基体和第二漏极的第二晶体管。第一栅极和第二栅极可以彼此耦合,并且第一源极和第二源极可以彼此耦合。第一漏极可以连接到阵列的第一超声换能器,并且第二漏极可以连接到接收装置。在装置的脉冲发射(tx)模式期间,第一栅极和第二栅极以及第一源极和第二源极可以处于相同电势。在该装置的接收(rx)模式期间:第一栅极和第二栅极可以处于第一浮动电势,或者第一基体和第二基体可以处于第一浮动电势,或者第一栅极和第二栅极以及第一基体和第二基体可以处于第一浮动电势。

[0013]

在第一方面,在tx模式期间,第一基体和第二基体可以与第一源极和第二源极处于相同电势。

[0014]

在第二方面,在rx模式期间,第一基体和第二基体可以处于第二浮动电势。

[0015]

在第三方面,第一漏极可以耦合到第一对称接收器开关的输入端子,第二漏极可以耦合到第一对称接收器开关的输出端子,并且在tx模式期间,第二漏极可以处于固定电势。

[0016]

在第三方面的变型中,第一晶体管可以是nmos晶体管,第二晶体管可以是nmos晶体管,并且在tx模式期间,第二漏极可以处于比第一浮动电势高的电势。在进一步的变型中,在tx模式期间,第一晶体管和第二晶体管是关断的,并且第一栅极和第二栅极以及第一源极和第二源极的相同电势为负电势。例如,第一基体和第二基体可以处于第一栅极和第二栅极以及第一源极和第二源极的负电势。负电势可以在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0017]

在第三方面的另一个变型中,第一晶体管可以是pmos晶体管,第二晶体管可以是pmos晶体管,并且在tx模式期间,第二漏极可以处于比第一浮动电势低的电势。在进一步的变型中,在tx模式期间,第一晶体管和第二晶体管可以是关断的,并且第一栅极和第二栅极以及第一源极和第二源极的相同电势可以为正电势。例如,第一基体和第二基体可以处于第一栅极和第二栅极以及第一源极和第二源极的正电势。正电势可以在以下范围内:1v至

100v、或5v至20v、或10v至50v、或15v至75v。

[0018]

在第四方面,第一漏极可以耦合到第一对称接收器开关的输入端子,第二漏极可以耦合到第一对称接收器开关的输出端子,并且在tx模式期间,第二漏极可以处于接地电势。

[0019]

在第五方面,在rx模式期间,第一晶体管和第二晶体管可以是导通的。

[0020]

在第五方面的变型中,第一晶体管和第二晶体管可以是nmos晶体管,并且在rx模式期间,第一栅极和第二栅极的第一浮动电势可以为正电势。第一栅极和第二栅极可以选择性地连接到正电压源并与该正电压源断开连接以设置第一浮动电势。例如,正电势可以在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0021]

在第五方面的另一个变型中,第一晶体管和第二晶体管可以是pmos晶体管,并且在rx模式期间,第一栅极和第二栅极的第一浮动电势可以为负电势。第一栅极和第二栅极可以选择性地连接到负电压源并与该负电压源断开连接以设置第一浮动电势。例如,负电势可以在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0022]

根据本技术的一些实施例,一种超声设备包括超声换能器阵列、被配置为处理从超声换能器阵列输出的电信号的接收装置、以及耦合在接收装置与超声换能器阵列之间的对称开关阵列。对称开关阵列的第一对称开关可以包括包含第一栅极和第一源极的第一晶体管以及包含第二栅极和第二源极的第二晶体管。第一栅极和第二栅极可以彼此耦合,并且第一源极和第二源极可以彼此耦合。在设备的脉冲发射(tx)模式期间,第一对称开关是断开的。在设备的接收(rx)模式期间,第一对称开关是接通的。

[0023]

在第一方面,在tx模式期间,第一栅极和第二栅极以及第一源极和第二源极可以处于相同电势。在第一方面的变型中,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于浮动电势。在进一步的变型中,第一栅极和第二栅极也可以处于浮动电势。

[0024]

在第一方面的另一个变型中,在rx模式期间,第一栅极和第二栅极可以处于浮动电势。在进一步的变型中,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于相同电势,该相同电势可以是接地电势、或浮动电势、或固定的非接地电势。第一源极和第二源极可以与第一基体和第二基体处于相同电势。在另一个进一步的变型中,第一晶体管可以是nmos晶体管并且可以进一步包括第一基体,第二晶体管可以是nmos晶体管并且可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于比第一栅极和第二栅极的浮动电势低的电势。在替代性进一步的变型中,第一晶体管可以是pmos晶体管并且可以进一步包括第一基体,第二晶体管可以是pmos晶体管并且可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于比第一栅极和第二栅极的浮动电势高的电势。

[0025]

在第二方面,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在tx模式期间,第一栅极和第二栅极、第一源极和第二源极以及第一基体和第二基体可以处于相同电势。

[0026]

在第三方面,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在tx模式期间,第一基体和第二基体以及第一源极和第二源极可以处于相同电势。

[0027]

在第四方面,第一晶体管可以进一步包括连接到阵列的超声换能器的第一漏极,并且第二晶体管可以进一步包括连接到接收装置的第二漏极。

[0028]

根据本技术的一些实施例,一种超声设备可以包括超声换能器、被配置为处理从超声换能器输出的电信号的接收装置、以及具有耦合到超声换能器的输入端子和耦合到接收装置的输出端子的对称开关。对称开关可以包括包含第一栅极和第一源极的第一晶体管以及包含第二栅极和第二源极的第二晶体管。第一栅极和第二栅极可以彼此耦合,并且第一源极和第二源极可以彼此耦合。在设备的脉冲发射(tx)模式期间,对称开关可以是断开的。在设备的接收(rx)模式期间,对称开关可以是接通的。

[0029]

在第一方面,在tx模式期间,第一栅极和第二栅极以及第一源极和第二源极可以处于相同电势。

[0030]

在第一方面的变型中,在rx模式期间,第一栅极和第二栅极可以处于浮动电势。在进一步的变型中,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于相同电势,该相同电势可以是浮动电势或接地电势或固定电势。在rx模式期间,第一源极和第二源极可以与第一基体和第二基体处于相同电势。在另一个进一步的变型中,第一晶体管可以是nmos晶体管并且可以进一步包括第一基体,第二晶体管可以是nmos晶体管并且可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于比第一栅极和第二栅极的浮动电势低的电势。在另一个进一步的变型中,第一晶体管可以是pmos晶体管并且可以进一步包括第一基体,第二晶体管可以是pmos晶体管并且可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于比第一栅极和第二栅极的浮动电势高的电势。

[0031]

在第一方面的另一个变型中,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在rx模式期间,第一基体和第二基体可以处于浮动电势。在进一步的变型中,第一栅极和第二栅极也可以处于浮动电势。

[0032]

在第二方面,第一晶体管可以进一步包括第一基体,第二晶体管可以进一步包括第二基体,并且在tx模式期间,第一源极和第二源极以及第一基体和第二基体可以处于相同电势。在变型中,第一栅极和第二栅极也可以处于相同电势。

[0033]

在第三方面,第一晶体管可以进一步包括连接到阵列的超声换能器的第一漏极,并且第二晶体管可以进一步包括连接到接收装置的第二漏极。

[0034]

根据本技术的一些实施例,一种超声设备可以包括超声换能器阵列、被配置为处理从超声换能器阵列输出的电信号的接收装置、以及耦合在接收装置与超声换能器阵列之间的对称开关阵列。对称开关阵列的第一对称开关可以包括具有第一栅极、第一源极、第一基体和第一漏极的第一晶体管以及具有第二栅极、第二源极、第二基体和第二漏极的第二晶体管。第一栅极和第二栅极可以彼此耦合,并且第一源极和第二源极可以彼此耦合。第一漏极可以连接到阵列的第一超声换能器,并且第二漏极可以连接到接收装置。在设备的脉冲发射(tx)模式期间,第一栅极和第二栅极以及第一源极和第二源极可以处于相同电势。在设备的接收(rx)模式期间,第一栅极和第二栅极可以处于第一浮动电势,或者第一基体和第二基体可以处于第一浮动电势,或者第一栅极和第二栅极以及第一基体和第二基体可以处于第一浮动电势。

[0035]

在第一方面,在tx模式期间,第一基体和第二基体可以与第一源极和第二源极处

于相同电势。

[0036]

在第二方面,在rx模式期间,第一基体和第二基体可以处于第二浮动电势。

[0037]

在第三方面,第一漏极可以耦合到第一对称接收器开关的输入端子,第二漏极可以耦合到第一对称接收器开关的输出端子,并且在tx模式期间,第二漏极可以处于固定电势。

[0038]

在第三方面的变型中,第一晶体管可以是nmos晶体管,第二晶体管可以是nmos晶体管,并且在tx模式期间,第二漏极可以处于比第一浮动电势高的电势。在进一步的变型中,在tx模式期间,第一晶体管和第二晶体管可以是关断的,并且第一栅极和第二栅极以及第一源极和第二源极的相同电势可以为负电势。第一基体和第二基体也可以处于第一栅极和第二栅极以及第一源极和第二源极的负电势。负电势可以在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0039]

在第三方面的另一个变型中,第一晶体管可以是pmos晶体管,第二晶体管可以是pmos晶体管,并且在tx模式期间,第二漏极可以处于比第一浮动电势低的电势。在进一步的变型中,在tx模式期间,第一晶体管和第二晶体管可以是关断的,并且第一栅极和第二栅极以及第一源极和第二源极的相同电势可以为正电势。第一基体和第二基体可以处于第一栅极和第二栅极以及第一源极和第二源极的正电势。正电势可以在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0040]

在第四方面,第一漏极可以耦合到第一对称接收器开关的输入端子,第二漏极可以耦合到第一对称接收器开关的输出端子,并且在tx模式期间,第二漏极可以处于接地电势。

[0041]

在第五方面,在rx模式期间,第一晶体管和第二晶体管可以是导通的。

[0042]

在第五方面的变型中,第一晶体管和第二晶体管可以是nmos晶体管,并且在rx模式期间,第一栅极和第二栅极的第一浮动电势可以为正电势。在进一步的变型中,第一栅极和第二栅极可以选择性地连接到正电压源并与该正电压源断开连接以设置第一浮动电势。在另一个进一步的变型中,正电势可以在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0043]

在第五方面的另一个变型中,第一晶体管和第二晶体管可以是pmos晶体管,并且在rx模式期间,第一栅极和第二栅极的第一浮动电势可以为负电势。在进一步的变型中,第一栅极和第二栅极可以选择性地连接到负电压源并与该负电压源断开连接以设置第一浮动电势。负电势可以在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0044]

根据本技术的一些实施例,一种超声设备可以包括超声换能器、被配置为处理从超声换能器输出的电信号的接收装置、以及具有耦合到超声换能器的输入端子和耦合到接收装置的输出端子的对称开关。对称开关可以包括具有第一栅极、第一源极、第一基体和第一漏极的第一晶体管以及具有第二栅极、第二源极、第二基体和第二漏极的第二晶体管。第一栅极和第二栅极可以彼此耦合,并且第一源极和第二源极可以彼此耦合。第一漏极可以连接到阵列的第一超声换能器,并且第二漏极可以连接到接收装置。在设备的脉冲发射(tx)模式期间,第一栅极和第二栅极以及第一源极和第二源极可以处于相同电势。在设备的接收(rx)模式期间,第一栅极和第二栅极可以处于第一浮动电势,或者第一基体和第二

基体可以处于第一浮动电势,或者第一栅极和第二栅极以及第一基体和第二基体可以处于第一浮动电势。

[0045]

在第一方面,在tx模式期间,第一基体和第二基体可以与第一源极和第二源极处于相同电势。

[0046]

在第二方面,在rx模式期间,第一基体和第二基体可以处于第二浮动电势。

[0047]

在第三方面,第一漏极可以耦合到对称开关的输入端子,第二漏极可以耦合到对称开关的输出端子,并且在tx模式期间,第二漏极可以处于固定电势。

[0048]

在第三方面的变型中,第一晶体管可以是nmos晶体管,第二晶体管可以是nmos晶体管,并且在tx模式期间,第二漏极可以处于比第一浮动电势高的电势。在进一步的变型中,在tx模式期间,第一晶体管和第二晶体管可以是关断的,并且第一栅极和第二栅极以及第一源极和第二源极的相同电势可以为负电势。第一基体和第二基体可以处于第一栅极和第二栅极以及第一源极和第二源极的负电势。负电势可以在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0049]

在第三方面的另一个变型中,第一晶体管可以是pmos晶体管,第二晶体管可以是pmos晶体管,并且在tx模式期间,第二漏极可以处于比第一浮动电势低的电势。在进一步的变型中,在tx模式期间,第一晶体管和第二晶体管可以是关断的,并且第一栅极和第二栅极以及第一源极和第二源极的相同电势可以为正电势。第一基体和第二基体可以处于第一栅极和第二栅极以及第一源极和第二源极的正电势。正电势可以在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0050]

在第四方面,第一漏极可以耦合到对称开关的输入端子,第二漏极可以耦合到对称开关的输出端子,并且在tx模式期间,第二漏极可以处于接地电势。

[0051]

在第五方面,在rx模式期间,第一晶体管和第二晶体管可以是导通的。

[0052]

在第五方面的变型中,第一晶体管和第二晶体管可以是nmos晶体管,并且在rx模式期间,第一栅极和第二栅极的第一浮动电势可以为正电势。在进一步的变型中,第一栅极和第二栅极可以选择性地连接到正电压源并与该正电压源断开连接以设置第一浮动电势。正电势可以在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0053]

在第五方面的另一个变型中,第一晶体管和第二晶体管可以是pmos晶体管,并且在rx模式期间,第一栅极和第二栅极的第一浮动电势可以为负电势。第一栅极和第二栅极可以选择性地连接到负电压源并与该负电压源断开连接以设置第一浮动电势。负电势可以在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0054]

根据本技术的一些实施例,一种使用如上文所描述的超声设备或装置的方法可以包括:在tx模式下,使对称开关断开;以及在rx模式下,使对称开关接通。

[0055]

根据本技术的一些实施例,一种使用如上文所描述的超声设备或装置的方法可以包括:通过使第一栅极和第二栅极以及第一源极和第二源极处于相同电势来进入tx模式;以及通过使第一栅极和第二栅极处于第一浮动电势、或者使第一基体和第二基体处于第一浮动电势、或者使第一栅极和第二栅极以及第一基体和第二基体处于第一浮动电势来进入rx模式。

附图说明

[0056]

将参考附图描述本技术的各个方面和实施例。应当理解,这些附图不一定按比例绘制。出现在多个附图中的项在其出现的所有附图中可以用相同的附图标记表示。在附图中:

[0057]

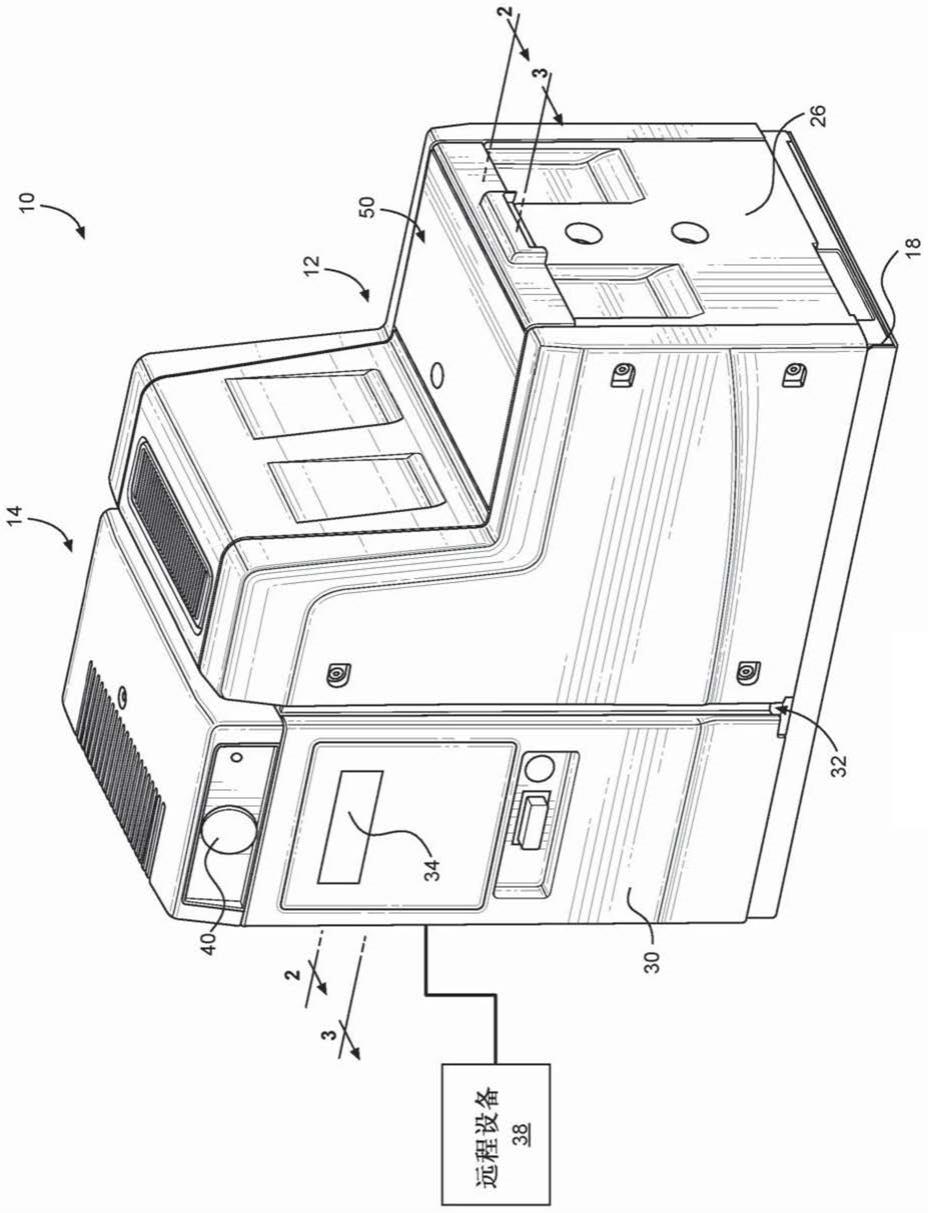

图1是展示了包括多个脉冲电路和多个接收器开关的超声设备的框图。

[0058]

图2是展示了耦合到电容式超声换能器的脉冲电路的框图。

[0059]

图3是展示了包括脉冲发生器和反馈电路的脉冲电路的框图。

[0060]

图4是展示了用于操作耦合到电容式超声换能器的脉冲电路的方法的动作的框图。

[0061]

图5a是展示了被配置为产生多个阈值电压的电阻梯的电路图。

[0062]

图5b是展示了被配置为产生检测信号的分压电路的电路图。

[0063]

图6a展示了示出由脉冲电路提供给电容式超声换能器的示例信号的时序图。

[0064]

图6b展示了示出由脉冲电路提供给电容式超声换能器的切趾信号的时序图。

[0065]

图7是展示了耦合到多个电容式超声换能器的多个脉冲电路的框图。

[0066]

图8a是展示了在发射模式下操作的超声设备的框图。

[0067]

图8b是展示了在接收模式下操作的超声设备的框图。

[0068]

图9是展示了包括对称开关的超声设备的框图。

[0069]

图10展示了示出被配置为驱动图9的对称开关的控制信号的时序图。

[0070]

图11是展示了包括对称开关的替代设备的框图。

[0071]

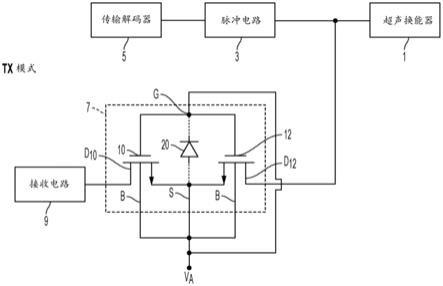

图12是展示了根据本技术的非限制性方面的在发射模式下操作的超声设备的框图。

[0072]

图13是展示了根据本技术的非限制性方面的在接收模式下操作的超声设备的框图。

[0073]

图14a是展示了根据本技术的非限制性方面的超声装置的框图。

[0074]

图14b是展示了根据本技术的非限制性方面的图14a的超声装置的栅极控制器的图。

[0075]

图14c是示出了根据本技术的非限制性方面的图14a的超声装置的阱开关的图。

[0076]

图15是展示了根据本技术的非限制性方面的图14a的超声装置的替代栅极控制器的图。

[0077]

图16a是示出了根据本技术的非限制性方面的图14a的超声装置的一些元件在发射模式操作、接收模式操作以及从发射模式操作到接收模式操作的转变期间的状态的时序图。

[0078]

图16b至图16d是根据本技术的非限制性方面的图14a的超声装置在发射模式操作、接收模式操作以及从发射模式操作到接收模式操作的转变期间的信号的时序图。

具体实施方式

[0079]

片上超声设备可以包括与半导体管芯(本文中也称为“芯片”)上的电路系统集成的超声换能器。可以在超声探头或其他超声设备内采用片上超声设备来执行超声成像、疗法(例如,高强度聚焦超声(hifu))或两者。因此,与超声换能器集成的电路系统可以支持这

种功能,并采用适合用于探头或其他形状因子(如听诊器)的形式。电路系统可以包括脉冲电路,该脉冲电路可以产生用于驱动片上超声设备的超声换能器以产生适合于成像和/或hifu的超声信号(例如超声波)的电脉冲。脉冲电路可以是数字电路、模拟电路或模拟-数字混合电路。

[0080]

本技术的各方面可以提供带反馈的双极性、多级脉冲电路。尽管这些电路可以用于单极性脉冲,但申请人已经认识到被配置为发射单极性脉冲的超声设备表现出有限的动态范围,因为与单极性脉冲相关联的直流(dc)分量可能会使用于接收与反射超声波相对应的信号的接收电路饱和,从而降低所产生图像的对比度。单极性脉冲可以是仅采用大于或等于零(0)的电压或替代性地小于或等于零(0)的电压的脉冲。申请人已经认识到,相比之下,使用双极性脉冲可以限制dc分量对接收电路的影响,因此与利用单极性脉冲的超声设备相比,可以提供显著增加的动态范围和图像对比度。因此,本技术的各方面可以提供被配置为利用双极性脉冲的超声设备,这些双极性脉冲是可以采用大于、小于或等于零(0)的电压的脉冲。

[0081]

使用带反馈的多级脉冲电路是因为申请人认识到通过对发射到被成像目标的超声波脉冲执行时域和空域切趾可以显著增强超声图像的对比度。切趾可以减小与发射的脉冲相关联的旁瓣的范围,从而提高所产生图像的分辨率。控制可以采用多个值的信号的能力可以促进时间和空间切趾的脉冲的产生。

[0082]

本文所述类型的多级脉冲可以采用从一组可选值中选择的任何值,其中,该组可以包括至少三个值。在提供多个电源电压的情况下,产生这种多级脉冲可能需要复杂的脉冲发生器设计。然而,提供多个电源电压可能是不切实际的。当超声设备被设置成手持超声探头或其他紧凑形式时,可能尤其是这样,因为可能需要附加的片外供电电路。申请人已经认识到,使用反馈电路可以促进多级脉冲的产生和切趾脉冲的产生而无需借助多个电源电压,从而简化超声设备的设计。

[0083]

本技术的各方面提供了一种超声设备,该超声设备包括被布置成将超声换能器耦合到接收电路系统的对称开关。至少由于上述原因,使用双极性脉冲电路可能是有益的;然而,双极性脉冲会对超声设备的接收电路系统产生不利影响。由发射电路产生的双极性脉冲可能无意中直接电耦合到接收电路,该接收电路可能没有被设计成承受双极性脉冲的较大正负电压信号。因此,如果没有为接收电路系统提供适当的保护,则超声设备可能被损坏。申请人已经认识到,被设计成阻挡与双极性脉冲相关联的较大正负电压信号的适当定位的对称开关可以防止对接收电路系统的损坏,从而在与双极性脉冲电路一起使用时保护超声设备。

[0084]

申请人已经认识到,所制造的对称开关布置可能会产生阱电容,该阱电容可能是由于对称开关的设备结构设置在半导体衬底中的一个或多个掺杂阱中而产生的。例如,形成对称开关的晶体管可以设置在掺杂阱中,该掺杂阱进而可以设置在另一个掺杂阱中。阱可以是高电压阱,这些高电压阱可以在超声设备的信号路径中产生较大阱电容。为了减少或消除通过(多个)阱耦合的噪声,对称开关可以设置有阱开关,该阱开关可以用于去除信号路径中的阱电容。

[0085]

本文所描述的cmos电路系统特征可以促进以商业上有价值的形状因子创建适合于执行超声成像和/或hifu的片上超声设备。

[0086]

现在转向附图,如上所述,本技术的各方面提供了一种超声设备,该超声设备包括双极性多级脉冲电路和将双极性多级脉冲电路耦合到接收电路系统的对称开关。图1是展示了超声设备的一般架构的框图,该超声设备可以包括根据本技术的各方面的各种特征。超声设备100可以包括多个电容式超声换能器1011…

101n,其中n是整数。超声设备100可以包括多个电路系统通道1021…

102n,该多个电路系统通道可以分别电连接到超声换能器1011…

101n。

[0087]

在一些实施例中,超声换能器1011…

101n可以是传感器,并且可以产生表示接收到的超声波的电信号。在一些实施例中,超声换能器1011…

101n还可以发射超声信号(即,超声波)。在一些实施例中,超声换能器1011…

101n可以是电容式微加工超声换能器(cmut)。然而,在其他实施例中可以使用其他类型的电容式超声换能器。

[0088]

电路系统通道1021…

102n可以包括发射电路系统、接收电路系统或两者。发射电路系统可以包括分别耦合到脉冲电路1031…

103n的发射解码器1051…

105n。脉冲电路1031…

103n可以控制相应的超声换能器1011…

101n以发射超声信号。

[0089]

本技术的各方面涉及脉冲电路1031…

103n。在一些方面,脉冲电路1031…

103n可以被配置为产生双极性脉冲。在一些方面,脉冲电路1031…

103n可以被配置为产生多级脉冲。如下文将进一步描述的,在一些方面,脉冲电路1031…

103n可以包括脉冲发生器和附加电路系统。在一些方面,脉冲电路1031…

103n可以包括脉冲发生器和反馈电路系统。

[0090]

电路系统通道1021…

102n的接收电路系统可以接收分别从超声换能器1011…

101n输出的电信号。在所展示的示例中,电路系统通道1021…

102n分别可以包括接收开关1071…

107n和接收电路1091…

109n。接收开关1071…

107n中的每一个可以被选择性地控制以激活或去激活来自超声换能器1011…

101n中的对应超声换能器的电信号的读数。接收电路1091…

109n可以包括电流-电压转换器。电流-电压转换器可以包括跨阻抗放大器(tia);因此,接收电路1091…

109n被展示为tia,但是附加和/或替代电路系统可以构成接收电路1091…

109n。如将理解的,代替电流-电压转换器,接收电路1091…

109n可以包括电流-数字转换器和/或电流输入模数转换器。

[0091]

本技术的各方面涉及接收开关1071…

107n。在一些方面,接收开关1071…

107n可以包括对称开关,该对称开关被配置为阻挡表现出正电压和/或负电压的大电压信号。接收开关1071…

107n可以被配置为形成电开路,用于在发射模式期间分别将接收电路1091…

109n与发射电路系统和超声换能器1011…

101n解耦。接收开关1071…

107n可以进一步被配置为形成电短路,以在接收模式期间分别将接收电路1091…

109n耦合到超声换能器1011…

101n。

[0092]

超声设备100可以进一步包括模数转换器(adc)111。adc 111可以被配置为对从超声换能器1011…

101n接收到的信号进行数字化。接收到的信号的数字化可以串联或并联执行。尽管展示了单个adc 111并且因此示出为由电路系统通道1021…

102n共享,但是本技术的替代方面可以为每个电路系统通道或每组电路系统通道提供一个adc。

[0093]

虽然图1可能展示了作为超声设备100的电路的一部分的多个部件,但是应当理解,本文所描述的各个方面并不限于所展示的确切部件或部件配置。

[0094]

图1所展示的部件可以位于单个衬底上或不同的衬底上。当位于单个衬底上时,衬底可以例如是半导体衬底(例如硅衬底),并且部件可以单片集成在该衬底上。当所展示部件不在同一衬底上时,例如,超声换能器1011…

101n可以在第一衬底上,而其余所展示部件

可以在第二衬底上。作为进一步的替代方案,超声换能器1011…

101n和一些所展示部件可以在同一衬底上,而其他部件可以在不同的衬底上。当使用多个衬底时,这些衬底可以是半导体衬底(例如硅衬底)。

[0095]

根据本技术的各方面,图1的部件可以形成超声探头的一部分,该超声探头可以是手持式的。在一方面,图1的部件可以形成被配置为由患者佩戴的超声贴片的一部分。

[0096]

图2是展示了根据本技术的各方面的脉冲电路103的示例的框图,该脉冲电路可以用作图1的脉冲电路1031…

103n中的任一个。脉冲电路103可以包括脉冲发生器220和反馈电路230。脉冲电路103可以包括电连接到电容式超声换能器101的输出端子,并且可以被配置为向电容式超声换能器101提供输入信号240。在一些方面,脉冲发生器220可以被配置为产生双极性脉冲,这些双极性脉冲除了零之外还可以采用正值和负值。通过产生双极性脉冲,脉冲发生器220可以减少或抑制与提供给超声换能器101的脉冲相关联的任何dc分量。如前所述,当发射具有dc分量的脉冲时,超声设备100所产生的图像的质量可能会降低。与脉冲的通带分量相比,dc分量在穿过被成像物体传播时可能衰减得显著更少。因此,接收电路可以接收到dc分量显著大于通带分量的信号。作为结果,接收电路可能饱和,因此限制了图像的动态范围。

[0097]

在本技术的一些方面,反馈电路230可以被配置为控制脉冲发生器220以产生多级脉冲。多级脉冲可以采用从一组可选值中选择的任何值。该组可以包括至少三个值,并且在至少一些方面,可以包括四个或更多个值(例如,3个与30个之间的值、4个与20个之间的值、4个与10个之间的值或这些范围内的任何数量)。使用多级脉冲可以使得能够优化脉冲的包络以最大化由脉冲形成的超声图像的参数。例如,脉冲的包络可以被工程化为最大化图像对比度。具体地,通过使用时域切趾,脉冲的最终频率内容可以表现出大的主瓣和抑制的旁瓣,这可以增加成像分辨率。时域切趾可能需要表现出尽可能多的电压等级的脉冲来产生几乎连续的窗口函数。然而,为了产生具有较大等级数量的脉冲,可能需要复杂的脉冲电路。因此,等级数量应该被选择成最大化执行时域切趾的能力,同时保持脉冲电路103相对简单和紧凑。在本技术的一些方面,脉冲发生器220可以被配置为产生多级脉冲,这些多级脉冲可以具有3个与30个之间的等级、5个与10个之间的等级或任何合适的值或值范围之间。

[0098]

使用多级脉冲还可以实现空域切趾。为了执行空域切趾,可以用具有空间相关振幅的输入信号来驱动超声换能器1011…

101n。通过访问参考电压,可以方便地提供具有空间相关振幅的输入信号。

[0099]

在本技术的一些方面,反馈电路230可以被配置为通过提供多个参考电压来促进多级脉冲的产生。使用本文所述类型的反馈电路可以促进多级脉冲发生器的设计而无需借助多个电源电压。如上所述,可能不期望利用多个电源电压,因为多个电源电压可能需要相当大的超声探头,该相当大的超声探头可能难以适配手持式形状因子。相比之下,本文所述类型的反馈电路可以使得紧凑的电路系统能够用于产生参考电压;这种紧凑的电路系统可以容易地并入手持式超声探头中。

[0100]

如图2的框图所描绘的,反馈电路230的输出端子可以电耦合到脉冲发生器220的输入端子。反馈电路230的输入端子可以电耦合到脉冲发生器220的输出端子。反馈电路230的输入端子还可以被配置为接收表示超声换能器101的输入信号240的检测信号241。在本

技术的一些方面,输入信号240和检测信号241可以是电压。在本技术的一些方面,检测信号241可以从输入信号240得到。例如,检测信号241可以与输入信号240成比例。

[0101]

反馈电路230可以被配置为将检测信号241与阈值电压进行比较。在本技术的一些方面,阈值电压可以从一组可选阈值电压中选择。基于比较结果,反馈电路230可以向脉冲发生器220的输入端子提供控制信号242。

[0102]

在本技术的一些方面,反馈电路230可以被配置为确定检测信号241的值是大于、小于还是等于阈值电压。在本技术的一些方面,反馈电路230可以被配置为确定检测信号241的值是否在阈值电压的范围内,如在阈值电压的10%内、在阈值电压的5%内、或在任何期望的范围内。基于检测信号241相对于阈值电压的值,反馈电路230可以控制脉冲发生器220以保持输入信号240的当前值或者将输入信号240改变为另一个值。例如,如果检测信号241的值小于阈值电压,则反馈电路230可以控制脉冲发生器220以增加输入信号240的值,直到检测信号241的值等于阈值电压或在阈值电压的预定范围内。如果检测信号241的值大于阈值电压,则反馈电路230可以控制脉冲发生器220以减小输入信号240的值,直到检测信号241的值等于阈值电压或在阈值电压的预定范围内。

[0103]

在本技术的一些方面,超声换能器101是电容式超声换能器(cut)101。与cut 101相关联的电容可以使电荷被保留,这可以导致当检测信号241已经达到所选阈值电压时跨该cut的端子保持恒定电压。当检测信号241的值小于阈值电压时,可以控制脉冲发生器220以对与cut 101相关联的电容进行充电,从而增加输入信号240的值。当检测信号241的值大于阈值电压时,可以控制脉冲发生器220以对与cut 101相关联的电容进行放电或负充电,从而降低输入信号240的值。

[0104]

在本技术的一些方面,反馈电路230可以异步地控制脉冲发生器220。因此,可以允许控制信号242、输入信号240和检测信号241的值在任何时刻变化。在本技术的一些方面,脉冲电路103可以由时钟信号定时。然而,控制信号242可以仍被允许在不由时钟信号定义的时间段内变化。

[0105]

图3是展示了图2的脉冲电路103的示例的详细实施方式的框图。在本技术的一些方面,脉冲发生器220可以包括两个晶体管322、324。然而,应当理解,在其他方面,脉冲发生器220可以包括不同数量的晶体管。晶体管322、324可以包括金属氧化物半导体场效应晶体管(mosfet)、结型场效应晶体管(jfet)、双极结型晶体管(bjt)、金属半导体场效应晶体管(mesfet)、绝缘栅场效应晶体管(igfet)、横向扩散金属氧化物半导体晶体管(ldmos)或其任何合适的组合。晶体管322的导电类型可以不同于晶体管324的导电类型。例如,晶体管322可以具有基于在电场作用下移动的孔洞所维持的漂移电流的导电性。晶体管324可以具有基于在电场作用下移动的电子所维持的漂移电流的导电性。

[0106]

在本技术的一些方面,晶体管324可以是nmosfet,并且晶体管322可以是pmosfet。晶体管322、324可以被配置为使得nmos晶体管324的漏极可以连接到pmos晶体管324的漏极。这些漏极可以进一步连接到cut 101的端子。nmos晶体管324的源极可以连接到电源电压vn。在一些方面,vn可以小于零;例如,vn可以在-100v与-1v之间、在-50v与-20v之间、或在任何期望的值范围之间。pmos晶体管322的源极可以连接到电源电压v

p

。在一些方面,v

p

可以大于零;例如,v

p

可以在1v与100v之间、在20v与50v之间、或在任何期望的值范围之间。提供给晶体管322、324的栅极的电压可以由图2所展示的反馈电路230产生。

[0107]

在本技术的一些方面,反馈电路230可以包括控制器336、分压电路332和参考发生器334。在一些方面,反馈电路230可以进一步包括电平移位器338、340。分压电路332可以被配置为接收与输入信号240相对应的电压,并输出检测信号341。分压电路332可以被配置为输出与输入信号240成比例的检测信号341。检测信号341可以通过控制器336的输入端子in提供给控制器336。

[0108]

参考发生器334可以被配置为向控制器336的输入端子ref提供一组可选阈值电压。在本技术的一些方面,参考发生器334可以经由n个连接器连接到控制器336,并且可以被配置为经由n个连接器中的对应连接器提供n个阈值电压,其中,n可以采用大于二的任何合适的值。阈值电压可以等于、大于或小于零。

[0109]

在本技术的一些方面,反馈电路230可以被数字控制,并且控制器336可以包括数字控制电路系统。控制器336可以被配置为基于检测信号341与从n个阈值电压中选择的阈值电压的比较来控制脉冲发生器220以保持、增加或减小与输入信号240相对应的电压值。

[0110]

控制器336可以从参考发生器334提供的n个阈值电压中选择阈值电压。例如,可以通过信号(例如,sel_threshold信号)来数字地选择阈值电压。sel_threshold信号可以包括m个位,其中,m具有使得n等于或小于2m的值。每个位组合可以从n个阈值电压中选择一个阈值电压。例如,等于000的sel_threshold序列可以选择八个阈值电压中的最少或最小电压,并且等于111的sel_threshold序列可以选择八个阈值电压中的最大电压。此外,sel_threshold信号可以异步地变化。

[0111]

在本技术的一些方面,分压电路332可以输出与输入信号240按缩放因子成比例的检测信号341。在这些方面,参考发生器334可以被配置为提供一组阈值电压,该组阈值电压以相同的缩放因子被缩放到输入信号240。因此,检测信号341可以直接与所选阈值电压进行比较,而不必进一步缩放检测信号341或输入信号240。

[0112]

在本技术的各方面,信号p/n可以用于控制晶体管322、324的状态。例如,p/n可以是单比特信号。信号p/n可以被设置为用于激活晶体管322的p信号或用于激活晶体管324的n信号。然而,可以使用被配置为控制晶体管322、324的状态的任何合适数量的位。单个位的值可以使晶体管322或晶体管324进入导电状态,无论是在线性模式还是饱和模式下。在一方面,一次仅一个晶体管可以处于导电状态。

[0113]

基于sel_threshold信号和p/n信号的值,控制器336可以通过输出端子p_control、n_control来输出控制信号242

p

、242n。控制信号242

p

、242n一起可以表示图2所展示的控制信号242。例如,信号242

p

可以包括单个位并且可以用于控制pmos晶体管322的状态,而信号242n可以包括单个位并且可以用于控制nmos体晶管324的状态。可以允许这两个晶体管322、324同时处于截止状态。

[0114]

在本技术的一些方面,控制信号242

p

和242n可以分别直接驱动晶体管322和324的栅极。在其他方面,如图3所示,控制信号242

p

、242n可以分别耦合到电平移位器338和电平移位器340的输入端子。电平移位器338的输出端子可以耦合到晶体管322的栅极,而电平移位器340的输出端子可以耦合到晶体管324的栅极。电平移位器338、340可以被配置为基于信号242

p

和242n将控制器336所产生的电压适配成与晶体管322、324兼容的电压,以驱动晶体管322、324进入其截止或导电状态。

[0115]

在本技术的一个方面,当检测信号341小于所选阈值电压时,控制器336可以被配

置为输出具有适合于使pmos晶体管322进入导电状态并且使nmos晶体管324进入截止状态的值的控制信号242

p

、242n。在这方面,从电压电源v

p

流向cut 101的电流可以对cut 101进行充电,直到检测信号341达到所选阈值电压或者达到所选阈值电压的预定范围内的电压。

[0116]

在本技术的一个方面,当检测信号341大于所选阈值电压时,控制器336可以被配置为输出具有适合于使nmos晶体管324进入导电状态并且使pmos晶体管322进入截止状态的值的控制信号242

p

、242n。在这方面,从cut 101流向电压电源vn的电流可以对cut 101进行放电或负充电,直到检测信号341达到所选阈值电压或达到所选阈值电压的预定范围内的电压。

[0117]

在本技术的一个方面,当检测信号241等于所选阈值电压或者在所选阈值电压的预定范围内时,可以通过信号242

p

、242n控制pmos晶体管322和nmos晶体管324,使得晶体管322、324两者进入截止状态。在这方面,没有电流会流向或流出cut 101。因此,cut 101可以保持电荷,从而保持与跨其端子的所选阈值电压相对应的目标电压。

[0118]

如将理解的,在可能期望超声换能器101保持其电荷的本技术的方面,超声换能器101可以是cut。在这些方面,电阻超声换能器可能无法正常工作。

[0119]

应当理解,尽管控制器336可以被配置为基于p/n信号和sel_threshold信号来控制脉冲发生器220,如以上结合图3所描述的,但是相比之下,脉冲电路103在这方面没有限制。因此,也可以采用被配置为控制脉冲发生器220保持、增加或减小输入信号240的值直到达到阈值电压、或者直到达到阈值电压的预定范围内的值的任何信号或信号组合。

[0120]

图4是展示了根据本技术的各方面的用于操作脉冲电路103以驱动cut 101的方法400的流程图。图4的方法400可以结合图2所展示的脉冲电路103或图3所展示的脉冲电路103的实施方式来执行。方法400可以从动作402开始,在该动作中可以从一组n个可选阈值电压中选择阈值电压,其中,n可以采用大于二的任何合适的值。在一些方面,可以经由具有m个位的数字信号来选择阈值电压,其中,n的值等于或小于2m。

[0121]

方法400可以继续到动作404,在该动作中输入信号240可以由脉冲发生器220提供给cut 101。根据本技术的一个方面,脉冲发生器220可以被配置为提供可以表现出正电压和/或负电压的双极性输入信号。如上所述,本文所述类型的双极性输入信号可能导致回波信号不会使超声设备100的接收电路1091…

109n饱和。

[0122]

根据本技术的另一个方面,脉冲发生器220可以被配置为提供多级脉冲,该多级脉冲可以呈现从多个可选值中选择的值。如以上所讨论的,能够产生多级脉冲的脉冲电路可以促进时域和空域切趾,这可以使得图像对比度增强。本文所述类型的多级脉冲的产生可以通过被设计成提供从一组阈值电压中选择的阈值电压的反馈电路来促进,而无需借助附加电压供电电路的使用,这些附加电压供电电路会增加手持式超声探头的大小并因此使得这些探头更难操纵,从而对用户更不太友好。

[0123]

在动作406处,检测信号341可以从输入信号240得到。检测信号341可以表示输入信号240。例如,检测信号341可以等于输入信号240或与其成比例。

[0124]

在动作408处,可以将检测信号341与在动作402处选择的阈值电压进行比较。在本技术的一些方面,检测信号341可以按缩放因子与输入信号240成比例。在这些方面,所选阈值电压可以按相同的缩放因子缩放到输入信号240。作为比较的结果,检测信号341可以被确定为等于、大于或小于所选阈值电压。

[0125]

在动作410处,基于在动作408处执行的比较的结果,控制信号242可以被提供给脉冲发生器220以控制输入信号240。控制信号242可以由反馈电路230提供,该反馈电路可以数字控制。

[0126]

在动作412处,如果检测信号341的值被确定为小于所选阈值电压,则控制信号242可以控制脉冲发生器220以增加与输入信号240相对应的电压。在本技术的一些方面,控制信号242可以使pmos晶体管322进入导电状态,以对与cut 101相关联的电容进行充电。

[0127]

在动作412处,如果检测信号341的值被确定为大于所选阈值电压,则控制信号242可以控制脉冲发生器220以减小与输入信号240相对应的电压。在本技术的一些方面,控制信号242可以使nmos晶体管324进入导电状态,以对与cut 101相关联的电容进行放电或负充电。

[0128]

除非在动作412处确定检测信号341的值等于所选阈值电压或在所选阈值电压的预定义范围内,否则方法400可以返回到动作406。也就是说,方法400可以重复一个或多个循环,直到检测信号341的值被确定为等于所选阈值电压或在所选阈值电压的预定义范围内。

[0129]

在动作412处,如果检测信号341的值被确定为等于所选阈值电压或在所选阈值电压的预定义范围内,则控制信号242可以控制脉冲发生器220以保持输入信号240的当前值。在本技术的一些方面,控制信号242可以使nmos晶体管324和pmos晶体管322进入截止状态,以允许与cut 101相关联的电容保持其当前电荷。预定义范围可以在所选阈值电压的10%以内、在所选阈值电压的5%以内、或在任何合适的预定义范围内。

[0130]

一旦输入信号240已经达到与所选阈值电压相对应的值,方法400就可以进行到动作414,在该动作中可以从n个可选阈值电压中选择另一个阈值电压。如果在动作414处选择了另一个阈值电压,则方法400可以循环回到动作404并针对新选择的阈值电压重复。新阈值电压的选择可以异步地执行。如果在动作414处没有选择新的阈值电压,则方法400可以在动作416处结束。

[0131]

图5a是展示了根据本技术的各方面的图3的参考发生器334的示例的电路图。参考发生器334可以包括电阻梯,该电阻梯被配置为产生n个阈值电压ref1…

refn,其中,n可以采用大于二的任何值。在一些方面,电阻梯可以包括串联连接的n 1个电阻器5341…

534

n 1

。电阻器5341可以耦合到电源电压vh,该电源电压可以等于图3所示的电源电压v

p

。电阻器534

n 1

可以耦合到电源电压v

l

,该电源电压可以等于图3所示的电源电压vn。

[0132]

在本技术的一些方面,所有n 1个电阻器5341…

534

n 1

的电阻可以相等,以将从vh到v

l

的电压范围分成n个相等区段。在本技术的其他方面,电阻器5342…

534

n 1

的电阻可以等于r,而电阻器5341的电阻可以等于xr,其中,x可以采用0.01与100之间的任何值。如将理解的,x也可以是其他值。在这些其他方面,与从vh到v

l

的电压范围成比例的缩放电压范围可以被分成n个相等区段。

[0133]

图5b是展示了根据本技术的各方面的图3的分压电路332的示例的电路图。分压电路332可以包括被配置为产生与输入信号240成比例的信号(检测信号341)的电容分压器。电容分压器可以包括一对电容器532、533。电容器532可以具有耦合到脉冲发生器220的输出的一个端子和耦合到控制器336的输入的一个端子。在一些方面,电容器532可以被配置为接收由脉冲发生器220产生的输入信号240。电容器533可以具有耦合到控制器336的输入

的一个端子(与电容器532相同)和耦合到电源电压vc的一个端子。在一些方面,电容器533可以被配置为接收输入信号240的缩放版本。在一些方面,电源电压vc可以等于图3所示的电源电压vn。电容器532和533的电容可以被配置为与检测信号341按与缩放图5a的阈值电压的缩放因子相同的缩放因子来缩放。在这些方面,检测信号341可以直接与从n个阈值电压中选择的阈值电压进行比较,而不必首先缩放这两个信号中的任一个,如以上所讨论的。

[0134]

图6a展示了根据本技术的一个方面的可以由脉冲电路103提供给cut 101的信号的时序图600的示例。具体地,时序图600展示了目标信号602的示例和输入信号240的示例。在这方面,阈值电压可以从七个阈值电压中选择。目标信号602可以表示要由输入信号240跟随或模拟的电压信号,该输入信号可以是电压信号。如果输入信号240例如在时间t1时等于目标信号602,则检测信号341的电压值可以等于当前阈值电压。在这种情况下,为了保持输入电压恒定,反馈电路230可以控制脉冲发生器220以保持输入信号240恒定在输入信号240的当前值。如果输入信号240的电压值例如在时间t2时小于目标信号602的电压值,则反馈电路230可以控制脉冲发生器220以增加输入信号240的电压值,直到达到目标信号602的电压值。如果输入信号240的电压值例如在时间t3时大于目标信号602的电压值,则反馈电路230可以控制脉冲发生器220以减小输入信号240的电压值,直到达到当前目标电压。在一些实施例中,目标信号602可以异步地变化。因此,目标信号602的每个区段的持续时间可以独立于其他区段的持续时间来设置。

[0135]

在本技术的一些方面,脉冲电路103可以被配置为产生dc分量大于零的输入信号240。可以选择dc分量的范围来偏置接收电路(例如,接收电路1091),而不会让接收电路达到饱和。

[0136]

在本技术的一些方面,输入信号240可能过冲并且其电压值大于目标信号602的电压值(图6a中未示出)。对于这种过冲,反馈电路230可能试图减轻过冲的影响。也就是说,反馈电路230可以被配置为使阈值电压偏斜。在本技术的一些方面,可以通过向阈值电压添加(或减去)电压偏移来使阈值电压偏斜。例如,如果期望的输出电压是x伏,则阈值电压可以被设置为y伏,使得x与y之间的差等于过冲电压。在一些实施例中,可以通过不均匀的电阻梯使阈值电压偏斜。

[0137]

图6b展示了根据本技术的一个方面的可以由脉冲电路103提供给cut 101的切趾信号的时序图620的示例。具体地,时序图620展示了切趾目标信号604和切趾输入信号240的示例。反馈电路230可以被配置为基于高斯窗(gaussian window)、汉明窗(hamming window)、平顶窗、余弦窗或任何合适的窗函数来执行输入信号240的时域切趾。本文所述类型的多级脉冲可以提供足够程度的粒度以忠实地生成连续窗函数。

[0138]

图7是展示了根据本技术的各方面的耦合到多个cut 1011、1012、1013…

101n的多个脉冲电路的框图。在一些方面,cut 1011、1012、1013…

101n可以被布置成形成一维(1d)阵列。在其他方面,cut1011…

101n可以被布置成形成二维(2d)阵列。cut 1011…

101n可以耦合到相应脉冲发生器2201、2202、2203…

220n的输出端子,如图7示意性地示出的。反馈电路2301、2302、2303…

230n可以分别耦合到脉冲发生器2201…

220n的输入端子,并且还可以分别耦合到脉冲发生器2201、2202、2203…

220n的输出端子,如图7所示。在一些方面,反馈电路2301…

230n可以是单独的电路。在其他方面,反馈电路2301…

230n可以是被配置为控制脉冲发生器2201…

220n的单个电路的一部分。

[0139]

如图7所展示的,反馈电路2301…

230n可以控制脉冲发生器2201…

220n以产生输入信号7401、7402、7403…

740n,这些输入信号表现出与空间相关的振幅。在本技术的一些方面,反馈电路2301…

230n可以控制脉冲发生器2201…

220n以执行输入信号7401、7402、7403…

740n的空域切趾。例如,输入信号7401…

740n可以表现出在阵列中心较大并且按照预定义的轮廓向阵列边缘衰减的振幅。空域切趾函数可以用于高斯窗、汉明窗、平顶窗、余弦窗或任何合适的窗。空域切趾可以在一个空间维度或两个空间维度上执行。通过执行空域切趾,可以有效地改变窗的孔径,从而提供了对发射的超声波的空间轮廓进行优化的手段。在本技术的一些方面,可以优化空间轮廓以最小化空间旁瓣。能够发射具有最小旁瓣或抑制旁瓣的空间轮廓的超声设备可以表现出增强的空间分辨率以及因此增强的图像对比度。

[0140]

在本技术的一些方面,cut 101可以连接到发射电路系统和接收电路系统。在发射期间,由脉冲电路103产生的双极性输入信号可能无意中耦合到接收电路系统的接收电路。在一些方面,接收电路可能包括未被设计成承受由脉冲发生器220产生的那种较大正负电压信号的部件。因此,将双极性脉冲直接耦合到接收电路中可能具有不利影响,这可能导致接收电路系统的一个或多个部件的损坏。

[0141]

根据本技术的各方面,提供了用于在产生双极性脉冲时将接收电路与发射电路解耦的对称开关。为了本技术的目的,对称开关可以是基于晶体管的开关,该基于晶体管的开关可以具有相同类型的输入端子和输出端子。例如,对称开关的输入端子和输出端子可以都是源极、或者都是漏极、或者都是发射极、或者都是集电极、或者都是其他端子类型。

[0142]

图8a和图8b是展示了根据本技术的各方面的分别在发射模式和接收模式下操作的超声设备的框图。对称开关107可以包括连接到脉冲电路103的输出端子的输入端子。在一些方面,对称开关107的输入端子可以连接到脉冲电路103的脉冲发生器220的输出端子。对称开关107的输入端子可以进一步连接到cut 101的端子。在一些方面,对称开关107的输入端子可以耦合在脉冲发生器220的输出端子与cut 101的端子之间。对称开关107还可以包括耦合到接收电路109的输入端子的输出端子。在一些方面,接收电路109包括电流-电压转换器,该电流-电压转换器被配置为将可以由cut 101响应于从反射超声波接收回波信号而产生的电流转换成电压。在一些方面,电流-电压转换器可以包括跨阻抗放大器(tia)。

[0143]

如图8a所展示的,在发射模式(tx模式)下,对称开关107可以被配置为提供高阻抗以将脉冲电路103产生的脉冲与接收电路109解耦。在一些方面,对称开关107可以被配置为在发射模式期间作为开路操作。图8a中所示的箭头801可以表示在发射模式期间与输入信号240相对应的信号路径方向。

[0144]

如图8b所展示的,在接收模式(rx模式)下,对称开关107可以被配置为提供低阻抗以将cut 101耦合到接收电路109,使得接收电路109可以接收由cut 101响应于从反射超声波接收回波信号而产生的电流。在本技术的一些方面,对称开关107可以被配置为在接收模式期间将接收电路109短路到cut 101。在一些方面,脉冲电路103可以被配置为在接收模式期间处于高阻抗状态。图8b中所示的箭头821可以表示在接收模式期间与来自cut 101的信号相对应的信号路径方向。

[0145]

图9是示意性地展示了根据本技术的各方面的包括对称开关907的超声设备900的实例的框图。对称开关907可以被配置为在发射模式期间阻挡与脉冲电路103所产生的双极性脉冲相关联的正电压和负电压到达接收电路109,从而防止对接收电路109的损坏。

[0146]

在本技术的一些方面,对称开关907可以包括两个晶体管910、912。然而,在其他方面,对称开关907可以包括被配置为在发射模式期间阻挡双极性脉冲的任何合适数量的晶体管。晶体管910、912可以是任何类型的,如包括nmos或pmos的金属氧化物半导体场效应晶体管(mosfet)、结型场效应晶体管(jfet)、双极结型晶体管(bjt)、金属半导体场效应晶体管(mesfet)、绝缘栅场效应晶体管(igfet)、横向扩散金属氧化物半导体晶体管(ldmos)或其任何合适的组合。

[0147]

在本技术的一些方面,晶体管910、912两者都是nmos晶体管。晶体管910的栅极可以短路到晶体管912的栅极。在一方面,晶体管910除栅极外的第二端子可以短路到晶体管912除栅极外的第二端子。例如,晶体管910的源极可以短路到晶体管912的源极。晶体管912的第三端子(例如,漏极)可以耦合在脉冲电路103的输出端子与cut 101的端子之间。晶体管910的第三端子(例如,漏极)可以耦合到接收电路109的输入端子。例如,晶体管910的漏极可以短路到接收电路109的输入端子。在本技术的一些方面,晶体管910的基体端子可以短路到晶体管910的源极,并且晶体管912的基体端子可以短路到晶体管912的源极。

[0148]

在本技术的一些方面,包括对称开关907的开关电路908可以用于在发射模式期间阻挡双极性脉冲。除了对称开关907之外,开关电路908可以包括晶体管915。晶体管915可以是任何合适类型的晶体管,例如nmos晶体管。晶体管915可以被配置为使漏极短路到接收电路109的输入端子。晶体管915的源极可以短路到接地端子。晶体管915的基体端子可以短路到其源极。

[0149]

在本技术的一些方面,如图11中示意性地示出的,对称开关1107可以包括pmos晶体管1110、1112。如将理解的,在本技术的其他方面,对称开关可以包括不同数量的pmos晶体管。

[0150]

对称开关1107可以被配置为使得晶体管1110的栅极可以短路到晶体管1112的栅极。在本技术的一些方面,晶体管1110除栅极外的第二端子可以短路到晶体管1112除栅极外的第二端子。例如,晶体管1110的源极可以短路到晶体管1112的源极。晶体管1112的第三端子(例如,漏极)可以耦合在脉冲电路103的输出端子与cut 101的端子之间。晶体管1110的第三端子(例如,漏极)可以耦合到接收电路109的输入端子。在一些方面,晶体管1110的漏极可以短路到接收电路109的输入端子。在一些方面,晶体管1110的基体端子可以短路到晶体管1110的源极,并且晶体管1112的基体端子可以短路到晶体管1112的源极。在一些方面,开关电路1108可以包括对称开关1107和晶体管915。

[0151]

回到图9,开关电路908可以由任何合适类型和数量的控制信号控制,这些控制信号被配置为在发射模式期间阻挡由脉冲电路103所产生的双极性脉冲,并且进一步可以被配置为在接收模式期间将cut 101耦合到接收电路109。图10展示了时序图1000的示例,示出了根据本技术的一个方面的可以用于驱动图9的对称开关907的控制信号的示例。控制信号1002可以用于控制晶体管910、912的栅极g。控制信号1004可以用于控制晶体管910、912的源极s。控制信号1006可以用于控制晶体管915的栅极g2。在本技术的一些方面,控制信号1008可以用于接通和断开接收电路109。例如,控制信号1008可以用于启用或禁用接收电路109的电压供电,从而启用或禁用接收电路109。

[0152]

在时间t0之前,开关电路908可以被配置为在接收模式下操作。在该时段期间,控制信号1002可以大于控制信号1004。在本技术的一些方面,控制信号1002和控制信号1004

两者都可以大于零。以这种方式,晶体管910、912两者的栅极-源极电压都可以大于零,并且因此可以被配置为传导电流。控制信号1006可以为零或低于晶体管915的阈值电压,使得晶体管915可以保持在截止状态。在一方面,控制信号1008可以被设置为启用接收电路109的值。

[0153]

在时间t0与时间t1之间,控制信号1008可以被设置为禁用接收电路109的值。

[0154]

在时间t1与时间t2之间,控制信号1002可以被设置为等于控制信号1004的值;因此,晶体管910、912可以进入截止状态。在本技术的一些方面,控制信号1006可以被设置为高于晶体管915的阈值电压的值;因此,接收电路109的输入端子可以被强制为等于零的电压。

[0155]

在时间t2与时间t3之间,控制信号1002、1004可以被设置为负电压。在本技术的一些方面,控制信号1002、1004可以同时被设置为负电压。在一些方面,负电压可以等于图3所示的电压vn。

[0156]

在时间t3与时间t4之间,控制信号1002、1004可以被设置为零或脉冲电路103的偏置电压。在本技术的一些方面,控制信号1002、1004可以同时被设置为零或脉冲电路103的偏置电压。

[0157]

在时间t4与时间t5之间,控制信号1002可以被设置为使得晶体管910、912的栅极-源极电压可以高于用于传导电流的阈值的电压。在本技术的一些方面,控制信号1006可以被设置为低于晶体管915的阈值电压的值,使得与接收电路109的输入端子相关联的电压可以自由波动。

[0158]

在时间t5之后,控制信号1008可以被设置为启用接收电路109的值。

[0159]

在本技术的一些方面,在图10中,接收模式可以由t0之前和t5之后的时间段来定义,而发射模式可以由t0与t5之间的时间段来定义。在其他方面,在图10中,接收模式可以由t1之前和t4之后的时间段来定义,而发射模式可以由t1与t4之间的时间段来定义。在一些方面,t0可以等于t1。在一些方面,t1可以等于t2。在一些方面,t3可以等于t4。在一些方面,t4可以等于t5。

[0160]

图12至图16d示意性地展示了本技术的替代方面,用于在向超声设备的超声换能器发射脉冲期间保护超声设备的接收电路系统免受大电压信号的损坏。

[0161]

根据本技术的一个方面,对称开关7可以如图12和图13所示实施。对称开关可以由第一晶体管12和第二晶体管10构成。第二晶体管10的漏极d

10

可以连接到接收电路9。第一晶体管12的漏极d

12

可以连接到超声换能器1。例如,第一晶体管12的漏极d

12

可以连接在超声换能器1与脉冲电路3的输出端子之间。脉冲电路3的输入端子可以连接到传输解码器5。脉冲电路3可以具有类似于以上讨论的脉冲电路103的结构,并且传输解码器5可以类似于以上讨论的传输解码器105。

[0162]

在图12和图13中,这两个晶体管12、10是nmos晶体管;然而,如将理解的,本领域普通技术人员可以容易地将对称开关适配用于pmos晶体管。

[0163]

可选地,钳位二极管20可以连接在第一晶体管12和第二晶体管10的栅极g与第一晶体管12和第二晶体管10的源极s之间,如图12和图13所示。

[0164]

在发射(tx)模式期间,第一晶体管12和第二晶体管10是关断的,使得接收电路9可以与来自脉冲电路3的大电压信号隔离。例如,漏极d

10

可以处于0v。

[0165]

如图12所示,在tx模式期间,第一晶体管12和第二晶体管10的栅极可以连接在一起(统称为g)。在tx模式期间,第一晶体管12和第二晶体管10的源极可以连接在一起(统称为s)。在tx模式期间,第一晶体管12和第二晶体管10的基体可以连接在一起(统称为b)。在本技术的一个方面,源极s、栅极g和基体b可以保持在公共电势va。例如,在nmos晶体管12、10的情况下,公共电势va可以是-15v。

[0166]

在tx模式期间,脉冲电路3可以输出从-v

x

到 v

x

并且向后来回摆动的双极性脉冲。例如,双极性脉冲可以从-15v摆动到 15v。对称开关7可以保护接收电路9免受电压摆动的影响。

[0167]

在接收(rx)模式期间,第一晶体管12和第二晶体管10是导通的,使得来自超声换能器1的信号可以到达接收电路9。

[0168]

如图13所示,在rx模式期间,第一晶体管12和第二晶体管10的栅极g可以连接在一起。在rx模式期间,第一晶体管12和第二晶体管10的源极s可以连接在一起。在rx模式期间,第一晶体管12和第二晶体管10的基体b可以连接在一起。栅极g可以在足以使第一晶体管12和第二晶体管10导通的电势下浮动。例如,栅极g可以连接到电势vb,并且然后断开连接以使栅极g能够在电势vb下浮动。在该示例中,为了确保第一晶体管12和第二晶体管10可以在rx模式期间保持导通,栅极g可以间歇地连接到电势vb。例如,对于nmos晶体管,vb可以为 5v。

[0169]

在rx模式期间,第一晶体管12和第二晶体管10的基体b可以处于接地电势,或者在nmos晶体管的情况下,处于比栅极g的电势低的电势;基体b的电势可以在栅极g的浮动或固定电势以下浮动或固定。替代性地,在pmos晶体管的情况下,基体b的电势可以在栅极g的浮动或固定电势以上浮动或固定。

[0170]

图14a至图14c和图15示出了可以用于结合图12和图13所示的用于tx和rx模式的实施方式的示例电路配置,并且图16a至图16d示出了可以用于理解图12至图15的各种电路元件的状态的时序图和状态图的示例。

[0171]

根据本技术的一个方面,如图14a和图14b所示,对称开关7的第一晶体管12和第二晶体管10的栅极g可以连接到栅极控制器30。栅极控制器30可以由用于向栅极g提供导通电压v

on

的晶体管40构成;在rx模式期间,当要提供导通电压v

on

来导通晶体管10、12、47时,信号s5可以被提供给晶体管40的栅极。也就是说,信号s5可以用于控制晶体管10、12、47从非导电状态到导电状态的转变。例如,在nmos晶体管10、12的情况下,v

on

可以为 5v。如将理解的,v

on

可以等同于以上结合图12所讨论的vb。晶体管40可以是pmos晶体管。

[0172]

栅极控制器30还可以由用于向栅极g提供关断电压v

off

的晶体管41构成;在tx模式期间,当关断电压v

off

被提供给栅极g以关断晶体管10、12、47时,信号s6可以被提供给晶体管41的栅极。也就是说,信号s6可以用于将晶体管10、12、47从导电状态转变到非导电状态。例如,在nmos晶体管10、12的情况下,v

off

可以为-15v。如将理解的,v

off

可以等同于以上结合图12所讨论的va。晶体管41可以是nmos晶体管。

[0173]

如上所述,从栅极控制器30到对称开关7的栅极g的信号也可以用于控制晶体管47的栅极的断开和闭合。对称开关7的源极s可以连接到晶体管43,并且对称开关的基体b可以连接到晶体管42。晶体管42、43可以是pmos晶体管,并且晶体管47可以是nmos晶体管。在tx模式期间,信号s7可以被提供给晶体管42、43的栅极以使晶体管42、43导通,使得基体b和源

极s被设置为电势ve。例如,在nmos晶体管12、10的情况下,ve可以为-15v。如将理解的,ve可以等同于以上结合图12所讨论的va。如图14a所示,晶体管42可以连接到晶体管47。

[0174]

如上所述,由于对称开关7在半导体衬底中的制造设备结构,对称开关7可能会产生阱电容。例如,这两个晶体管12、10可以是设置在n掺杂衬底(“n阱”)中的p掺杂阱(“p阱”)中的nmos晶体管。p阱和n阱可以是高电压(“hv”)阱,这些高电压阱可以在信号路径中产生较大阱电容。为了减小或消除通过hv n阱耦合的噪声,对称开关7的基体b可以经由二极管21连接到hv n阱开关23,如图14a和图14c所示。hv n阱开关23可以用于在rx模式期间去除信号路径中的较大阱电容。

[0175]

如图14c所示,hv n阱开关23可以由三个晶体管44、45、46构成。晶体管45、46可以是pmos晶体管,并且晶体管44可以是nmos晶体管。hv n阱开关23可以保持在电势vf,或者允许经由晶体管45、46的断开或闭合而在电势vf下或接近该电势的电势下浮动。信号s4可以被提供到晶体管45的栅极以控制其断开和闭合。晶体管44、46的断开和闭合可以通过其经由二极管21与对称开关7的基体b的连接来控制。

[0176]

如图16a和图16b的时序图和状态图所示,在tx模式期间,信号s5可以使晶体管40关断并且信号s6可以使晶体管41导通,使得对称开关7的栅极g可以是断开的(例如,处于-15v的低电势)。hv n阱电路23可以处于 5v。可以控制晶体管42、43的断开和闭合的信号s7可以处于与源极s关断时一致的电势(例如,-10v的电势)。对称开关7的基体b和源极s可以经由晶体管42、43被驱动到-15v的低电势。接收电路9与对称开关7之间的位置d1处的电压可以是0v,并且对称开关与脉冲电路3之间的位置d2处的电压可以在脉冲电路3所使用的两个电源电压的电势之间来回摆动(例如, 15v和-15v)。

[0177]

在从tx模式到rx模式的转变期间,信号s5可以使晶体管40导通并且信号s6可以使晶体管41关断,使得对称开关7的栅极g可以是接通的并且栅极g可以从-15v的电势转变到 5v的电势。信号s5也可以使晶体管47导通。信号s7可以处于使晶体管42、43关断的电势(例如,-15v),使得对称开关7的基体b可以转变到接地电势或0v。位置d1、d2处的电压可以从0v转变到稍微升高的电势(例如, 0.75v)。

[0178]

在从tx模式到rx模式的转变期间,栅极g可以不浮动,而是可以由晶体管40设置为v

on

(例如, 5v)。

[0179]

在rx模式期间,在转变之后,信号s5可以使晶体管40关断,使得对称开关7的栅极g可以在大约 5v的电势下浮动。晶体管40可以由信号s5控制以间歇地使晶体管40导通,使得栅极g可以保持在大约 5v。信号s6可以不根据转变而改变,因此晶体管41可以保持关断。信号s7可以保持在转变的电势(例如,-15v)以保持晶体管42、43关断,使得对称开关7的基体b可以保持在接地电势或0v,并且使得对称开关7的源极s可以保持在 0.75v。hv n阱开关23也可以独立于栅极g或与栅极g一起在 5v处浮动。位置d1、d2处的电压可以保持在 0.75v,而栅极g可以是浮动的。

[0180]

图15示出了可以用作图14b的栅极控制器30的替代方案的栅极控制器32。在这种布置中,信号s3可以用于控制nmos晶体管52,类似于信号s6对晶体管41的控制。信号s1和s2可以用于控制pmos晶体管50、51,类似于信号s5对晶体管40的控制。pmos晶体管53的栅极和漏极可以连接在晶体管51的源极与晶体管50的漏极之间,并且二极管可以与晶体管53并联连接。

[0181]

图16c和图16d示出了用于从tx模式转变到rx模式的信号传导替代方案x1至x5的时序图和状态图。在替代方案x1和x2中,当处于rx模式时,信号s1和s2可能不会彼此跟踪,而是可能彼此不同。在替代方案x1和x2两者中,当信号s1保持在0v而信号s2处于 5v的浮动电势时(替代方案x1),或者当信号s1处于 5v的浮动电势而信号s2保持在0v时(替代方案x2),对称开关7的栅极g在rx模式下可以在 5v下浮动。在替代方案x3中,对称开关7的栅极g在rx模式下可能不浮动,而是可以保持在 5v;在这种情况下,信号s1和s2可以彼此跟踪,并且在rx模式下可以保持在0v。

[0182]

在替代方案x4中,信号s5可以保持在0v而信号s4可以保持在5v,在这种情况下,对称开关7的栅极g在rx模式下不能浮动,但是hv n阱开关23可以在rx模式下浮动。在替代方案x5中,信号s4可以保持在0v而信号s5可以保持在5v,在这种情况下,hv n阱开关23在rx模式下不能浮动,但是对称开关7的栅极g可以在rx模式下浮动。

[0183]

如将理解的,以上讨论的本技术的各方面可以提供一个或多个益处,其中一些益处可能已经在上文中提及或描述。以下描述了这些益处的示例。应当理解,并非本技术的所有方面都必须提供本文所述的所有益处。进一步地,应当理解,除了本文所述的那些益处之外,本技术的各方面可以提供其他益处。此外,本文呈现的示例是为了说明的目的而提供的,并且是非限制性示例。

[0184]

本技术的各方面提供了用于脉冲电路的电路系统,该脉冲电路被配置为产生双极性脉冲,这些双极性脉冲可以被超声设备的cut接收,而不会使超声设备的接收电路饱和。电路系统可以使得接收电路能够在存在双极性脉冲的情况下避免损坏,该接收电路可能包括未被设计成承受与双极性脉冲相关联的较大正负电压信号的部件。

[0185]

本技术的各方面提供了对称开关,这些对称开关被配置为在发射模式期间将接收电路与发射电路解耦,从而防止由双极性脉冲引起的对接收电路的损坏。

[0186]

时域和空域切趾脉冲的产生可能需要控制多级脉冲的能力。本技术的各方面可以提供一种反馈电路,该反馈电路被配置为在不借助使用附加电源电压的情况下执行时域和空域切趾,如果使用附加电源电压,则可能会不期望地增加旨在作为手持式探头的超声探头的大小。

[0187]

根据本文所述技术的装置可以以不同的配置体现。示例配置包括配置(1)至(2)的组合,如下:

[0188]

(1)一种装置,包括耦合在接收装置与超声换能器阵列之间的对称接收器开关阵列,其中:该对称接收器开关阵列的第一对称接收器开关由以下各项构成:第一晶体管,该第一晶体管具有第一栅极、第一源极、第一基体和第一漏极;以及第二晶体管,该第二晶体管具有第二栅极、第二源极、第二基体和第二漏极,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,该第一漏极连接到该阵列的第一超声换能器,该第二漏极连接到该接收装置,在该装置的脉冲发射(tx)模式期间,该第一栅极和该第二栅极以及该第一源极和该第二源极处于相同电势,并且,在该装置的接收(rx)模式期间:该第一栅极和该第二栅极处于第一浮动电势,或者该第一基体和该第二基体处于第一浮动电势,或者该第一栅极和该第二栅极以及该第一基体和该第二基体处于第一浮动电势。

[0189]

(2)如配置(1)所述的装置,其中,在该tx模式期间,该第一基体和该第二基体与该

第一源极和该第二源极处于相同电势。

[0190]

(3)如配置(1)至(2)中任一项所述的装置,其中,在该rx模式期间,该第一基体和该第二基体处于第二浮动电势。

[0191]

(4)如配置(1)至(3)中任一项所述的装置,其中:该第一漏极耦合到该第一对称接收器开关的输入端子,该第二漏极耦合到该第一对称接收器开关的输出端子,并且在该tx模式期间,该第二漏极处于固定电势。

[0192]

(5)如配置(1)至(4)中任一项所述的装置,其中:该第一晶体管是nmos晶体管,该第二晶体管是nmos晶体管,并且在该tx模式期间,该第二漏极处于比第一浮动电势高的电势。

[0193]

(6)如配置(1)至(5)中任一项所述的装置,其中:该第一晶体管是pmos晶体管,该第二晶体管是pmos晶体管,并且在该tx模式期间,该第二漏极处于比第一浮动电势低的电势。

[0194]

(7)如配置(1)至(6)中任一项所述的装置,其中:该第一漏极耦合到该第一对称接收器开关的输入端子,该第二漏极耦合到该第一对称接收器开关的输出端子,并且在该tx模式期间,该第二漏极处于接地电势。

[0195]

(8)如配置(1)至(7)中任一项所述的装置,其中,在该tx模式期间:该第一晶体管和该第二晶体管是关断的,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为负电势。

[0196]

(9)如配置(1)至(8)中任一项所述的装置,其中,在该tx模式期间,该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的负电势。

[0197]

(10)如配置(1)至(9)中任一项所述的装置,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0198]

(11)如配置(1)至(10)中任一项所述的装置,其中,在该tx模式期间:该第一晶体管和该第二晶体管是关断的,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为正电势。

[0199]

(12)如配置(1)至(11)中任一项所述的装置,其中,在该tx模式期间,该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的正电势。

[0200]

(13)如配置(1)至(12)中任一项所述的装置,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0201]

(14)如配置(1)至(13)中任一项所述的装置,其中,在该rx模式期间,该第一晶体管和该第二晶体管是导通的。

[0202]

(15)如配置(1)至(14)中任一项所述的装置,其中:该第一晶体管和该第二晶体管是nmos晶体管,并且在该rx模式期间,该第一栅极和该第二栅极的第一浮动电势为正电势。

[0203]

(16)如配置(1)至(15)中任一项所述的装置,其中,该第一栅极和该第二栅极选择性地连接到正电压源并与该正电压源断开连接以设置该第一浮动电势。

[0204]

(17)如配置(14)至(16)中任一项所述的装置,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0205]

(18)如配置(1)至(17)中任一项所述的装置,其中:该第一晶体管和该第二晶体管是pmos晶体管,并且在该rx模式期间,该第一栅极和该第二栅极的第一浮动电势为负电势。

[0206]

(19)如配置(1)至(18)中任一项所述的装置,其中,该第一栅极和该第二栅极选择性地连接到负电压源并与该负电压源断开连接以设置该第一浮动电势。

[0207]

(20)如配置(11)至(19)中任一项所述的装置,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0208]

根据本文所述技术的装置可以以不同的配置体现。示例配置包括配置(21)至(34)的组合,如下:

[0209]

(21)一种装置,包括耦合在接收装置与超声换能器阵列之间的对称接收器开关阵列,其中,该对称接收器开关阵列的第一对称接收器开关由包括第一栅极和第一源极的第一晶体管以及包括第二栅极和第二源极的第二晶体管构成,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,其中,在该装置的脉冲发射(tx)模式期间,该第一对称接收器开关是断开的,并且其中,在该装置的接收(rx)模式期间,该第一对称接收器开关是接通的。

[0210]

(22)如配置(21)所述的装置,其中,在该tx模式期间,该第一栅极和该第二栅极以及该第一源极和该第二源极处于相同电势。

[0211]

(23)如配置(21)至(22)中任一项所述的装置,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该tx模式期间,该第一栅极和该第二栅极、该第一源极和该第二源极以及该第一基体和该第二基体处于相同电势。

[0212]

(24)如配置(21)至(23)中任一项所述的装置,其中,在该rx模式期间,该第一栅极和该第二栅极处于浮动电势。

[0213]

(25)如配置(21)至(24)中任一项所述的装置,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于浮动电势。

[0214]

(26)如配置(21)至(25)中任一项所述的装置,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体以及该第一栅极和该第二栅极处于浮动电势。

[0215]

(27)如配置(21)至(26)中任一项所述的装置,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该tx模式期间,该第一基体和该第二基体以及该第一源极和该第二源极处于相同电势。

[0216]

(28)如配置(21)至(27)中任一项所述的装置,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于相同电势。

[0217]

(29)如配置(21)至(28)中任一项所述的装置,其中,在该rx模式期间,该第一基体和该第二基体处于接地电势。

[0218]

(30)如配置(21)至(29)中任一项所述的装置,其中,在该rx模式期间,该第一基体和该第二基体处于浮动电势。

[0219]

(31)如配置(21)至(30)中任一项所述的装置,其中,在该rx模式期间,该第一基体和该第二基体以及该第一源极和该第二源极处于相同电势。

[0220]

(32)如配置(21)至(31)中任一项所述的装置,其中:该第一晶体管是nmos晶体管并且进一步由第一基体构成,该第二晶体管是nmos晶体管并且进一步由第二基体构成,并

且在该rx模式期间,该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势低的电势。

[0221]

(33)如配置(21)至(32)中任一项所述的装置,其中:该第一晶体管是pmos晶体管并且进一步由第一基体构成,该第二晶体管是pmos晶体管并且进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势高的电势。

[0222]

(34)如配置(21)至(33)中任一项所述的装置,其中:该第一晶体管进一步由连接到该阵列的超声换能器的第一漏极构成,并且该第二晶体管进一步由连接到该接收装置的第二漏极构成。

[0223]

根据本文所述技术的超声设备可以以不同的配置体现。示例配置包括配置(35)至(48)的组合,如下:

[0224]

(35)一种超声设备,包括:超声换能器阵列;接收装置,该接收装置被配置为处理从该超声换能器阵列输出的电信号;以及对称开关阵列,该对称开关阵列耦合在该接收装置与该超声换能器阵列之间,其中,该对称开关阵列的第一对称开关由包括第一栅极和第一源极的第一晶体管以及包括第二栅极和第二源极的第二晶体管构成,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,其中,在该设备的脉冲发射(tx)模式期间,该第一对称开关是断开的,并且其中,在该设备的接收(rx)模式期间,该第一对称开关是接通的。

[0225]

(36)如配置(35)所述的超声设备,其中,在该tx模式期间,该第一栅极和该第二栅极以及该第一源极和该第二源极处于相同电势。

[0226]

(37)如配置(35)至(36)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该tx模式期间,该第一栅极和该第二栅极、该第一源极和该第二源极以及该第一基体和该第二基体处于相同电势。

[0227]

(38)如配置(35)至(37)中任一项所述的超声设备,其中,在该rx模式期间,该第一栅极和该第二栅极处于浮动电势。

[0228]

(39)如配置(35)至(38)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于浮动电势。

[0229]

(40)如配置(35)至(39)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体以及该第一栅极和该第二栅极处于浮动电势。

[0230]

(41)如配置(35)至(40)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该tx模式期间,该第一基体和该第二基体以及该第一源极和该第二源极处于相同电势。

[0231]

(42)如配置(35)至(41)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于相同电势。

[0232]

(43)如配置(35)至(42)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体处于接地电势。

[0233]

(44)如配置(35)至(43)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体处于浮动电势。

[0234]

(45)如配置(35)至(44)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体以及该第一源极和该第二源极处于相同电势。

[0235]

(46)如配置(35)至(45)中任一项所述的超声设备,其中:该第一晶体管是nmos晶体管并且进一步由第一基体构成,该第二晶体管是nmos晶体管并且进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势低的电势。

[0236]

(47)如配置(35)至(46)中任一项所述的超声设备,其中:该第一晶体管是pmos晶体管并且进一步由第一基体构成,该第二晶体管是pmos晶体管并且进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势高的电势。

[0237]

(48)如配置(35)至(47)中任一项所述的超声设备,其中:该第一晶体管进一步由连接到该阵列的超声换能器的第一漏极构成,并且该第二晶体管进一步由连接到该接收装置的第二漏极构成。

[0238]

根据本文所述技术的超声设备可以以不同的配置体现。示例配置包括配置(49)至(62)的组合,如下:

[0239]

(49)一种超声设备,包括:超声换能器;接收装置,该接收装置被配置为处理从该超声换能器输出的电信号;以及对称开关,该对称开关具有耦合到该超声换能器的输入端子和耦合到该接收装置的输出端子,其中,该对称开关由包括第一栅极和第一源极的第一晶体管以及包括第二栅极和第二源极的第二晶体管构成,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,其中,在该设备的脉冲发射(tx)模式期间,该对称开关是断开的,并且其中,在该设备的接收(rx)模式期间,该对称开关是接通的。

[0240]

(50)如配置(49)所述的超声设备,其中,在该tx模式期间,该第一栅极和该第二栅极以及该第一源极和该第二源极处于相同电势。

[0241]

(51)如配置(49)至(50)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该tx模式期间,该第一栅极和该第二栅极、该第一源极和该第二源极以及该第一基体和该第二基体处于相同电势。

[0242]

(52)如配置(49)至(51)中任一项所述的超声设备,其中,在该rx模式期间,该第一栅极和该第二栅极处于浮动电势。

[0243]

(53)如配置(49)至(52)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于浮动电势。

[0244]

(54)如配置(49)至(53)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体以及该第一栅极和该第二栅极处于浮动电势。

[0245]

(55)如配置(49)至(54)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该tx模式期间,该第一基体和

该第二基体以及该第一源极和该第二源极处于相同电势。

[0246]

(56)如配置(49)至(55)中任一项所述的超声设备,其中:该第一晶体管进一步由第一基体构成,该第二晶体管进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于相同电势。

[0247]

(57)如配置(49)至(56)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体处于接地电势。

[0248]

(58)如配置(49)至(57)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体处于浮动电势。

[0249]

(59)如配置(49)至(58)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体以及该第一源极和该第二源极处于相同电势。

[0250]

(60)如配置(49)至(59)中任一项所述的超声设备,其中:该第一晶体管是nmos晶体管并且进一步由第一基体构成,该第二晶体管是nmos晶体管并且进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势低的电势。

[0251]

(61)如配置(49)至(60)中任一项所述的超声设备,其中:该第一晶体管是pmos晶体管并且进一步由第一基体构成,该第二晶体管是pmos晶体管并且进一步由第二基体构成,并且在该rx模式期间,该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势高的电势。

[0252]

(62)如配置(49)至(61)中任一项所述的超声设备,其中:该第一晶体管进一步由连接到该阵列的超声换能器的第一漏极构成,并且该第二晶体管进一步由连接到该接收装置的第二漏极构成。

[0253]

根据本文所述技术的超声设备可以以不同的配置体现。示例配置包括配置(63)至(82)的组合,如下:

[0254]

(63)一种超声设备,包括:超声换能器阵列;接收装置,该接收装置被配置为处理从该超声换能器阵列输出的电信号;以及对称开关阵列,该对称开关阵列耦合在该接收装置与该超声换能器阵列之间,其中,该对称开关阵列的第一对称开关由以下各项构成:第一晶体管,该第一晶体管具有第一栅极、第一源极、第一基体和第一漏极;以及第二晶体管,该第二晶体管具有第二栅极、第二源极、第二基体和第二漏极,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,其中,该第一漏极连接到该阵列的第一超声换能器,其中,该第二漏极连接到该接收装置,其中,在该设备的脉冲发射(tx)模式期间,该第一栅极和该第二栅极以及该第一源极和该第二源极处于相同电势,并且其中,在该设备的接收(rx)模式期间:该第一栅极和该第二栅极处于第一浮动电势,或者该第一基体和该第二基体处于第一浮动电势,或者该第一栅极和该第二栅极以及该第一基体和该第二基体处于第一浮动电势。

[0255]

(64)如配置(63)所述的超声设备,其中,在该tx模式期间,该第一基体和该第二基体与该第一源极和该第二源极处于相同电势。

[0256]

(65)如配置(63)至(64)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体处于第二浮动电势。

[0257]

(66)如配置(63)至(65)中任一项所述的超声设备,其中:该第一漏极耦合到该第

一对称接收器开关的输入端子,该第二漏极耦合到该第一对称接收器开关的输出端子,并且在该tx模式期间,该第二漏极处于固定电势。

[0258]

(67)如配置(63)至(66)中任一项所述的超声设备,其中:该第一晶体管是nmos晶体管,该第二晶体管是nmos晶体管,并且在该tx模式期间,该第二漏极处于比第一浮动电势高的电势。

[0259]

(68)如配置(63)至(67)中任一项所述的超声设备,其中:该第一晶体管是pmos晶体管,该第二晶体管是pmos晶体管,并且在该tx模式期间,该第二漏极处于比第一浮动电势低的电势。

[0260]

(69)如配置(63)至(68)中任一项所述的超声设备,其中:该第一漏极耦合到该第一对称接收器开关的输入端子,该第二漏极耦合到该第一对称接收器开关的输出端子,并且在该tx模式期间,该第二漏极处于接地电势。

[0261]

(70)如配置(63)至(69)中任一项所述的超声设备,其中,在该tx模式期间:该第一晶体管和该第二晶体管是关断的,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为负电势。

[0262]

(71)如配置(63)至(70)中任一项所述的超声设备,其中,在该tx模式期间,该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的负电势。

[0263]

(72)如配置(63)至(71)中任一项所述的超声设备,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0264]

(73)如配置(63)至(72)中任一项所述的超声设备,其中,在该tx模式期间:该第一晶体管和该第二晶体管是关断的,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为正电势。

[0265]

(74)如配置(63)至(73)中任一项所述的超声设备,其中,在该tx模式期间,该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的正电势。

[0266]

(75)如配置(63)至(74)中任一项所述的超声设备,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0267]

(76)如配置(63)至(75)中任一项所述的超声设备,其中,在该rx模式期间,该第一晶体管和该第二晶体管是导通的。

[0268]

(77)如配置(63)至(76)中任一项所述的超声设备,其中:该第一晶体管和该第二晶体管是nmos晶体管,并且在该rx模式期间,该第一栅极和该第二栅极的第一浮动电势为正电势。

[0269]

(78)如配置(63)至(77)中任一项所述的超声设备,其中,该第一栅极和该第二栅极选择性地连接到正电压源并与该正电压源断开连接以设置该第一浮动电势。

[0270]

(79)如配置(76)至(78)中任一项所述的超声设备,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0271]

(80)如配置(63)至(79)中任一项所述的超声设备,其中:该第一晶体管和该第二晶体管是pmos晶体管,并且在该rx模式期间,该第一栅极和该第二栅极的第一浮动电势为负电势。

[0272]

(81)如配置(63)至(80)中任一项所述的超声设备,其中,该第一栅极和该第二栅极选择性地连接到负电压源并与该负电压源断开连接以设置该第一浮动电势。

[0273]

(82)如配置(73)至(81)中任一项所述的超声设备,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0274]

根据本文所述技术的超声设备可以以不同的配置体现。示例配置包括配置(83)至(102)的组合,如下:

[0275]

(83)一种超声设备,包括:超声换能器;接收装置,该接收装置被配置为处理从该超声换能器输出的电信号;以及对称开关,该对称开关具有耦合到该超声换能器的输入端子和耦合到该接收装置的输出端子,其中,该对称开关由以下各项构成:第一晶体管,该第一晶体管具有第一栅极、第一源极、第一基体和第一漏极;以及第二晶体管,该第二晶体管具有第二栅极、第二源极、第二基体和第二漏极,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,其中,该第一漏极连接到该阵列的第一超声换能器,其中,该第二漏极连接到该接收装置,其中,在该设备的脉冲发射(tx)模式期间,该第一栅极和该第二栅极以及该第一源极和该第二源极处于相同电势,并且其中,在该设备的接收(rx)模式期间:该第一栅极和该第二栅极处于第一浮动电势,或者该第一基体和该第二基体处于第一浮动电势,或者该第一栅极和该第二栅极以及该第一基体和该第二基体处于第一浮动电势。

[0276]

(84)如配置(83)所述的超声设备,其中,在该tx模式期间,该第一基体和该第二基体与该第一源极和该第二源极处于相同电势。

[0277]

(85)如配置(83)至(84)中任一项所述的超声设备,其中,在该rx模式期间,该第一基体和该第二基体处于第二浮动电势。

[0278]

(86)如配置(83)至(85)中任一项所述的超声设备,其中:该第一漏极耦合到该对称开关的输入端子,该第二漏极耦合到该对称开关的输出端子,并且在该tx模式期间,该第二漏极处于固定电势。

[0279]

(87)如配置(83)至(86)中任一项所述的超声设备,其中:该第一晶体管是nmos晶体管,该第二晶体管是nmos晶体管,并且在该tx模式期间,该第二漏极处于比第一浮动电势高的电势。

[0280]

(88)如配置(83)至(87)中任一项所述的超声设备,其中:该第一晶体管是pmos晶体管,该第二晶体管是pmos晶体管,并且在该tx模式期间,该第二漏极处于比第一浮动电势低的电势。

[0281]

(89)如配置(83)至(88)中任一项所述的超声设备,其中:该第一漏极耦合到该对称开关的输入端子,该第二漏极耦合到该对称开关的输出端子,并且在该tx模式期间,该第二漏极处于接地电势。

[0282]

(90)如配置(83)至(89)中任一项所述的超声设备,其中,在该tx模式期间:该第一晶体管和该第二晶体管是关断的,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为负电势。

[0283]

(91)如配置(83)至(90)中任一项所述的超声设备,其中,在该tx模式期间,该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的负电势。

[0284]

(92)如配置(83)至(91)中任一项所述的超声设备,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0285]

(93)如配置(83)至(92)中任一项所述的超声设备,其中,在该tx模式期间:该第一

晶体管和该第二晶体管是关断的,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为正电势。

[0286]

(94)如配置(83)至(93)中任一项所述的超声设备,其中,在该tx模式期间,该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的正电势。

[0287]

(95)如配置(83)至(94)中任一项所述的超声设备,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0288]

(96)如配置(83)至(95)中任一项所述的超声设备,其中,在该rx模式期间,该第一晶体管和该第二晶体管是导通的。

[0289]

(97)如配置(83)至(96)中任一项所述的超声设备,其中:该第一晶体管和该第二晶体管是nmos晶体管,并且在该rx模式期间,该第一栅极和该第二栅极的第一浮动电势为正电势。

[0290]

(98)如配置(83)至(97)中任一项所述的超声设备,其中,该第一栅极和该第二栅极选择性地连接到正电压源并与该正电压源断开连接以设置该第一浮动电势。

[0291]

(99)如配置(96)至(98)中任一项所述的超声设备,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0292]

(100)如配置(83)至(99)中任一项所述的超声设备,其中:该第一晶体管和该第二晶体管是pmos晶体管,并且在该rx模式期间,该第一栅极和该第二栅极的第一浮动电势为负电势。

[0293]

(101)如配置(83)至(100)中任一项所述的超声设备,其中,该第一栅极和该第二栅极选择性地连接到负电压源并与该负电压源断开连接以设置该第一浮动电势。

[0294]

(102)如配置(93)至(101)中任一项所述的超声设备,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0295]

一种使用根据本文所述技术的装置(例如,超声设备)的方法可以包括各种过程。示例过程包括过程(103)至(115)的组合,如下:

[0296]

(103)一种具有脉冲发射(tx)模式和接收(rx)模式的装置的方法,该装置包括超声换能器、被配置为处理从该超声换能器输出的电信号的接收器、以及具有耦合到该超声换能器的输入端子和耦合到该接收装置的输出端子的对称开关,该对称开关包括第一晶体管和第二晶体管,该第一晶体管包括第一栅极、第一源极、第一基体和第一漏极,该第二晶体管包括第二栅极、第二源极、第二基体和第二漏极,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,该方法包括:在该tx模式下,使该对称开关断开,并且在该rx模式下,使该对称开关接通。

[0297]

(104)如过程(103)所述的方法,其中,在该tx模式期间,在使该对称开关断开时,使该第一栅极和该第二栅极以及该第一源极和该第二源极处于相同电势。

[0298]

(105)如过程(103)至(104)中任一项所述的方法,其中,在该tx模式期间,在使该对称开关断开时,使该第一栅极和该第二栅极、该第一源极和该第二源极以及该第一基体和该第二基体处于相同电势。

[0299]

(106)如过程(103)至(105)中任一项所述的方法,其中,在该rx模式期间,在使该对称开关接通时,使该第一栅极和该第二栅极处于浮动电势。

[0300]

(107)如过程(103)至(106)中任一项所述的方法,其中,在该rx模式期间,在使该

对称开关接通时,使该第一基体和该第二基体处于浮动电势。

[0301]

(108)如过程(103)至(107)中任一项所述的方法,其中,在该rx模式期间,在使该对称开关接通时,使该第一基体和该第二基体以及该第一栅极和该第二栅极处于浮动电势。

[0302]

(109)如过程(103)至(108)中任一项所述的方法,在该tx模式期间,在使该对称开关断开时,将该第一基体和该第二基体以及该第一源极和该第二源极设置为处于相同电势。

[0303]

(110)如过程(103)至(109)中任一项所述的方法,其中,在该rx模式期间,在使该对称开关接通时,使该第一基体和该第二基体处于相同电势。

[0304]

(111)如过程(103)至(110)中任一项所述的方法,其中,在该rx模式期间,在使该对称开关接通时,使该第一基体和该第二基体处于接地电势。

[0305]

(112)如过程(103)至(111)中任一项所述的方法,其中,在该rx模式期间,在使该对称开关接通时,使该第一基体和该第二基体处于浮动电势。

[0306]

(113)如过程(103)至(112)中任一项所述的方法,其中,在该rx模式期间,在使该对称开关接通时,使该第一基体和该第二基体以及该第一源极和该第二源极处于相同电势。

[0307]

(114)如过程(103)至(113)中任一项所述的方法,其中:该第一晶体管是nmos晶体管,该第二晶体管是nmos晶体管,并且在该rx模式期间,在使该对称开关接通时,使该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势低的电势。

[0308]

(115)如过程(103)至(114)中任一项所述的方法,其中:该第一晶体管是pmos晶体管,该第二晶体管是pmos晶体管,并且在该rx模式期间,在使该对称开关接通时,使该第一基体和该第二基体处于比该第一栅极和该第二栅极的浮动电势高的电势。

[0309]

一种使用根据本文所述技术的装置(例如,超声设备)的方法可以包括各种过程。示例过程包括过程(116)至(135)的组合,如下:

[0310]

(116)一种具有脉冲发射(tx)模式和接收(rx)模式的装置的方法,该装置包括超声换能器、被配置为处理从该超声换能器输出的电信号的接收器、以及具有耦合到该超声换能器的输入端子和耦合到该接收装置的输出端子的对称开关,该对称开关包括第一晶体管和第二晶体管,该第一晶体管包括第一栅极、第一源极、第一基体和第一漏极,该第二晶体管包括第二栅极、第二源极、第二基体和第二漏极,其中,该第一栅极和该第二栅极彼此耦合,并且其中,该第一源极和该第二源极彼此耦合,该方法包括:通过使第一栅极和第二栅极以及第一源极和第二源极处于相同电势来进入tx模式;以及通过以下操作来进入该rx模式:使该第一栅极和该第二栅极处于第一浮动电势,或者使该第一基体和该第二基体处于该第一浮动电势,或者使该第一栅极和该第二栅极以及该第一基体和该第二基体处于该第一浮动电势。

[0311]

(117)如过程(116)所述的方法,其中,在进入该tx模式时,使该第一基体和该第二基体与该第一源极和该第二源极处于相同电势。

[0312]

(118)如过程(116)至(117)中任一项所述的方法,其中,在进入该rx模式时,使该第一基体和该第二基体处于第二浮动电势。

[0313]

(119)如过程(116)至(118)中任一项所述的方法,其中,在进入该tx模式时,使该

第二漏极处于固定电势。

[0314]

(120)如过程(116)至(119)中任一项所述的方法,其中:该第一晶体管是nmos晶体管,该第二晶体管是nmos晶体管,并且在进入该tx模式时,使该第二漏极处于比第一浮动电势高的电势。

[0315]

(121)如过程(116)至(120)中任一项所述的方法,其中:该第一晶体管是pmos晶体管,该第二晶体管是pmos晶体管,并且在进入该tx模式时,使该第二漏极处于比第一浮动电势低的电势。

[0316]

(122)如过程(116)至(121)中任一项所述的方法,其中,在进入该tx模式时,使该第二漏极处于接地电势。

[0317]

(123)如过程(116)至(122)中任一项所述的方法,其中:在进入该tx模式时,使该第一晶体管和该第二晶体管关断,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为负电势。

[0318]

(124)如过程(116)至(123)中任一项所述的方法,其中,在进入该tx模式时,使该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的负电势。

[0319]

(125)如过程(116)至(124)中任一项所述的方法,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0320]

(126)如过程(116)至(125)中任一项所述的方法,其中:在进入该tx模式时,使该第一晶体管和该第二晶体管关断,并且该第一栅极和该第二栅极以及该第一源极和该第二源极的相同电势为正电势。

[0321]

(127)如过程(116)至(126)中任一项所述的方法,其中,在进入该tx模式时,使该第一基体和该第二基体处于该第一栅极和该第二栅极以及该第一源极和该第二源极的正电势。

[0322]

(128)如过程(116)至(127)中任一项所述的方法,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0323]

(129)如过程(116)至(128)中任一项所述的方法,其中,在进入该rx模式时,使该第一晶体管和该第二晶体管导通。

[0324]

(130)如过程(116)至(129)中任一项所述的方法,其中:该第一晶体管和该第二晶体管是nmos晶体管,并且在进入该rx模式时,将该第一栅极和该第二栅极的第一浮动电势设置为正电势。

[0325]

(131)如过程(116)至(130)中任一项所述的方法,其中,该第一栅极和该第二栅极选择性地连接到正电压源并与该正电压源断开连接以设置该第一浮动电势。

[0326]

(132)如过程(129)至(131)中任一项所述的方法,其中,该正电势在以下范围内:1v至100v、或5v至20v、或10v至50v、或15v至75v。

[0327]

(133)如过程(116)至(132)中任一项所述的方法,其中:该第一晶体管和该第二晶体管是pmos晶体管,并且在进入该rx模式时,将该第一栅极和该第二栅极的第一浮动电势设置为负电势。

[0328]

(134)如过程(116)至(133)中任一项所述的方法,其中,该第一栅极和该第二栅极选择性地连接到负电压源并与该负电压源断开连接以设置该第一浮动电势。

[0329]

(135)如过程(126)至(134)中任一项所述的方法,其中,该负电势在以下范围内:-1v至-100v、或-5v至-20v、或-10v至-50v、或-15v至-75v。

[0330]

已经如此描述了本技术的若干方面,应当理解,本领域普通技术人员可以容易地想到各种更改、修改和改进。这种更改、修改和改进旨在落入本文所述技术的精神和范围内。因此,应当理解,对本技术的各方面的前述描述仅以示例的方式呈现,并且在所附权利要求及其等同物的范围内,这些方面的变更可以在其它方面以不同于具体描述的方式实践。另外,如果本文所述的两种或更多种特征、系统、物品、材料和/或方法并非相互矛盾,则这些特征、系统、物品、材料和/或方法的任何组合包括在本公开的范围内。

[0331]

此外,如所描述的,一些方面可以体现为一种或多种方法。作为该方法的一部分执行的动作可以按任何适合的方式进行排序。因此,可以构建以下实施例:其中,各个动作以与所示顺序不同的顺序来执行,从而可以包括尽管在说明性实施例中作为顺次动作示出但却是同时执行一些动作。

[0332]

上述方面和实施例的特征可以单独使用、一起使用或以两个或更多个的任何组合使用。

[0333]

本文定义和使用的所有定义应当理解为对字典定义、通过引用并入的文件中的定义和/或所定义术语的一般含义的控制。

[0334]

除非明确指出相反,否则如本文在本说明书和权利要求中使用的不定冠词“一个(a)”和“一种(an)”应理解成意指“至少一个”。

[0335]

说明书和/或权利要求中用于修饰特征的术语(如“第一”、“第二”、“第三”等)的使用本身并不暗含一个特征相对于另一个特征的任何优先权、优先级或顺序。

[0336]

如在本文的说明书和权利要求中使用的短语“和/或”应理解成意指如此联合的这些元素中的“任一者或两者”,即在一些情况下相结合地出现并且在其他情况下分开出现的元素。

[0337]

如本文在本说明书和权利要求中所使用的,短语“至少一个”在提及一个或多个元素的列表的情况下,应被理解为意指选自元素列表中任何一个或多个元素的至少一个元素,但不一定包括在该元素列表内具体列出的每个元素中的至少一个,并且不排除元素列表中的元素的任何组合。这个定义还允许除了该元素列表内具体指明的元素之外可以可选地存在短语“至少一个”所指代的元素,而无论与具体指出的那些元素相关还是不相关。

[0338]

术语“大约”和“约”可以用于意味着在一些实施例中在目标值的

±

20%之内,在一些实施例中在目标值的

±

10%之内,在一些实施例中在目标值的

±

5%之内,并且在一些实施例中还在目标值的

±

2%之内。术语“大致”和“约”可以包括目标值。

[0339]

在权利要求以及以上说明书中,所有过渡性短语,如“包括”、“包含”、“携带”、“具有”、“含有”、“涉及”、“容纳”、“由

……

构成”等应当被理解为是开放式的,即是指包含但不限于。过渡短语“由

……

组成”和“基本上由

……

组成”应分别是封闭式或半封闭式过渡短语。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。