技术特征:

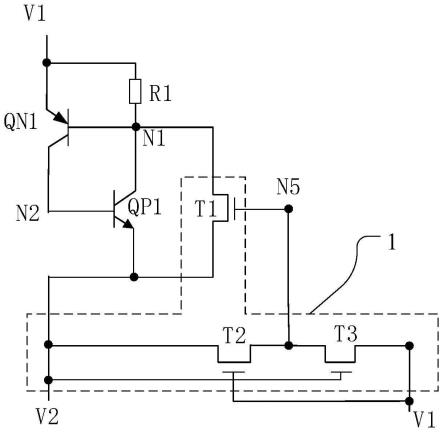

1.一种静电保护电路,其特征在于,所述静电保护电路包括:第一pnp型三极管,发射极连接第一信号端,基极连接第一节点,集电极连接第二节点,其中,所述第一信号端连接所述第一节点;第一npn型三极管,发射极连接第二信号端,基极连接所述第二节点,集电极连接所述第一节点;控制电路,连接所述第一信号端、第二信号端、第一节点,用于根据所述第一信号端和第二信号端的信号将所述第一信号端和第二信号端中的低电平信号端连接到所述第一节点。2.根据权利要求1所述的静电保护电路,其特征在于,所述静电保护电路还包括:第二pnp型三极管,发射极连接第二信号端,基极连接第三节点,集电极连接第四节点;第二npn型三极管,发射极连接所述第一信号端,基极连接所述第四节点,集电极连接所述第三节点;所述控制电路还连接所述第三节点,用于根据所述第一信号端和第二信号端的信号将所述第一信号端和第二信号端中的低电平信号端连接到所述第三节点。3.根据权利要求2所述的静电保护电路,其特征在于,所述控制电路包括:第一晶体管,第一极连接所述第一节点,第二极连接所述第二信号端,栅极连接第五节点;第二晶体管,第一极连接所述第二信号端,第二极连接所述第五节点,栅极连接所述第一信号端;第三晶体管,第一极连接所述第一信号端,第二极连接所述第五节点,栅极连接所述第二信号端;第四晶体管,第一极连接所述第三节点,第二极连接所述第一信号端,栅极连接所述第五节点;其中,所述第一晶体管、第四晶体管同为gg-nmos,所述第二晶体管、第三晶体管同为n型晶体管。4.根据权利要求1所述的静电保护电路,其特征在于,所述控制电路包括:第五晶体管,第一极连接所述第二信号端,第二极连接第五节点,栅极连接所述第一信号端;第六晶体管,第一极连接所述第一信号端,第二极连接所述第五节点,栅极连接所述第二信号端;其中,所述第五节点连接所述第一节点,且所述第五晶体管和所述第六晶体管为n型晶体管。5.根据权利要求4所述的静电保护电路,其特征在于,所述静电保护电路还包括:至少一个第一二极管,至少一个所述第一二极管串联于所述第一节点和第五节点之间,且所述第一节点连接所述第一二极管的阳极,所述第五节点连接所述第一二极管的阴极。6.根据权利要求5所述的静电保护电路,其特征在于,所述静电保护电路还包括:第二pnp型三极管,发射极连接第二信号端,基极连接第三节点,集电极连接第四节点;第二npn型三极管,发射极连接所述第一信号端,基极连接所述第四节点,集电极连接

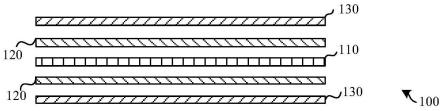

所述第三节点;其中,所述第三节点连接所述第一节点;第二二极管,所述第二二极管的阳极连接所述第一信号端,阴极连接所述第一节点;第三二极管,所述第三二极管的阳极连接所述第二信号端,阴极连接所述第三节点。7.根据权利要求1所述的静电保护电路,其特征在于,所述静电保护电路还包括:第四二极管,阳极连接所述第二信号端,阴极连接所述第一信号端;第二pnp型三极管,发射极连接所述第一信号端,基极连接第三节点,集电极连接第四节点;第二npn型三极管,发射极连接第三信号端,基极连接所述第四节点,集电极连接所述第三节点;第五二极管,阳极连接所述第三信号端,阴极连接所述第一信号端;所述控制电路还连接所述第三节点,用于根据所述第一信号端和第三信号端的信号将所述第一信号端和第三信号端中的低电平信号端连接到所述第三节点。8.根据权利要求7所述的静电保护电路,其特征在于,所述控制电路包括:第一晶体管,第一极连接所述第一节点,第二极连接所述第二信号端,栅极连接第五节点;第二晶体管,第一极连接所述第二信号端,第二极连接所述第五节点,栅极连接所述第一信号端;第三晶体管,第一极连接所述第一信号端,第二极连接所述第五节点,栅极连接所述第二信号端;第四晶体管,第一极连接所述第三节点,第二极连接所述第三信号端,栅极连接第六节点;第七晶体管,第一极连接所述第三信号端,第二极连接所述第六节点,栅极连接所述第一信号端;第八晶体管,第一极连接所述第一信号端,第二极连接所述第六节点,栅极连接所述第三信号端;其中,所述第一晶体管、第四晶体管同为gg-nmos,所述第二晶体管、第三晶体管、第七晶体管、第八晶体管同为n型晶体管。9.一种静电保护结构,其特征在于,所述静电保护结构包括权利要求1所述的静电保护电路,所述静电保护结构包括:半导体衬底;第一p型阱,位于所述半导体衬底内;第一n型阱,位于所述半导体衬底内;第一p型掺杂部,位于所述第一n型阱内,且电连接所述静电保护结构的第一信号端;第一n型掺杂部,位于所述第一n型阱内,与所述第一p型掺杂部间隔设置,且电连接所述静电保护结构的第一信号端;第二n型掺杂部,位于所述第一p型阱内,且电连接所述静电保护结构的第二信号端;第三n型掺杂部,部分位于所述第一p型阱内,部分位于所述第一n型阱内;第一栅极绝缘层,位于所述第一p型阱背离所述半导体衬底的一侧,且所述第一栅极绝

缘层在所述半导体衬底上的正投影至少部分位于所述第三n型掺杂部在所述半导体衬底上的正投影和所述第二n型掺杂部在所述半导体衬底上的正投影之间;第一栅极层,位于所述第一栅极绝缘层背离所述半导体衬底的一侧;选通电路,连接所述静电保护结构的第一信号端、第二信号端、第一栅极层,用于根据所述第一信号端和第二信号端的信号将所述第一栅极层连接到所述第一信号端和第二信号端中的低电平信号端。10.根据权利要求9所述的静电保护结构,其特征在于,所述静电保护结构还包括:第二n型阱,位于所述第一p型阱远离所述第一n型阱的一侧;第二p型掺杂部,位于所述第二n型阱内,且电连接所述静电保护结构的第二信号端;第四n型掺杂部,位于所述第二n型阱内,与所述第二p型掺杂部间隔设置,且电连接所述静电保护结构的第二信号端;第五n型掺杂部,位于所述第一p型阱内,与所述第二n型掺杂部间隔设置,且电连接所述静电保护结构的第一信号端;第六n型掺杂部,部分位于所述第一p型阱内,部分位于所述第二n型阱内;第二栅极绝缘层,位于所述第一p型阱背离所述半导体衬底的一侧,且所述第二栅极绝缘层在所述半导体衬底上的正投影至少部分位于所述第五n型掺杂部在所述半导体衬底上的正投影和所述第六n型掺杂部在所述半导体衬底上的正投影之间;第二栅极层,位于所述第二栅极绝缘层背离所述半导体衬底的一侧;所述选通电路还连接所述第二栅极层,用于根据所述第一信号端和第二信号端的信号将所述第二栅极层连接到所述第一信号端和第二信号端中的低电平信号端。11.根据权利要求10所述的静电保护结构,其特征在于,所述选通电路包括:第二晶体管,第一极连接所述第二信号端,第二极连接所述第一栅极层和所述第二栅极层,栅极连接所述第一信号端;第三晶体管,第一极连接所述第一信号端,第二极连接所述第一栅极层和所述第二栅极层,栅极连接所述第二信号端。12.一种静电保护结构,其特征在于,所述静电保护结构包括权利要求1所述的静电保护电路,所述静电保护结构包括:半导体衬底;第一p型阱,位于所述半导体衬底内;第一n型阱,位于所述半导体衬底内;第二掺杂阱,位于所述半导体衬底内;第一p型掺杂部,位于所述第一n型阱内,且电连接所述静电保护结构的第一信号端;第一n型掺杂部,位于所述第一n型阱内,且与所述第一p型掺杂部间隔设置;第二n型掺杂部,位于所述第一p型阱内,且电连接所述静电保护结构的第二信号端;第二p型掺杂部,位于所述第二掺杂阱内,且电连接所述第一n型掺杂部;第三n型掺杂部,位于所述第二掺杂阱内,且与所述第二p型掺杂部间隔设置;选通电路,连接所述静电保护结构的第一信号端、第二信号端、第三n型掺杂部,用于根据所述第一信号端和第二信号端的信号将所述第三n型掺杂部连接到所述第一信号端和第二信号端中的低电平信号端。

13.根据权利要求12所述的静电保护结构,其特征在于,所述静电保护结构包括多个所述第二掺杂阱、多个所述第二p型掺杂部、多个所述第三n型掺杂部;多个所述第二掺杂阱间隔设置,多个所述第二p型掺杂部与多个所述第二掺杂阱一一对应设置,所述第二p型掺杂部位于与其对应的所述第二掺杂阱内;多个所述第三n型掺杂部与多个所述第二掺杂阱一一对应设置,所述第三n型掺杂部位于与其对应的所述第二掺杂阱内;所述第一n型掺杂部电连接多个所述第二p型掺杂部中的任一个所述第二p型掺杂部;多个所述第二掺杂阱通过位于其内的所述第二p型掺杂部、第三n型掺杂部依次串联,在相邻连接的两所述第二掺杂阱中,位于不同所述第二掺杂阱中的第二p型掺杂部和第三n型掺杂部电连接;多个所述第二掺杂阱包括尾部第二掺杂阱,所述尾部第二掺杂阱通过其余所述第二掺杂阱连接所述第一n型掺杂部,所述选通电路连接尾部第二掺杂阱中的第三n型掺杂部。14.根据权利要求12所述的静电保护结构,其特征在于,所述静电保护结构还包括:第三p型阱,位于所述半导体衬底内,且位于所述第一p型阱和所述第二掺杂阱之间;第二n型阱,位于所述半导体衬底内,且位于所述第三p型阱和所述第二掺杂阱之间;第三p型掺杂部,位于所述第二n型阱内,且电连接所述静电保护结构的第二信号端;第四n型掺杂部,位于所述第二n型阱内,且与所述第三p型掺杂部间隔设置,所述第四n型掺杂部电连接所述第一n型掺杂部;第五n型掺杂部,位于所述第三p型阱内,所述第五n型掺杂部电连接所述静电保护结构的第一信号端;第四p型掺杂部,位于所述第三p型阱内,与所述第五n型掺杂部间隔设置,且电连接所述静电保护结构的第一信号端;第五p型掺杂部,位于所述第一p型阱内,与所述第二n型掺杂部间隔设置,且电连接所述静电保护结构的第二信号端。15.根据权利要求12所述的静电保护结构,其特征在于,所述选通电路包括:第五晶体管,第一极连接所述第二信号端,第二极连接所述第三n型掺杂部,栅极连接所述第一信号端;第六晶体管,第一极连接所述第一信号端,第二极连接所述所述第三n型掺杂部,栅极连接所述第二信号端;其中,所述第五节点连接所述第一节点,且所述第五晶体管和所述第六晶体管为n型晶体管。16.一种静电保护结构,其特征在于,所述静电保护结构包括权利要求1所述的静电保护电路,所述静电保护结构包括:半导体衬底;第一p型阱,位于所述半导体衬底内;n型深阱,位于所述半导体衬底内;第一n型阱,位于所述半导体衬底内,部位位于所述n型深阱和所述第一p型阱之间,且部分位于所述n型深阱内;第一p型掺杂部,位于所述n型深阱内,且电连接所述静电保护结构的第一信号端;

第一n型掺杂部,位于所述n型深阱内,与所述第一p型掺杂部间隔设置,且电连接所述静电保护结构的第一信号端;第二n型掺杂部,位于所述第一p型阱内,且电连接所述静电保护结构的第二信号端;第三n型掺杂部,部分位于所述第一p型阱内,部分位于所述第一n型阱内;第一栅极绝缘层,位于所述第一p型阱背离所述半导体衬底的一侧,且所述第一栅极绝缘层在所述半导体衬底上的正投影至少部分位于所述第三n型掺杂部在所述半导体衬底上的正投影和所述第二n型掺杂部在所述半导体衬底上的正投影之间;第一栅极层,位于所述第一栅极绝缘层背离所述半导体衬底的一侧;第一选通电路,连接所述静电保护结构的第一信号端、第二信号端、第一栅极层,用于根据所述第一信号端和第二信号端的信号将所述第一栅极层连接到所述第一信号端和第二信号端中的低电平信号端。17.根据权利要求16所述的静电保护结构,其特征在于,所述静电保护结构还包括:第二p型阱,位于所述n型深阱内;第二p型掺杂部,位于所述n型深阱内,与所述第一n型掺杂部、第一p型掺杂部间隔设置,且电连接所述静电保护结构的第一信号端;第四n型掺杂部,位于所述第二p型阱内,电连接所述静电保护结构的第三信号端;第五n型掺杂部,部分位于所述第二p型阱内,部分位于所述n型深阱内;第二栅极绝缘层,位于所述第二p型阱背离所述半导体衬底的一侧,且所述第二栅极绝缘层在所述半导体衬底上的正投影至少部分位于所述第四n型掺杂部在所述半导体衬底上的正投影和所述第五n型掺杂部在所述半导体衬底上的正投影之间;第二栅极层,位于所述第二栅极绝缘层背离所述半导体衬底的一侧;第二选通电路,连接所述静电保护结构的第一信号端、第三信号端、第二栅极层,用于根据所述第一信号端和第三信号端的信号将所述第二栅极层连接到所述第一信号端和第三信号端中的低电平信号端;第三p型掺杂部,位于所述第一p型阱内,与所述第二n型掺杂部、第三n型掺杂部间隔设置,且电连接所述静电保护结构的第二信号端;第四p型掺杂部,位于所述第二p型阱内,与所述第四n型掺杂部、第五n型掺杂部间隔设置,且电连接所述静电保护结构的第三信号端。18.根据权利要求17所述的静电保护结构,其特征在于,所述第一选通电路包括:第二晶体管,第一极连接所述第二信号端,第二极连接所述第一栅极层,栅极连接所述第一信号端;第三晶体管,第一极连接所述第一信号端,第二极连接所述第一栅极层,栅极连接所述第二信号端;所述第二选通电路包括:第七晶体管,第一极连接所述第三信号端,第二极连接所述第二栅极层,栅极连接所述第一信号端;第八晶体管,第一极连接所述第一信号端,第二极连接所述第二栅极层,栅极连接所述第三信号端;其中,所述第二晶体管、第三晶体管、第七晶体管、第八晶体管同为n型晶体管。

19.一种芯片,其特征在于,包括权利要求1-8任一项所述的静电保护电路。20.一种芯片,其特征在于,包括权利要求9-19任一项所述的静电保护结构。

技术总结

本公开涉及半导体技术领域,提出一种静电保护电路、静电保护结构、芯片,静电保护电路包括:第一PNP型三极管、第一NPN型三极管、控制电路,第一PNP型三极管的发射极连接第一信号端,基极连接第一节点,集电极连接第二节点,其中,第一信号端连接第一节点;第一NPN型三极管的发射极连接第二信号端,基极连接第二节点,集电极连接第一节点;控制电路连接第一信号端、第二信号端、第一节点,用于根据第一信号端和第二信号端的信号将第一信号端和第二信号端中的低电平信号端连接到第一节点。该静电保护电路具有较高的稳定性。电路具有较高的稳定性。电路具有较高的稳定性。

技术研发人员:许杞安

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2022.04.07

技术公布日:2022/6/10

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。