用于提供水分和质子阻挡部的集成电路器件的钝化层

1.相关申请的交叉引用

2.本技术要求于2020年12月16日提交的美国临时申请第63/126,096号专利的优先权,其公开内容通过引用并入本文。

技术领域

3.本发明总体上涉及集成电路器件,并且具体地涉及用于这种集成电路器件的钝化层,该钝化层提供防止污染物(例如水分和质子)侵入的阻挡部。

背景技术:

4.参考图1,其示出了集成电路器件10的一部分的横截面。该实施例中所示的器件例如是垂直栅极n沟道mosfet类型的分立功率晶体管。

5.半导体衬底12轻掺杂有第一类型掺杂剂(例如n型)。半导体衬底12包括顶面14和底面16。半导体衬底12的外围边缘表面18连接顶面14和底面16。半导体衬底12形成分立功率晶体管的漏极区。底面16处的金属层58提供漏极(d)电接触部。金属层58可以例如由包括以下项的层堆叠构成:钛(ti)层;镍(ni)或镍钒合金(niv)层;和银(ag)或金(au)层。

6.多个沟槽20从顶面14延伸到半导体衬底12中。沟槽20的深度小于半导体衬底12的厚度。在一个实施例中,每个沟槽20具有宽度(在横截面的平面内延伸)和长度(垂直于宽度延伸并在平面中进出横截面)。在一个实施例中,长度显著大于宽度,因此每个沟槽20是延伸进出横截面并且在俯视图中具有矩形形状的条形沟槽。每个沟槽20由绝缘衬里22加衬,每个沟槽的其余部分由形成分立功率晶体管栅电极的电导体24填充。在一个实施例中,绝缘衬里22由介电材料、例如氧化物制成,并且电导体24由导电材料制成,例如多晶硅(如果需要,其可以掺杂有合适的掺杂物种类/类型)。

7.半导体衬底12还包括掺杂有第二类型掺杂剂(例如p型)的第一半导体阱26。第一半导体阱26具有从顶面14延伸的深度,该深度小于沟槽20的深度。第一半导体阱26形成分立功率晶体管的体(沟道)区。

8.在半导体衬底12的周边处的外围终止区pr包括掺杂有第二类型掺杂剂(例如p型)的第二半导体阱27。第二半导体阱27具有从顶面14延伸的深度,该深度大于沟槽20的深度。第二半导体阱27形成分立功率晶体管的环区。

9.半导体衬底12还包括掺杂有第一类型掺杂剂的半导体区28。半导体区28具有从顶面14延伸的深度,该深度小于半导体阱26的深度。半导体区28形成分立功率晶体管的源极区。半导体区28并不延伸跨越半导体衬底12的整个顶面14,而是仅存在于大体对应于存在沟槽20的区域的有源区ar中。

10.场氧化区30被提供在半导体衬底12的顶面14处,位于有源区ar外部的外围区pr中,并与外围边缘表面18相邻。该场氧化区30可以例如围绕有源区ar。

11.沉积预金属化介电层32以覆盖半导体衬底12的顶面14和氧化区30。预金属化介电层32可以由介电材料制成,例如原硅酸四乙酯(四乙氧基硅烷-teos)。在一个实施例中,预

金属化介电层32可以包括层堆叠,包括覆盖半导体衬底12的顶面14和氧化区30的teos层和覆盖teos层的硼和磷掺杂的teos(bpteos)层。在另一个实施例中,预金属化介电层32可以包括层堆叠,该层堆叠包括覆盖半导体衬底12的顶面14和氧化区30的teos层和覆盖teos层的磷掺杂的teos(pteos)层。

12.多个沟槽34延伸穿过预金属化介电层32并进入半导体衬底12。沟槽34的深度小于半导体阱26的深度并大于半导体区域28的深度。因此,沟槽34完全延伸穿过预金属化介电层32和半导体区域28,并且部分地进入半导体阱26中。在一个实施例中,每个沟槽34具有宽度(在横截面的平面中延伸)和长度(垂直于宽度延伸并在平面内进出横截面)。在一个实施例中,长度显著大于宽度,因此每个沟槽34是延伸进出横截面并且在俯视图中具有矩形形状的条形沟槽。每个沟槽34位于两个沟槽20之间(并平行于两个沟槽延伸)。预金属化介电层32的上表面以及每个沟槽34的侧壁和底部都衬有层堆叠36,层堆叠包括例如薄金属层和薄金属氮化物层。薄金属层可以例如由钛制成,并且薄金属氮化物层可以例如由氮化钛(tin)材料制成。每个沟槽34的其余部分由形成分立功率晶体管的源极和体接触部的电导体38填充。电导体38可以例如由钨(w)材料制成。

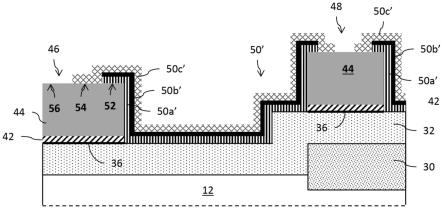

13.在薄金属氮化物层36之上沉积第一金属层42。该第一金属层42可以例如由钛(ti)制成。

14.在第一金属层42之上沉积第二金属层44。第二金属层44可以例如由铝(al)或铜和铝的合金(alcu)制成。

15.第二金属层44、第一金属层42和金属/金属氮化物层堆叠36被光刻图案化,以限定源极(s)电接触部46和栅极(g)电接触部48。

16.在不存在源极(s)电接触部46和栅极(g)电接触部48的区域中,光刻图案化使预金属化介电层32的顶面暴露。钝化层50沉积在源(s)电接触部46、栅极(g)电接触部48和预金属化介电层32的暴露上表面上。源极(s)电接触部46和栅极(g)电接触部48处的钝化层50配置的细节接触在图2中示出。在一个实施例中,钝化层50可以包括teos层50a、或氮化硅(sin)层50b、或包括teos层50a和氮化硅(sin)层50b的层堆叠。teos层50a可以例如具有大约的厚度,并且sin层50b可以具有例如大约的厚度。钝化层50被光刻图案化以形成暴露源极(s)电接触部46和栅极(g)电接触部48的上表面的开口。

17.提供钝化层50以抑制污染物(例如水分和质子)侵入。然而,应力可导致在钝化层50中形成裂纹。污染物可通过裂纹进入并导致器件故障。例如,水分渗透会导致温度湿度偏差(thb)可靠性故障,并且质子侵入会导致高温反向偏置(htrb)可靠性故障。

18.本领域需要一种钝化层,该钝化层可以提供针对污染物(例如水分和质子)侵入的改进阻挡部。

技术实现要素:

19.在一个实施例中,一种集成电路器件包括:金属接触部,具有顶面和侧壁,金属接触部的顶面包括第一表面部分、第二表面部分和第三表面部分;钝化层在金属接触部的侧壁上、并且在金属接触部的顶面的第一和第二表面部分上延伸。

20.钝化层包括层堆叠,层堆叠包括:原硅酸四乙酯(teos)层;在teos层顶部上的磷掺杂teos(pteos)层;以及位于pteos层顶部上的高密度富硅氮化物层。

21.teos层和pteos层在金属接触部的顶面的第一表面部分之上延伸,但不在金属接触部的顶面的第二和第三表面部分之上延伸。

22.高密度富硅氮化物层在金属接触部的顶面的第一和第二表面部分之上延伸,但不在金属接触部顶面的第三表面部分之上延伸。

附图说明

23.为了更好地理解实施例,现在将仅通过示例的方式参考附图,其中:

24.图1示出了现有技术中的集成电路器件的一部分的横截面;

25.图2示出了图1的集成电路器件的源极电接触部和栅极电接触部处的钝化层配置的细节;

26.图3示出了基于图1的、根据本技术的集成电路器件的源极电接触部和栅极电接触部处的钝化层配置的细节;

27.图4示出了根据本技术的钝化层配置的示例的扫描电子显微照片;

28.图5a-5e示出了根据本技术的用于制造图3和4的钝化层配置的制造工艺的步骤;

29.图6示出了基于图1的、根据本技术的集成电路器件的源极电接触部和栅极电接触部处的钝化层配置的细节;

30.图7示出了n/si比与富si氮化硅材料的折射率之间的关系;以及

31.图8a-8c示出了根据本技术的利用钝化层配置的其他集成电路器件的横截面。

具体实施方式

32.现在参考图3和图6,它们示出了图1的集成电路器件的源极电接触部46和栅极电接触部48处的钝化层50'配置的细节。在该实施例中,钝化层50'包括层堆叠,层堆叠包括:teos层50a'、覆盖teos层50a'的磷掺杂teos(pteos)层50b'、和氮化硅(sin)层50c'。teos层50a'可以例如具有大约范围内的厚度,pteos层50b'可以具有例如大约范围内厚度,并且sin层50c'可以具有例如大约范围内的厚度。在图6所示的实施方式中,通过在pteos层50b'与sin层50c'之间使用薄硅闪层70,可以增强sin层50c'在金属层44上的粘附力。例如,硅闪层70可以具有小于的厚度。钝化层50被光刻图案化以形成暴露源极(s)电接触部46和栅极(g)电接触部48的上表面的开口。

33.teos层50a'提供由比氮化硅软的材料制成的层,以提供应力释放结构,并且还呈现相对于第二金属层44的铝材料的良好粘附特性。teos层50a'还提供了抑制磷从pteos层50b'扩散的扩散阻挡部。pteos层50b'用作呈现质子h 吸杂中心的吸杂层。sin层50c'优选地实施为高密度富硅氮化物(在本领域中称为“黄色氮化物”)并且用作防止污染物例如质子h 和水分渗透的防潮阻挡部。

34.图4示出了相对于由铝制成的接触部(c)的钝化层50'配置的示例的扫描电子显微照片。

35.在源极(s)电接触部46和栅极(g)电接触部48不存在(见右侧)的区域中,用于钝化层50'的堆叠的所有三个层50a'、50b'和50c'在预金属化介电层32的暴露上表面之上延伸。

用于钝化层50'的堆叠的所有三个层50a'、50b'和50c'进一步在接触部c的侧壁(s)之上(即,在光刻图案化层42和44的侧边缘表面上)延伸。用于钝化层50'的堆叠的三个层50a'、50b'和50c'进一步在接触部c的顶面的第一表面部分52之上(即,在光刻图案化层44的顶面上)延伸。然而,只有sin层50c'在接触部c的顶面的第二表面部分54之上延伸。sin层50c'(连同闪层70,当存在时)在从第一表面部分52到第二表面部分54的过渡处在层50a'、50b'的侧边缘表面上延伸。接触部c的顶面的第三表面部分56没有被任何钝化层50'覆盖。此外,sin层50c'在层50a'、50b'的侧壁s1之上延伸。

36.钝化层50'的制造需要使用两个掩模来对堆叠的三个层50a'、50b'和50c'(加上层70,如果存在)进行光刻图案化。制造过程的步骤如图5a-5e所示。在图5a中,层50a'、50b'沉积在金属接触部c(44)之上。层50a'和50b'可以例如使用等离子体增强化学气相沉积(pecvd)来沉积。在图5b中,第一掩模60由显影的光刻胶形成。第一掩模60覆盖金属接触部的顶面的第一表面部分52。然后进行蚀刻以去除层50a'、50b'未被第一掩模60覆盖的部分。然后去除第一掩模60。在图5c中,层50c'(具有插入的硅闪层70,如果需要,参见图6)被共形地沉积以覆盖图案化层50a'、50b'以及金属接触部的顶面的第二和第三表面部分54和56。层50c'可以例如使用基于sih4的等离子体增强化学气相沉积(pecvd)来沉积。sin层50c'的化学计量例如可以包括si

x

ny,其中键合比(bond ratio)x:y例如可通过分析技术来确定,分析技术诸如r射线光电子能谱(xps)、傅里叶变换红外光谱(ftis)或卢瑟福的背向散射(rbs),显示n/si比小于约1.3(或x:y大于3:4)和折射率(例如通过光学椭圆偏光法测量)大于2(参见图7)。在图5d中,第二掩模62由显影的光刻胶形成。第二掩模62覆盖金属接触部顶面的第一和第二表面部分52和54。然后进行蚀刻以去除层50c'未被第二掩模62覆盖的部分,从而在金属接触部的顶面的第三表面部分56之上提供接触部开口64。然后去除第二掩模62。结果如图5e所示。

37.虽然图3和图6示出了钝化层50'结合功率mosfet晶体管的使用,但应当理解,钝化层50'可以与任何合适的集成电路器件的金属接触部/接合焊盘结合使用。此类器件的示例包括但不限于:屏蔽栅极沟槽功率mosfet(图8a),其中在源极和/或栅极接触部处提供钝化;沟槽栅极场截止igbt(图8b),其中在发射极和/或栅极接触部处提供钝化;超结mosfet(图8c),其中在源极和/或栅极接触部处提供钝化;以及功率二极管,其中在阳极和/或阴极接触部处提供钝化。

38.虽然在附图和前面的描述中详细说明和描述了本发明,但是这样的说明和描述被认为是说明性的或示例性的而不是限制性的;本发明不限于所公开的实施例。通过研究附图、公开内容和所附权利要求,本领域技术人员在实践要求保护的发明时可以理解和实现对所公开的实施例的其他变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。