1.本发明涉及一种用于测试集成电路器件的方法。

背景技术:

2.在用于诸如(半导体)存储器单元的集成电路器件的现有技术测试方法中,使用外电阻对器件(的一部分)中的可能缺陷进行建模,从而仅允许对直线型缺陷进行建模。例如,将线性电阻器添加到用于存储器单元的模拟和测试的晶体管级网表。要在高级且新颖的半导体存储器单元中达到十亿分率故障检测级别,这种方式是不够的。

3.kannah sachhidh等人的文章“modelling and diagnosis of faults in multilevel memristor memories(对多级忆阻器存储器中的故障的建模和诊断)”(doi:10.1109/tcad.2015.2394434)提出了一种测试技术,该测试技术利用交叉存储器中固有的潜通路通过集成用于检测和定位忆阻器中的故障的解决方案来同时地测试若干存储器单元。还提出了混合诊断方案,该混合诊断方案使用潜通路和march测试的组合以减少诊断时间。所提出的方案在故障检测和诊断模式期间支持并利用潜通路,而在正常操作期间禁用潜通路。与传统的march测试相比,所提出的混合方案将故障检测和诊断时间分别减少24.69%和28%。

4.robert r martin等人的文章“fault detection and diagnosis for multi-level cell flash memories(用于多级单元闪存存储器的故障检测和诊断)”(doi:10.1109/imtc.2006.235838)提供了一种用于测试和诊断mlc闪存存储器阵列的解决方案。所提出的故障模型考虑到引起存储器的状态改变的许多物理缺陷。通用测试算法和该文章中提出的闪存诊断(fdx)march算法据说是用于mlc闪存的第一种。此外,该文章中提出的故障模型的完整故障覆盖具有低复杂性和低测试时间,从而使它们成为用于测试和诊断多级闪存存储器的故障的

‘

有吸引力的’方法。

技术实现要素:

5.本发明力图提供一种用于测试集成电路器件的测试方法,以允许在十亿分率缺陷(dppb)级别上进行测试。

6.根据本发明,提供了如上所定义的方法,该方法包括:对集成电路器件进行缺陷建模;基于从缺陷建模获得的信息对集成电路器件进行故障建模;基于从故障建模获得的信息进行测试开发;以及对集成电路器件执行测试。对集成电路器件进行缺陷建模包括:执行对集成电路器件的物理缺陷分析,以提供从与集成电路器件相关联的一组无缺陷技术参数修改的一组有效技术参数;以及使用该一组有效技术参数来执行对集成电路器件的电学建模,以基于集成电路器件的无缺陷电学模型来提供缺陷参数化电学模型,其中故障建模包括基于集成电路器件的缺陷参数化电学模型的故障分析,并且其中故障分析包括:定义故障空间,该故障空间包括对多个可能故障的描述;以及确定在对集成电路器件执行测试期间可以使多个可能故障中的哪些敏感化。

7.这允许提供一种扩展到与集成电路器件(例如,(半导体)存储器器件)相关的单元意识测试之外的测试方法,作为器件意识测试(dat)。本发明实施例的缺陷建模并未假设集成电路器件(或其单元)中的缺陷只可以在电学上建模为线性电阻器(如传统方法所建议),而是结合并捕捉物理缺陷对集成电路器件的技术参数以及之后对其电参数的影响。一旦定义了有缺陷电学模型,就执行系统故障分析(基于故障模拟)以导出适当的故障模型并且之后导出测试解决方案。因此,可以提供实现十亿分率故障检测级别的高度可靠的测试方法。

附图说明

8.下文将参考附图更详细地论述本发明,在附图中:

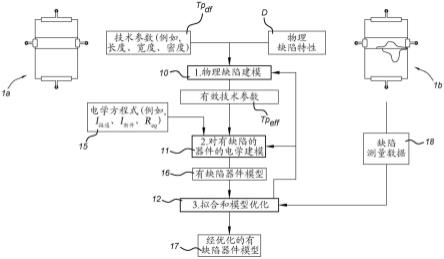

9.图1示出了根据本发明的器件意识测试的实施例的缺陷建模部分的示意表示,

10.图2示出了根据本发明的器件意识测试的实施例的故障建模部分的流程图。

具体实施方式

11.技术扩展推动半导体行业在提供具有高服务质量的更大、更快且更便宜的集成电路方面取得非凡的成功。硅技术已经进入纳米时代并且正在制作5nm晶体管的原型。然而,广泛地认识到,在制造过程期间的缺陷和器件特性的可变性以及它们对系统的整体质量和可靠性的影响是主要挑战,尤其是在考虑高质量级别,例如十亿分率缺陷(dppb)级别时。此外,纳米时代的新兴故障机制使得芯片的故障模式以瞬态、间歇和微弱故障为主,而不是严重和永久故障。故障机制的这种转变可能会影响进行故障建模的方式。应注意,反映新技术的真实缺陷的准确故障模型对于开发高缺陷覆盖测试解决方案是必须的。高质量测试是整个设计和制造链中的负责在出售之前筛选所有有缺陷的芯片的非常关键的步骤,因为这是向最终客户递送要求的质量和可靠性的最后机会。所有这些都表明高质量测试解决方案的必要性和重要性。

12.本发明实施例涉及一种扩展到与集成电路器件1相关的单元意识测试之外的测试方法,在下文表示为器件意识测试(dat)。方法实施例包括三个步骤:缺陷建模、故障建模以及测试(或测试设计(dft))开发。本发明实施例的缺陷建模并未假设集成电路器件1(或其单元)中的缺陷只可以在电学上建模为线性电阻器(如传统方法所建议),而是结合并捕捉物理缺陷对集成电路器件1的技术参数以及之后对其电参数的影响。一旦定义了有缺陷电学模型,就执行系统故障分析(基于故障模拟)以导出适当的故障模型并且之后导出测试解决方案。

13.一般而言,本发明实施例涉及一种用于测试集成电路器件1的方法,该方法包括:对集成电路器件1进行缺陷建模;基于从缺陷建模获得的信息对集成电路器件1进行故障建模;基于从故障建模获得的信息进行测试开发;以及对集成电路器件1执行测试。对集成电路器件1进行缺陷建模包括:执行对集成电路器件1的物理缺陷分析10,以提供从与集成电路器件1相关联的一组无缺陷技术参数tp

df

(例如,长度、宽度、密度或单元结构)修改的一组有效技术参数tp

eff

;以及使用该一组有效技术参数tp

eff

来执行对集成电路器件1的电学建模11,以基于集成电路器件1的无缺陷电学模型(例如,电流、阻抗、电压

……

)来提供缺陷参数化电学模型。

14.代替使用通过将线性电阻器注入表示集成电路器件1的晶体管级网表中导出的故

障模型,本发明实施例首先通过结合缺陷在器件的电学参数(模型)中的影响来改变有缺陷器件1的电学模型(例如,在晶体管级)。在又一实施例中,对集成电路器件1进行缺陷建模包括对集成电路器件1的部分进行缺陷建模,例如,在单元级、单元块级或在晶体管级。然后将电学模型用于执行电路模拟以导出故障模型且之后导出测试解决方案。本发明实施例采用三步dat方法:缺陷建模、故障建模和测试开发。关键区别之一是缺陷建模步骤,该缺陷建模步骤考虑到物理缺陷并且捕捉它们对电学参数的影响,因此实现准确的故障建模。故障建模系统地定义完整(理论)的存储器故障空间,并且之后系统地执行故障分析(使用第一步骤的缺陷建模和电路模拟)以验证该空间。这个步骤提供不仅关于真实故障的性质而且关于对其进行测试的最佳方式的见解信息,该见解信息在dat的第三步骤(测试开发)中使用。作为示例,导致错误读取值的故障可以容易用march测试来检测,因为该march测试能够使故障敏感化,而导致随机读取值的故障需要专门的可测试性设计(dft)以保证其检测。本发明实施例已经应用于r-ram和stt-mram存储器器件,并且展示了该方法与常规存储器测试方法相比的优越性。dat可以对无法通过常规方法来检测的器件缺陷中的一些进行建模并检测这些缺陷。因此,可以进一步减少测试漏掉的量,并且甚至可以更好地诊断缺陷以进行快速良率学习。

15.本发明应用于与任何存储器技术相关联的集成电路器件1,包括新兴的存储器技术,诸如pcm、r-ram和stt-mram。本文中描述了使用两种示例性存储器技术:电阻式随机存取存储器(r-ram)和自旋转移力矩磁性随机存取存储器(stt-mram)。结果表明,对于用传统方法检测不到的缺陷,本发明实施例能够使故障敏感化,这意味着传统方法无法产生十亿分率缺陷(dppb)级别所要求的高质量测试解决方案。至少对于所考虑的两种新兴存储器技术,新方法明确地设置了测试的转折点。

16.传统的存储器测试假设器件缺陷可以被建模为与器件串联或并联的线性电阻器。然而,已经表明,这种方法至少对于新兴存储器技术(诸如r-ram和stt-mram)是不准确的,从而导致不完整或不准确的故障建模。器件意识测试(dat)的本发明实施例旨在解决这个问题,并且设立满足dppb级别要求的步骤。第一,对集成电路器件1缺陷进行物理地建模并且将其电学行为结合到器件模型中。第二,将模型集成到存储器模拟平台中以便分析缺陷对存储器行为的影响;这通过验证预定义故障框架/空间(例如,使用spice模拟)而以系统方式进行。这个步骤的结果提供对真实故障的性质的见解,这用来开发最佳且适当的测试解决方案(例如,march测试、dft)。

17.不准确的缺陷建模可能会导致较差的故障模型,从而不仅在缺陷覆盖方面而且在测试时间方面限制所提出的测试解决方案和dft设计的有效性。例如,以不表示任何真实缺陷的故障模型为目标的测试不会增加缺陷覆盖,而仍消耗测试时间。为了准确地对物理缺陷进行建模,器件模型应结合缺陷影响集成电路器件1的技术参数(例如,长度、宽度、密度)且之后影响电学参数(例如,临界切换电流)的方式。

18.图1示出了这种建模方法的流程图,作为根据本发明的器件意识测试的实施例的缺陷建模部分的示意表示。将集成电路器件1的(无缺陷)模型1a和有缺陷模型1b用作基本输入。最终可能的输出是有缺陷的集成电路器件1的经优化的缺陷参数化模型17。应注意,一般而言,如本文所使用的集成电路器件1可以是finfet晶体管、stt-mram器件、r-ram器件、pcm器件等。

19.用于缺陷建模的本发明方法包括三个步骤。物理缺陷分析和建模10包括:鉴于在集成电路器件1的制造过程期间可能发生的一组物理缺陷d={d1,d2,

……

,dn},必须分析每个缺陷di以充分地理解缺陷机制并且识别其对集成电路器件1的每个(关键)技术参数tp的影响。由于这种缺陷,将修改一个或多个(无缺陷)技术参数tp

df

,从而得到所谓的有效技术参数tp

eff

。这可以通过以下抽象函数来描述:

20.tp

eff

(si)=fi(tp

df

,si)

ꢀꢀ

(1)

21.其中tp

df

是无缺陷技术参数,fi是对应于缺陷di(i=1

……

n)的映射函数,并且si={x1,x2,

……

,x

t

}是表示缺陷di的大小或强度的一组参数。

22.为了获得有效技术参数tp

eff

,物理缺陷分析10包括识别一组可能的物理缺陷d(其可能在集成电路器件的制造期间发生)以及它们的特性。例如对于存储器器件,可能的物理缺陷d包括以下一者或多者:存储器器件的r-ram单元中的成型缺陷、存储器器件的r-ram单元的电极粗糙度、存储器器件的stt-mram单元中的针孔缺陷、存储器器件的stt-mram单元中的缺陷中的隧道结的极端厚度变化等。

23.在有缺陷的集成电路器件1的电学建模步骤11中,识别来自前一步骤10的经更改的技术参数tp

eff

对集成电路器件1的关键电学参数中的每一者的影响(例如,使用如所指示的电学方程式15)。因此,对得到的电学参数进行量化以描述具有缺陷di的有缺陷的集成电路器件1的电学行为。执行这个操作的一种方式是修改无缺陷器件电学模型并通过对每个涉及的技术参数tp的方程式(1)进行积分来将其转换成缺陷参数化电学模型16。这个步骤给出具有有效电学输出参数的原始有缺陷器件模型16。

24.在第三步骤12中,可以进行进一步细化,即,对集成电路器件1进行缺陷建模还包括缺陷参数化电学模型16的校准12。这可以通过基于具有缺陷的集成电路器件1的实际测量对缺陷参数化电学模型16进行拟合和优化来实现,从而得到经优化的缺陷参数化电学模型17,如图1所示。如果有缺陷模型的任何物理或电学参数不准确地匹配特征数据,则有必要保持优化器件模型,直到获得可接受的准确性。通过执行硅数据拟合和模型优化,可以得出经优化的缺陷参数化电学模型17,这实现用于故障建模的准确电路模拟。

25.第二dat步骤是故障建模。在这个步骤中,使用来自前一步骤的(经优化的)缺陷模型16、17以分析集成电路器件1在存在缺陷的情况下的行为。这个分析的结果用来开发高质量测试。因此,在又一本发明实施例中,故障建模20包括基于集成电路器件1的缺陷参数化电学模型16;17的故障分析22。

26.在示例性实施例中,定义故障空间,所述故障空间对目标集成电路器件(例如,stt-mram、r-ram、pcm等)的所有可能故障进行描述和分类。第二,下面(参考图2更详细地)描述故障分析方法,所述故障分析方法确定来自空间的哪些故障对于所考虑的缺陷是现实的,即,在存在这种缺陷的情况下,可以使哪些故障敏感化。为此,提供了一个实施例,其中故障分析22包括:定义故障空间,所述故障空间包括对多个可能故障23、24的描述;以及确定在对集成电路器件1执行测试期间可以使多个可能故障23、24中的哪些敏感化。

27.在又一示例性实施例中,故障分析22包括确定可能故障23、27的列表,可能故障的列表包括容易检测的故障(例如,强烈故障)23和/或难以检测的故障27(例如,微弱的故障、导致随机读取的故障等)。容易检测的故障23是可以通过对集成电路器件1应用操作序列来检测到的功能故障。难以检测的故障27是引起集成电路器件1中的参数故障的故障(例如,

位线电流减少或者引起随机或不可预测的读取的故障)。

28.在有利的实施例中,集成电路器件1是存储器器件1。在又一有利的实施例中,集成电路器件是逻辑器件1。在这方面,可以设想存储器器件1的许多实施例和示例。

29.在一个示例中,分析被限于静态和动态单个单元故障。静态故障被定义为可以通过执行至多一个操作来敏感化的故障,而动态故障要通过多于一个操作来敏感化。如果故障涉及多于一个单元,则故障被称为耦合故障。强烈故障可以使用故障原语(fp)符号来系统地描述。fp描述观察到存储器器件1行为的与预期的存储器器件行为之间的差异,表示为三元组(s/f/r),其中

30.s表示使故障敏感化的操作序列。序列采用s=x0o1x

……on

xn的形式,其中x是

‘0’

或

‘1’

,并且o是具有值r(读取)或w(写入)的操作,0和1表示逻辑单元值。如果n≤1,则故障是静态的,否则是动态的。

31.f描述在执行s之后存储在单元中的值。对于传统的基于电荷的存储器(例如,sram),仅存在两个数字状态,即,f是

‘0’

或

‘1’

。然而,比如r-ram和stt-mram的新兴存储器技术使用电阻式存储元件;预定义电阻范围确定存储器器件1中的单元的逻辑状态。由于缺陷或极端过程变化,此类存储器器件1的状态可以在这些范围之外,因此需要定义其他(有故障的)电阻状态l、u和h。大量60nm mtj stt-mram存储器器件1的测量到的电阻分布表明f是{0;1;u;l;h}中的一者。分布中的每个点表示存储器器件1,所述存储器器件的r

p

在x轴上示出并且r

ap

在y轴上示出(并联p状态下的电阻r

p

,反并联ap状态下的电阻r

ap

)。从设计的角度来看,标称r

p

是例如2kω并且标称r

ap

是5kω,这在隧穿磁阻率tmr=150%下确保良好的读取可靠性。可以使用3σ的标称值来定义两个状态0和1的电阻范围。在规范内的器件1旁边,还存在因一些缺陷或极端过程变化而在规范外的大量器件1。这些是:(1)极低电阻状态

‘

l’,2)极高电阻状态

‘

h’,以及3)未定义的状态

‘

u’。应注意,stt-mram的状态

‘0’

和

‘1’

的定义与r-ram不同,其中状态

‘0’

代表高电阻而

‘1’

代表低电阻。

32.r描述读取操作的输出(如果s是读取操作的话)并且具有值

‘0’

、

‘1’

、

‘

?’或

‘‑’

,其中

‘

?’表示随机读取值(例如,感测电流非常接近感测放大器参考电流),并且

‘‑’

表示r不适用,即,当s是写入操作时。

33.表i单个单元静态故障原语

[0034][0035]

表i列出了所有单个单元静态fp及其名称。fp的命名遵循以下方案:

[0036]

fp={读取影响}{行为}{初始值}

{f}

ꢀꢀꢀ

(2)

[0037]

在这里,只有在读取敏感化操作导致故障读取:不正确(i)或随机(r)读取值的情况下,{读取影响}才适用。{行为}描述故障单元的行为:它指明操作(读取(r)或写入(w))的性质和产生的故障后果(破坏性(d)、转变(t)或无)。例如,

‘

wdf’意指写入破坏性故障。{初始值}描述单元的初始状态并且f是在执行s之后存储在单元中的值。

[0038]

例如,rrdf01=(0r0/1/?)是在读取

‘0’

期间使单元进入

‘1’

并且在输出处返回随机读取值的随机写入破坏性故障。状态故障是这个方案的例外,因为没有执行敏感化操作。它们的名称遵循以下方案:

[0039]

fp=sf{初始值}

{f}

[0040]

对于动态故障,fp的名称得到前缀nd,其中n表示s中的操作数量并且f是基于s中的最后操作,例如(1r1w0/l/-)是2d-wtf1

l

。

[0041]

集成电路故障可以分类成两种类型:强烈故障和微弱故障。强烈故障是可以始终通过应用操作序列来敏感化(并且可以被检测到)并且可以引起功能错误的功能故障;例如,表i的所有fp都是强烈故障。相反,微弱故障不导致fp,但它们会引起参数故障,例如,在读取操作期间位线电流减少。应注意,这些故障无法用任何操作序列来检测,因为它们不引起任何功能错误。显然,这些故障也需要被检测到,因为它们引起可靠性问题(例如,寿命更短、内场故障率更高)。取决于检测故障所需的努力,故障可以进一步分成容易检测的故障23和难以检测的故障27。可以简单地通过应用写入和读取操作(例如,通过使用march测试)来保证对容易检测的故障23的检测。然而,无法仅通过march测试来保证对难以检测的故障27的检测,并且它们的检测需要附加的努力;例如,使用专用电路,诸如dft。应注意,强烈故障可以包括容易检测的故障23和难以检测的故障27,而微弱故障全都是难以检测的故障

27。强烈难以检测的故障27的示例是随机读取故障,诸如rrf11和rrf00。例如,在具有小缺陷的stt-mram中,读取期间的位线电流可以非常接近感测放大器的参考电流,从而引起器件之间的随机行为。

[0042]

一旦对缺陷建模并且定义了故障的框架,就可以使用系统电路模拟方法来执行故障的验证。在本描述中,这限于涉及单个单元故障分析的示例。这种故障分析的示例在图2的图中示出。故障分析20可以包括七个步骤:1)电路生成,2)缺陷注入,3)激励生成,4)电路模拟,5)故障分析,6)故障原语识别,以及7)缺陷大小扫掠,并且重复步骤2至6,直到覆盖了所有大小。应注意,在所描述的示例性情况下,缺陷注入意味着将集成电路器件1(例如,r-ram或stt-mram)的电学模型16;17改变为在dat方法实施例的步骤1中获得的有缺陷器件模型16;17,而缺陷大小扫掠意味着改变缺陷的大小,这也修改有缺陷器件模型16;17的电学参数。

[0043]

图2示出了表示使得能够对真实故障的性质和测试它们的方式有更多见解的故障分析方法的流程图。鉴于缺陷列表21及其大小范围,应首先执行故障分析的七个步骤以验证表i的静态单个单元fp(即,n≤1)。结果将是与缺陷/参数的大小/范围相关联的一组fp,其被分类为容易检测的故障23、剩余故障24和难以检测的故障27。如果在存在缺陷的情况下fp未被敏感化,则故障被认为是微弱的并且添加到剩余故障24的列表。接下来,将进一步分析导致剩余故障24的所有缺陷,但然后使用动态故障分析,以n=2开始。导致剩余故障24的一些缺陷现在可以触发容易检测的故障23。例如,s=0w0引起微弱故障,而s=0w0w0引起容易检测的强烈故障23。一旦完成n=2操作单个单元故障分析22,就可以针对导致剩余故障24的缺陷以n=3进行类似的分析(经由判定框25)。可以通过扩展s来重复该过程,每次一个操作,直到达到所考虑的n

最大

(结束故障分析框26)。该过程中的每个步骤旨在减小剩余故障集24并且增大容易检测的故障集23。在故障分析结束时剩余的是难以检测的故障27的(精简)集。这是不仅有利于优化测试成本而且有利于提高整体产品质量的有利步骤。最终结果将是可以容易通过生成march测试来检测到的一组故障23,以及需要特别关注以便保证其检测(例如,dft、特殊测试等)的另一组故障27。

[0044]

故障分析20的结果促成高质量且高效的测试解决方案的开发。可以通过应用适当的测试算法来检测所有容易检测的故障23。通过识别故障23中的每一者的最低检测条件并且之后将它们汇编在测试算法中来开始开发优化的算法。这将以最低测试成本提供对容易检测的故障23的故障覆盖。还可以结合dft方案以便进一步优化测试时间,例如,实现同时测试许多故障23的dft、并行测试等。然而,难以检测的故障27需要特别关注。可能需要专门的dft方案和测试。示例是可以直接测量位线扫掠、修改操作条件(诸如微弱写入操作)的dft方案、应力测试等。目的是在保持经济上可负担测试成本的同时最大化对这些故障27的故障覆盖。一般而言,因此,本发明还涉及一个实施例,其中测试开发包括提供测试方案,所述测试方案包括针对在故障分析22中识别的每个容易检测的故障23对集成电路器件1进行的一组操作,以及针对每个难以检测的故障27对集成电路器件1的可测试性修改(可能与一组操作相结合)的设计。

[0045]

为了进一步改进对缺陷的验证,图3示出了表示故障分析22的又一方法的流程图,所述方法使得能够使用示例性系统方法来验证真实故障。故障分析22包括多个(操作)步骤:i)电路(网表)生成22a,ii)缺陷注入22b,iii)激励生成22c,iv)缺陷大小扫掠22d),v)

电路模拟22e,vi)分析22f,vii)故障原语识别22g,viii)故障原语报告22h,ix)缺陷扫掠完成22i,x)激励完成22j以及xi)缺陷完成22k。

[0046]

为了详述图3所示的流程图,故障分析22方法以电路(网表)生成22a开始,其提供了对电路的描述以用于后面的模拟目的。此后,鉴于缺陷列表21(如图2所示),进行缺陷注入22b,接着是激励生成22c。接下来,发生对(注入的)缺陷的缺陷大小扫掠22d,由此修改缺陷的大小,例如,对于电阻缺陷,改变电阻的幅值。此后,执行电路模拟22e,由此在(故障)分析22f步骤中检查电路模拟22e的结果。一旦完成了分析22f,就执行故障原语识别22g以识别观察到的电路行为与预期电路行为之间的任何差异。如果识别出故障原语,那么在故障原语报告22h步骤中进行报告,并且在没有识别故障原语的情况下,跳过故障原语报告22h步骤。

[0047]

其后,如果需要对缺陷大小的进一步扫掠,那么重复步骤iv)至viii),即,缺陷大小扫掠22d到故障原语报告22h。否则,如果不需要对缺陷大小的进一步扫掠,那么这在缺陷扫掠完成22i步骤中标记为完成。类似地,在接下来的步骤中,如果考虑其他激励,则重复步骤iii)至ix),即,激励生成22c至缺陷扫掠完成22i,否则,这在激励完成22j步骤中标记为完成。作为最终步骤,如果要注入其他缺陷,那么重复步骤ii)至x),即,缺陷注入22b至激励完成22j。否则,如果注入并检查了所有要求的缺陷,则这在缺陷完成22k步骤中标记,并且完成故障分析22。如上所述,用于故障分析22的方法提供了用于验证缺陷的系统方法,从而允许用于检查缺陷是否真实的准确且系统的框架。因此,通过执行准确的故障分析20,这允许导出适当且真实的故障模式,并且因此导出测试解决方案。

[0048]

在以下描述部分中,通过遵循三个主要步骤来将本发明dat方法实施例应用于r-ram存储器器件1。然而,为了阐明和理解,讨论r-ram制造缺陷并且选择代表性缺陷。r-ram存储器器件1的制造过程流程以在前段制程(feol)生产阶段中在晶片上制造晶体管。然后,后段制程(beol)阶段中沉积下金属互连层。通常在两个金属层之间构建r-ram存储器器件1。在这之后,沉积剩余的金属层。存储器器件1还没有导电细丝(cf),因此,需要执行初始cf形成步骤以便实现功能性存储器器件1。

[0049]

作为本发明实施例的示例性实施方式,将源于cf形成步骤的缺陷用作示例。在形成步骤期间,在r-ram器件1氧化物中产生最初的cf。这个步骤的条件对器件1的性能影响很大,并且因此,这个步骤可能导致缺陷。可以进行对形成条件的一些观察:形成电流(i

形成

)越高导致器件电阻越低且变化越少,并且形成电流的变化导致更多电阻变化。器件1几何形状和氧化物缺陷密度的变化也影响形成步骤。两个缺陷可以源于形成步骤:过度形成,此时cf太大;以及不良形成,此时没有形成cf或仅形成极小的cf。

[0050]

在以下段落中,将本发明dat方法用于形成缺陷(作为案例研究),并且与使用线性电阻器对缺陷进行建模的常规方法进行比较。对于dat方法,r-ram器件1模型的输入参数与形成电流i

形成

相关,因此将形成步骤的可能导致过度形成或不良形成的物理特性结合到电学模型16中。模型16可以被包括在网表中以观察其电学效果。形成电流i

形成

与cf的形状直接相关,即,它影响r-ram存储器器件1的关键参数:t

ox

(顶部电极te与底部电极be之间的氧化物层的厚度)、l

cf

(cf的长度)、l

间隙

(cf与顶部电极te之间的长度)、φb(在底部电极附近的cf的宽度),以及φ

t

(最靠近顶部电极的cf部分的宽度)。已表明,l

cf

和φ

t

对r-ram存储器器件1的电阻的影响最大。因此,使用这些参数对存储器器件1的形成效果进行建模。

[0051]

为了包括l

cf

的随机变化,包括附加参数δl

cf

(其设定这个变化的强度)。使用这些参数对器件1的形成效果进行建模。物理缺陷建模步骤可以在数学上表示如下:

[0052]

l

cf,eff

(i

形成

)=a

1 exp(b1·rμ

(i

形成

)) c

1 exp(d1·rμ

(i

形成

))

ꢀꢀ

(3)

[0053]

φ

t,eff

(i

形成

)=a

2 exp(b2·rμ

(i

形成

)) c

2 exp(d2·rμ

(i

形成

))

ꢀꢀ

(4)

[0054]

δl

cf,eff

(i

形成

)=a

3 exp(b3·rμ

(i

形成

)) c

3 exp(d3·rσ

(r

μ

))

ꢀꢀ

(5)

[0055]

在这里,ak、bk、ck和dk(k=1,2,3)是拟合参数。r

μ

(i

形成

)=f(i

形成

),其中f(i

形成

)是i

形成

到中值电阻的三次hermite插值,如a.grossi等人在iedm,2016年中的文章“fundamental variability limits of filament-based r-ram(基于细丝的r-ram的基本可变形限制)”所描述,该文章以应用方式并入本文。r

σ

(r

μ

)由本文章中的方程式(1)给出。

[0056]

h.li等人在电子器件快报,第35卷第2期,2014年2月的文章“a spice model of resistive random access memory for large-scale memory array simulation(用于大规模存储器阵列模拟的电阻式随机存取存储器的spice模型)”中公开的r-ram器件模型将l

cf

、φ

t

和δl

cf

作为输入参数,该文章以引用方式并入本文。这三个参数规定r-ram器件1的切换行为和电阻,并且因此很适合于对形成对器件的电学行为的影响进行建模。当在网表中模拟得到的模型时,可以分析对电学参数(例如,电阻、切换速度和阈值)的效果。

[0057]

在拟合和模型优化步骤中,对三个可改变的参数进行校准,使得r-ram器件1的有缺陷行为与真实器件的测量相对应。为了实现这一点,首先分析l

cf

、φ

t

对平均电阻的影响。然后将这些参数拟合到grossi文章中的测量,并且因此链接到i

形成

。分析δl

cf

的效果并且以类似方式拟合。i

形成

在5μa与34:1μa之间改变。

[0058]

应注意,常规的电阻缺陷建模方法将形成缺陷建模为与无缺陷r-ram器件1并联(r

pd

)或串联(r

sd

)的电阻器。

[0059]

一般而言,提供了又一个实施例,其中存储器器件1是电阻式随机存取存储器(r-ram)单元,技术参数tp包括氧化物厚度t

ox

、导电细丝长度l

cf

、间隙长度l

间隙

、导电细丝顶部宽度φ

t

、导电细丝底部宽度φb中的一者或多者,并且电学参数包括重置阈值v

重置

、设定阈值v

设定

、重置电阻r

hrs

、设定电阻r

lrs

、高电阻状态到低电阻状态切换延迟th→

l

、低电阻状态到高电阻状态切换延迟t

l

→h。

[0060]

下一本发明实施例步骤(即,故障建模)包括基于将在缺陷建模步骤中生成的电学模型用于形成缺陷来进行的故障分析。针对两个缺陷模型进行静态故障分析,并且然后分析用于dat方法(和传统方法)的动态故障。由于形成缺陷会影响单个r-ram器件1单元,因此仅分析单个单元故障。可能的单个单元静态故障是在表i中列出的那些故障;可以通过遵循如上所述的定义来构建动态故障空间。

[0061]

用于形成缺陷的故障分析以分析静态故障开始。表ii列出了针对所有的i

形成

、r

pd

和r

sd

用dat方法以及常规(conv.)方法两者敏感化的静态故障。

[0062]

表ii使用器件意识和电阻缺陷模型的故障敏感化

[0063][0064]

通过两种方法敏感化的独特故障(分别是6和9)及其重叠的故障(2)清楚地表明方法之间的差异。在基于常规缺陷模型使用的案例测试中,独特dat故障(8个真实故障中的6个,这对应于75%)可以导致测试遗漏。除此以外,常规的缺陷模型方法触发不是真实的9个故障,因此导致浪费测试时间。应注意,在这两种方法之间仅观察到2个共同的故障。故障分析然后以两个案例研究继续,其中增加s的长度,即,将动态故障敏感化。

[0065]

表iii用于r-ram形成缺陷故障的故障类别和fp

[0066][0067]

表iii示出了在敏感化操作的同一排上针对变化的i

形成

观察到的强烈故障的故障类别和fp。选择序列以表明随着增加s的长度,更多的强烈故障被敏感化。敏感化序列越长,故障就变得越强烈。应注意,故障仍然是难以检测的故障27(表iii中的黑体字名称)。这可以通过以下事实来说明:较低的i

形成

导致增加的r-ram器件1电阻(r

lrs

和r

hrs

两者)或甚至不良形成的缺陷。由于这种增加,单元无法在有效的

‘1’

区中切换,反而切换到

‘

u’区,而切换到

‘0’

区中的单元以

‘

h’区结束,如fp所示。应注意,尽管故障是强烈而难以检测的,但它们仍可以比微弱故障更容易被捕获。表iii进一步表明故障类型的范围被中断。这是由细丝生长和断裂的随机行为引起的,有时会使单元处于不可预测的状态。

[0068]

表iv用于r-ram串联电阻故障的故障类别和fp

[0069]

[0070]

在表iv中针对r

sd

示出了该方法对传统电阻缺陷的应用。同样,用黑体字标记强烈的难以检测的故障,而容易检测的故障是常规字体。表iv还表明当s的长度增加时,故障覆盖增加。例如,对于r=5,01kω的缺陷大小,可以观察到强烈的难以检测的故障(对于序列s=1r1w0)以及强烈的容易检测的故障(对于序列s=1r1w1w0)。第一序列导致2d-wtf1u强烈的难以检测的故障,而第二序列增强故障行为并且引起强烈的容易检测的3d-wtf11故障。

[0071]

为了比较,表iv还示出了在表iii中示出的相同序列。在这里可以看到差异在于,电阻缺陷模型随着增加的电阻无法切换到

‘0’

状态,而器件意识缺陷模型表明器件仍在状态之间切换。这个差异是由以下事实引起的:串联电阻器减少r-ram器件1上的电压,并且因此从未达到切换阈值。从上面可以得出,本发明dat方法和常规方法导致不同故障的敏感化。器件意识模型始终能够表明单元的切换,而电阻缺陷模型仅在有限的缺陷范围内表现出切换行为,因此未正确地对该缺陷进行建模。使用不适当的缺陷模型将导致检测非现有故障且错过现有故障的低质量测试。此外,可以得出,分析方法能够通过扩展s的长度来增加故障覆盖。这样扩展可能使缺陷将故障行为从微弱的难以检测的故障转变为强烈的难以检测的故障,并且将强烈的难以检测的故障转变为强烈的容易检测的故障,因此增加检测概率。

[0072]

来自前一步骤的结果用于开发r-ram测试步骤。在故障建模步骤中,观察到由这些缺陷引起的故障与r-ram存储器器件1处于错误状态(即,

‘

u’、

‘

l’或

‘

h’)相关,从而引起难以检测的故障24。因此,需要集中于检测单元是否处于这些状态之一的dft方案。在s.hamdioui等人在计算机汇刊,第64卷第1期,2015年1月的文章“testing open defects in memristor-based memories(测试基于忆阻器的存储器中的明显缺陷)”中,描述了可以用于检测单元的电阻是否处于

‘

u’状态的短写入时间和低写入电压dft方案,该文章以引用方式并入本文。应注意,对这个方案的修改也将允许检测到处于

‘

l’和

‘

h’状态的单元。相反,r

sd

缺陷模型使许多不真实的强烈的容易检测的故障敏感化,例如,irf11和wtf11。尽管它们可以容易被march测试中的(w1;r1)元素检测到,但对于它们的测试仍将增加不必要的测试成本。

[0073]

在以下段落中,针对基于stt-mram技术的存储器器件1,使用本发明dat方法并且将其与常规方法进行比较。描述了stt-mram制造缺陷的示例,其中特别强调了针孔缺陷,这然后作为本发明实施例的应用的主题。

[0074]

stt-mram制造过程主要包括表混cmos制造步骤以及将磁性隧道结(mtj)器件集成到金属层中。stt-mram单元的自底向上的制造流程和竖直多层结构对于本领域技术人员是已知的,参见例如y.j.song等人在iedm,2016年中的文章“highly functional and reliable 8mb stt-mram embedded in 28nm logic(嵌入在28nm逻辑中的高度功能性且可靠的8mb stt-mram)”,该文章以引用方式并入本文。基于制造阶段,stt-mram缺陷可以分类成前段制程(feol)缺陷和后段制程(beol)缺陷。由于mtj在beol处理期间集成到金属层中,因此beol缺点可以进一步分类成mtj制造缺陷和金属化缺陷。

[0075]

表v stt-mram缺陷分类

[0076][0077]

表v列出了stt-mram存储器器件1的一些潜在缺陷。在这些缺陷中,mgo隧道结中的针孔缺陷被视作在stt-mram存储器器件中可能出现的最重要缺陷之一。针孔缺陷因未优化的沉积过程而形成。这可能因硼扩散到mgo结或其他金属杂质中而引起在mgo隧道结中形成金属短路。因此,这导致电阻面积乘积(ra)和隧穿磁阻率(tmr)参数两者的退化。此外,由于焦耳加热以及针孔圆周上的电场,小针孔的面积可能增长。因此,如果甚至在制造测试中无法检测到小针孔缺陷,则它们可能引起电场的及早击穿。

[0078]

对于常规基于电阻器的缺陷建模方法,将针孔缺陷建模为串联电阻器r

sd

或并联电阻器r

pd

,这类似于如上所述的对r-ram存储器器件1中的形成缺陷进行建模的情况。

[0079]

通过对各种mtj器件中的针孔缺陷的综合理论研究和实验表征,显然,ra和tmr是受针孔缺陷显著影响的两个关键技术参数。因此,作为dat方法实施方式的第一部分,将针孔对这两个技术参数的效果建模如下。

[0080][0081][0082]

其中a

ph

(范围在0和1之间)是相对于mtj器件的截面面积a的标准化针孔面积。ra

df

和tmr

df

分别是无缺陷mtj的ra和tmr参数(即,当a

ph

=0时)。ra

bd

是在击穿之后得到的ra。

[0083]

作为实施例方法中的下一步骤,将方程式(6)和(7)集成到已经通过良好器件的测量数据进行校准的无缺陷mtj紧凑模型中。以此方式,将无缺陷mtj模型转换成能够预测针孔缺陷对mtj器件的电学影响的有缺陷mtj模型。此外,可通过改变输入变元a

ph

来调谐针孔大小。

[0084]

然后通过对良好的mtj器件和具有怀疑的针孔缺陷的器件两者执行电学表征来应用拟合和模型优化。通过拟合到测量的硅数据,然后可以进一步优化针孔参数化mtj紧凑模型。通过强调具有怀疑的针孔缺陷的器件和曲线拟合方法,得到值ra

bd

=0.41ω

·

μm2。

[0085]

一般而言,提供了又一个实施例,其中存储器器件1是自旋转移力矩磁性随机存取存储器(stt-mram)单元,技术参数tp包括电阻面积乘积ra、隧穿磁阻率tmr、自由层的各向

异性磁场hk、自由层的饱和磁化ms、隧道结的势垒高度φ中的一者或多者,并且电学参数包括p状态下的电阻r

p

、ap状态下的电阻r

ap

、临界切换电流ic、平均切换时间tw。

[0086]

作为下一步骤,通过用dat方法方式执行故障分析来将本实施例故障建模方法应用于针孔缺陷。

[0087]

表vi stt-mram存储器器件的单个单元静态故障建模结果

[0088][0089]

表vi表明足够大的针孔(a

ph

》0.62%)使mtj器件落入

‘0’

状态或甚至

‘

l’状态的电阻范围中。对应的故障原语fp在表vi中列出。随着针孔变小(a

ph

在0.08%与0.61%之间),将r

p

变换到

‘

l’状态并且r

ap

将变换到

‘

u’状态。取决于ap状态下的精确mtj电阻,读出值可以处于三种情况:1)

‘0’

,2)随机(

‘

?’),以及3)

‘1’

。在r

ap

显著小于参考单元的电阻(即,a

ph

在0.36%与0.61%之间)的情况1)下,ap状态下的器件的读出值是

‘0’

。在r

ap

接近参考单元的电阻(即,a

ph

在0.33%与0.35%之间)的情况2)下,读出值可以是随机的。换句话说,读取操作是不稳定的,并且因此

‘0’

和

‘1’

两者都是可能的读出值。在r

ap

比参考单元的电阻大得多(即,a

ph

在0.08%与0.32%之间)的情况3)下,读出是

‘1’

。随着针孔面积在0.05%到0.07%之间变得更小,预期的

‘1’

状态变换到

‘

u’状态,而预期的

‘0’

状态保持正确。如果针孔大小小于0.04%,则器件表现正常,从而不导致决定性故障。

[0090]

相反,基于将r

sd

和r

pd

注入无缺陷网表(即,现有技术方法)来执行故障建模,模拟结果也在表vi中示出。将基于两种缺陷建模方法的故障建模结果进行比较表明存储器器件1的故障行为因为针孔缺陷而无法用常规的基于电阻器的缺陷建模方法捕捉到。从表vi中清楚的是,在常规方法的模拟结果中未观察到通过本发明实施例针孔缺陷模型敏感化的fp。这是因为mtj器件1被认为是常规方法的黑盒。因此,在模拟中仅看到

‘0’

和

‘1’

状态。然而,使用本发明实施例的模拟和测量数据清楚地表明针孔缺陷可以导致器件进入状态

‘

u’和

‘

l’。这意味着依赖于故障建模和测试开发的传统方法可能会导致低质量测试解决方案,

从而意味着更高数量的遗漏。常规方法导致无法应用于stt-mram(即,基于针孔缺陷的校准模型,用我们的方法未找到)的一些故障原语。例如,使用串联电阻器r

sd

导致irf00,而使用并联电阻器r

pd

导致wtf00。这可能会导致以非现有故障为目标的测试,从而意味着浪费测试时间。

[0091]

基于用经校准的针孔缺陷模型的模拟结果,显然,针孔越大,故障效果越大,并且因此越容易检测到。如表vi所示,具有特定范围的缺陷大小的针孔缺陷可以引起多个故障。然而,能够检测到这些故障之一的任何测试都可以保证对这个特定针孔缺陷的检测。例如,当针孔面积a

ph

大于0.79%时,存在八个敏感化故障原语fp。在这些fp中,sf1

l

(在表中用粗体字标记)可以简单地通过读取

‘1’

操作来检测到,因为这些是强烈的容易检测的故障。因此,对于a

ph

》0.79%的针孔,(r1)是march算法中的检测条件。不同针孔大小的检测条件在表vi的最后一列中列出。将表vi中的最后三行相结合,显然,包括元素(w1,r1)的任何march测试都可以保证将a

ph

》0.36%的针孔缺陷检测为容易检测的故障。然而,对于更小的针孔缺陷,march测试无法保证它们的检测,因为缺陷引起难以检测的故障。由于累积的焦耳加热,小针孔缺陷的面积随时间而增加,因此如果在制造测试期间未检测到,则它们可能会引起场的及早击穿。这需要专用于极小针孔缺陷的dft设计或应力测试。一个可能的解决方案是使stt-mram存储器器件1经受具有升高的电压或延长的脉冲宽度的锤击写入

‘1’

操作序列,以故意加速针孔缺陷的增长,从而引起容易检测的故障。然而,这种方法对于大量测试来说过分昂贵。另外,需要仔细调谐锤击写入脉冲的幅值和持续时间以避免对良好存储器器件1的任何无意破坏,而同时维持可接受的测试有效性和效率。

[0092]

根据本发明,以上描述了器件意识测试方法的示例性实施例,所述器件意识测试方法具有三个不同且随后的步骤:缺陷建模、故障建模和测试开发。与常规基于电阻的测试相反,dat实施例导致准确的故障模型并且由此实现高质量(接近dppb级别)测试。

[0093]

如以上针对r-ram和stt-mram存储器器件1所述,本文描述的dat实施例导致反映物理缺陷的更准确故障模型。许多敏感化的故障都是独特的并且无法通过常规的基于电阻器的缺陷建模方法来观察到。因此,本方法明确地减少测试遗漏的数量并且增加测试质量。

[0094]

准确地对缺陷建模并且为其创建故障字典可以显著地加速良率学习过程。由于可以使用器件意识测试对每个缺陷单独地建模,而不是将电阻缺陷模型用于所有缺陷,因此可以为每个缺陷创建独特的故障特征。这改进了良率学习曲线,因为可以基于故障特征更准确地诊断缺陷。

[0095]

现今,公司花费大量的时间在功能测试(或系统测试)上以补偿因传统故障建模和测试的限制而造成的故障覆盖。本发明dat实施例允许开发可以在制造阶段应用的适当且高效的结构测试;因此,显著减少花费在板级测试上的昂贵测试时间。

[0096]

最后,dat实施例不限于新兴的存储器器件技术,方法也可以应用于其他电路(例如,sram和逻辑)以及其他种类的器件(诸如finfet和pcm器件)的测试生成。

[0097]

上文已参考附图所示的多个示例性实施例描述了本发明。对一些部分或元件的修改和替代实现是可能的,并且被包括在如所附权利要求限定的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。