1.本发明涉及半导体制造技术领域,尤其涉及一种半导体器件及其制造方法。

背景技术:

2.电容器(capacitor)是一种可以存储电量和电能的元件。可以通过在电容器的两个电极上施加不同的电压,使得电容器内储存不同数量的电荷。在此基础上,可以通过电容器来实现对不同数据的存储。由此可见,电容器的品质直接影响半导体器件的数据存储性能。

3.现有技术中电容器的制造方法如图1a~图1e所示,参考图1a,首先在基底1上沉积刻蚀阻挡层2及牺牲膜层3;之后,参考图1b,刻蚀牺牲膜层3及刻蚀阻挡层2形成电容孔4;之后,参考图1c,在牺牲膜层3、电容孔4内壁及底壁上沉积下电极材料层5;之后,参考图1d,去除电容孔4外的下电极材料层5,形成下电极6;之后,参考图1e,去除牺牲膜层 3;后续在下电极6上沉积介质层及上电极,形成电容器。

4.为了提升存储器的驱动性能,需要增加电容器的电容。一般增加电容器电容的方式是增加电容器的高度。然而电容器的高度增高,会导致电容器的纵横比(aspect ratio)增加。电容器的纵横比增加,就容易在wet clean(湿法清洗)工艺进行时,出现电容器倾斜、弯曲甚至塌陷等问题。

技术实现要素:

5.本发明提供了一种半导体器件及其制造方法,用以提高对下电极的支撑效果,防止下电极倾斜、弯曲或塌陷,同时简化工艺。

6.第一方面,本发明提供了一种半导体器件,该半导体器件包括一基底、形成在基底中的着陆焊盘图案、形成在基底上的下电极图案、以及形成在下电极图案之间的支撑结构。其中,着陆焊盘图案包括多个呈阵列排列的着陆焊盘。下电极图案包括多个呈阵列排列的下电极,多个下电极与多个着陆焊盘一一对应;每个下电极为筒状结构,且每个下电极的底部与对应的着陆焊盘接触。支撑结构包括连接在纵向或横向任意相邻的两个下电极之间的支撑线。

7.在上述的方案中,通过设置连接在纵向或横向任意相邻的两个下电极之间的支撑线,形成栅格状的支撑结构,以提高对下电极的支撑效果,防止下电极倾斜、弯曲或塌陷。

8.在一个具体的实施方式中,支撑结构设置在下电极图案的顶部位置,使支撑结构能够在下电极的图案顶部进行支撑,进一步提高支撑效果。

9.在一个具体的实施方式中,支撑结构的材料为sin、sibn或sicn。

10.在一个具体的实施方式中,下电极的材料为氮化钛或多晶硅。

11.在一个具体的实施方式中,支撑线的厚度均在10nm~500nm之间,以提高支撑效果。

12.第二方面,本发明还提供了一种半导体器件的制造方法,该制造方法包括:

13.提供一基底,基底中形成有着陆焊盘图案,着陆焊盘包括多个呈阵列排列的着陆焊盘;

14.在基底上形成下电极图案,下电极图案包括多个呈阵列排列的下电极,多个下电极与多个着陆焊盘一一对应;每个下电极为筒状结构,且每个下电极的底部与对应的着陆焊盘接触;

15.在下电极图案中形成支撑结构,支撑结构包括连接在纵向或横向任意相邻的两个下电极之间的支撑线。

16.在上述的方案中,通过设置连接在纵向或横向任意相邻的两个下电极之间的支撑线,形成栅格状的支撑结构,以提高对下电极的支撑效果,防止下电极倾斜、弯曲或塌陷。

17.在一个具体的实施方式中,在基底上形成下电极图案包括:在基底的上方,形成覆盖基底的牺牲膜层;从上向下刻蚀牺牲膜层,形成电容孔图案,其中,电容孔图案包括多个呈阵列排列的电容孔,多个电容孔与多个着陆焊盘一一对应,每个电容孔与对应的着陆焊盘连通;在电容孔图案中的每个电容孔的孔壁及底部形成每个下电极,以形成下电极图案。

18.在一个具体的实施方式中,在牺牲膜层上刻蚀形成电容孔图案之前,该制造方法还包括:在牺牲膜层的上方,形成覆盖牺牲膜层的支撑层。刻蚀牺牲膜层,形成电容孔图案包括:从上向下刻蚀支撑层及牺牲膜层,形成电容孔图案。

19.在一个具体的实施方式中,在下电极图案之间形成支撑结构具体为:采用毯式等离子体刻蚀工艺刻蚀所述支撑层,形成所述支撑结构。无需采用光刻工艺形成支撑结构,简化支撑结构的形成方式,简化工艺。

20.在一个具体的实施方式中,采用毯式等离子体刻蚀工艺刻蚀支撑层,形成支撑结构包括:采用毯式等离子体刻蚀支撑层时,支撑层中位于下电极的较窄的位置,刻蚀速率越慢;支撑层中位于下电极的较宽的位置,刻蚀速率越快。以便于形成栅格状的支撑结构,同时实现将位于支撑层下方的牺牲膜层去除。

附图说明

21.图1a为现有技术中制造电容器的其中一步工序的示意图;

22.图1b为现有技术中制造电容器的其中另一步工序的示意图;

23.图1c为现有技术中制造电容器的其中另一步工序的示意图;

24.图1d为现有技术中制造电容器的其中另一步工序的示意图;

25.图1e为现有技术中制造电容器的其中另一步工序的示意图;

26.图2a为本发明实施例提供的一种半导体器件俯视的结构示意图;

27.图2b为图2a中示出的半导体器件的a-a面的剖视的结构示意图;

28.图3a为本发明实施例提供的一种半导体器件的制造方法中的一步工序的示意图;

29.图3b为图3a中示出的半导体器件的俯视的结构示意图;

30.图4为本发明实施例提供的一种半导体器件的制造方法中的另一步工序的示意图;

31.图5为本发明实施例提供的一种半导体器件的制造方法中的另一步工序的示意图;

32.图6为本发明实施例提供的一种半导体器件的制造方法中的另一步工序的示意

图;

33.图7a为本发明实施例提供的采用毡式等离子体刻蚀纵向或横向相邻的两个下电极之间的支撑层的初始时的具体放大图;

34.图7b为本发明实施例提供的采用毡式等离子体刻蚀纵向或横向相邻的两个下电极之间的支撑层的刻蚀中某一时的具体放大图;

35.图7c为本发明实施例提供的采用毡式等离子体刻蚀纵向或横向相邻的两个下电极之间的支撑层的刻蚀中另一时的具体放大图;

36.图7d为本发明实施例提供的采用毡式等离子体刻蚀纵向或横向相邻的两个下电极之间的支撑层的刻蚀中完成时的具体放大图。

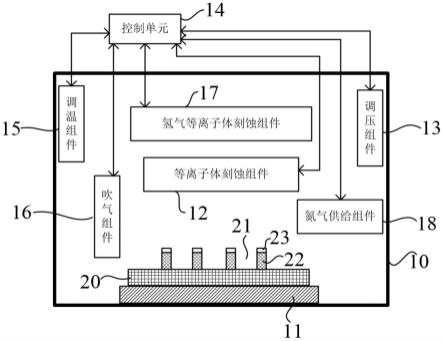

37.附图标记:

38.10-基底 11-着陆焊盘 12-隔离部

39.20-下电极 30-支撑线 40-电容孔

40.51-牺牲膜层 52-刻蚀阻挡层

41.53-支撑层 54-下电极材料层

具体实施方式

42.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

43.为了方便理解本发明实施例提供的半导体器件,下面首先说明一下本发明实施例提供的半导体器件的应用场景,该半导体器件应用于具有电容器的存储器中。下面结合附图对该半导体器件进行详细的叙述。

44.参考图2a及图2b,本发明实施例提供的半导体器件包括一基底10、形成在基底10中的着陆焊盘11图案、形成在基底10上的下电极20图案、以及形成在下电极20图案之间的支撑结构。其中,着陆焊盘11图案包括多个呈阵列排列的着陆焊盘11。下电极20图案包括多个呈阵列排列的下电极20,多个下电极20与多个着陆焊盘11一一对应;每个下电极20为筒状结构,且每个下电极20的底部与对应的着陆焊盘11接触。支撑结构包括环绕连接在纵向或横向任意相邻的两个下电极20之间的支撑线30。

45.在上述的方案中,通过设置连接在纵向或横向任意相邻的两个下电极20之间的支撑线 30,形成栅格状的支撑结构,以提高对下电极20的支撑效果,防止下电极20倾斜、弯曲或塌陷。下面结合附图对上述各个部件的设置方式进行详细的介绍。

46.在设置基底10时,参考图2b,该基底10可以是包括单一半导体材料的结构,如单晶硅基底10、多晶硅基底10等。该基底10也可以是已经形成有部分半导体结构的叠层结构。例如,参考图2b,基底10可以至少包括半导体衬底、晶体管、位线结构、存储接触部、绝缘部、着陆焊盘11图案和隔离部12。晶体管可以形成在半导体器件的半导体衬底上。位线结构可以形成在晶体管的上方。存储接触部和绝缘部形成在相邻位线结构之间。存储接触部与晶体管所具有的源区或漏区接触。绝缘部用于隔离相邻两个存储接触部。着陆焊盘11 图案包括多个阵列排列的着陆焊盘11,每个着陆焊盘11形成在与之对应的存储接触部上。着陆焊盘

11通过存储接触部与晶体管所具有的源区或漏区电连接。隔离部12形成在位线结构和绝缘部上,隔离部12用于隔离相邻两个着陆焊盘11。

47.在设置下电极20图案时,参考图2a及图2b,下电极20图案包括多个呈阵列排列的下电极20,多个下电极20与多个着陆焊盘11一一对应。每个下电极20为筒状结构,且每个下电极20的底部与对应的着陆焊盘11接触。即每个下电极20包括中空的筒壁、以及连接在中空的筒壁下方的筒底,且筒底与对应的着陆焊盘11接触。在确定下电极20的材料时,下电极20的材料可以为氮化钛或多晶硅。即下电极20的材料可以为氮化钛,也可以为多晶硅。

48.在设置支撑结构时,参考图2a及图2b,支撑结构形成在下电极20图案之间,以对下电极20进行支撑。支撑结构包括连接在纵向或横向任意相邻的两个下电极20之间的支撑线30。即在纵向或横向的任意相邻的两个下电极20之间,设置有支撑线30,支撑线30的一端连接在该两个下电极20中的一个下电极20的外壁上,另一端连接在该两个下电极20 中的另一个下电极20的外壁上,使纵向或横向的相邻的两个下电极20通过支撑线30连接,从而提高对下电极20的支撑效果。由于纵向或横向任意相邻的两个下电极20之间均设置有支撑线30,使支撑结构从整体上看是栅格状结构。相比分散设置的支撑环的方式,通过支撑线30连接横向及纵向连接相邻的两个下电极20,能够提高支撑结构的稳定性,从而提高对下电极20的支撑效果,防止下电极20倾斜、弯曲或塌陷。需要解释的是,纵向及横向分别指呈阵列排列中的两个相互垂直的排列方向,其中一个排列方向与纵向,另一个排列方向为横向。

49.如图2b所示,支撑结构可以设置在下电极20图案的顶部位置,使支撑结构能够在下电极20的图案顶部进行支撑,进一步提高支撑效果。当然,支撑结构还可以设置在下电极 20图案的中间高度位置等其他的高度位置。

50.在确定支撑结构的材料时,支撑结构的材料可以为sin、sibn或sicn。即支撑结构的材料可以为sin,也可以为sibn,还可以为sicn。

51.在确定支撑结构的厚度时,支撑线30的厚度可以均在10nm~500nm之间,以提高支撑效果。即支撑线30的厚度可以在10nm、50nm、100nm、150nm、250nm、300nm、350nm、 400nm、450nm、500nm等介于10nm~500nm之间的任意值。

52.在继续设置介质层及上电极,以完成整个电容器的制造时,可以在下电极20的内侧壁、外侧壁及支撑结构上均形成有上电极、以及将下电极20与上电极绝缘隔离的介质层。即在下电极20的内外侧均设置电容器结构,以提高电容器的电容,提高存储效果。应当理解的是,设置介质层及上电极的方式并不限于上述的方式,除此之外,还可以采用其他的方式。例如,还可以仅在下电极20的内侧壁及底壁上形成介质层及上电极,在下电极20的外侧壁上不形成介质层及上电极。

53.通过设置连接在纵向或横向任意相邻的两个下电极20之间的支撑线30,形成栅格状的支撑结构,以提高对下电极20的支撑效果,防止下电极20倾斜、弯曲或塌陷。

54.另外,本发明实施例还提供了一种半导体器件的制造方法,该制造方法包括:

55.步骤一:提供一基底10,基底10中形成有着陆焊盘11图案,着陆焊盘11包括多个呈阵列排列的着陆焊盘11;

56.步骤二:在基底10上形成下电极20图案,下电极20图案包括多个呈阵列排列的下电极20,多个下电极20与多个着陆焊盘11一一对应;每个下电极20为筒状结构,且每个下电极20的底部与对应的着陆焊盘11接触;

57.步骤三:在下电极20图案中形成支撑结构,支撑结构包括连接在纵向或横向任意相邻的两个下电极20之间的支撑线30。

58.在上述的方案中,通过设置连接在纵向或横向任意相邻的两个下电极20之间的支撑线 30,形成栅格状的支撑结构,以提高对下电极20的支撑效果,防止下电极20倾斜、弯曲或塌陷。下面结合附图对上述每一步骤进行详细的介绍。

59.首先,提供一基底10,基底10中形成有着陆焊盘11图案,着陆焊盘11包括多个呈阵列排列的着陆焊盘11。参考图3a,该基底10可以是包括单一半导体材料的结构,如单晶硅基底10、多晶硅基底10等。该基底10也可以是已经形成有部分半导体结构的叠层结构。例如,参考图3a,基底10可以至少包括半导体衬底、晶体管、位线结构、存储接触部、绝缘部、着陆焊盘11图案和隔离部12。晶体管可以形成在半导体器件的半导体衬底上。位线结构可以形成在晶体管的上方。存储接触部和绝缘部形成在相邻位线结构之间。存储接触部与晶体管所具有的源区或漏区接触。绝缘部用于隔离相邻两个存储接触部。着陆焊盘11 图案包括多个阵列排列的着陆焊盘11,每个着陆焊盘11形成在与之对应的存储接触部上。着陆焊盘11通过存储接触部与晶体管所具有的源区或漏区电连接。隔离部12形成在位线结构和绝缘部上,隔离部12用于隔离相邻两个着陆焊盘11。

60.接下来,在基底10上形成下电极20图案。具体加工时,参考图3a,可以先在基底10 的上方,形成覆盖基底10的牺牲膜层51。之后,参考图3a及图3b,从上向下刻蚀牺牲膜层51,形成电容孔40图案,其中,电容孔40图案包括多个呈阵列排列的电容孔40,多个电容孔40与多个着陆焊盘11一一对应,每个电容孔40与对应的着陆焊盘11连通。之后,参考图5,在电容孔40图案中的每个电容孔40的孔壁及底部形成每个下电极20,以形成下电极20图案。

61.参考图3a,在基底10的上方形成覆盖基底10的牺牲膜层51之前,可以在基底10上形成覆盖基底10的刻蚀阻挡层52。此时,牺牲膜层51并未直接设置在基底10上,牺牲膜层51与基底10之间通过刻蚀阻挡层52隔开。通过在牺牲膜层51及基底10之间层叠刻蚀阻挡层52,以防止后续刻蚀或清洗等操作对基底10造成影响,确保基底10品质。在确定刻蚀阻挡层52的材料时,刻蚀阻挡层52的材料可以选择sin、sibn或sicn,以提高刻蚀时的阻挡效果。在牺牲膜层51与着陆焊盘11之间设置有刻蚀阻挡层52时,还需要对刻蚀阻挡层52进行刻蚀,使电容孔40与着陆焊盘11连通。应当注意的是,还可以使牺牲膜层 51与基底10之间直接接触,即采用牺牲膜层51与基底10之间没有刻蚀阻挡层52隔开的方式。

62.参考图3a,在牺牲膜层51上刻蚀形成电容孔40图案之前,还可以在牺牲膜层51的上方,形成覆盖牺牲膜层51的支撑层53。此时,刻蚀牺牲膜层51,形成电容孔40图案时,需要从上向刻蚀支撑层53及牺牲膜层51,以形成电容孔40图案。

63.在加工下电极20时,参考图4,可以先在牺牲膜层51及电容孔40的孔底及内壁上沉积下电极材料层54。参考图5,之后去除下电极材料层54中位于电容孔40外的部分,形成下电极20。其中,可以采用等离子体刻蚀或湿法刻蚀的方式,以便于去除下电极材料层 54中位于电容孔40外的部分。

64.接下来,在下电极20图案中形成支撑结构。在下电极20图案之间形成支撑结构时,参考图6、图7a~图7d,可以采用毯式等离子体刻蚀工艺刻蚀所述支撑层53,形成如图2b 所示出的支撑结构。无需采用光刻工艺形成支撑结构,简化支撑结构的形成方式,简化工艺。采用毯式等离子体刻蚀支撑层53时,支撑层53中位于下电极20的较窄的位置,刻蚀速率越

慢;支撑层53中位于下电极20的较宽的位置,刻蚀速率越快。其中,在纵向或横向上相邻的两个下电极20之间的位置为较窄的位置。既不在纵向相邻,又不在横向相邻,而是在对角线方向相邻的两个下电极20之间的位置为较宽的位置。采用上述刻蚀方式,以便于形成栅格状的支撑结构,便于将位于支撑层53下方的牺牲膜层51去除。

65.接下来,可以通过栅格状的支撑结构的开口处去除牺牲膜层51,形成如图2a及图2b 所示的结构,以便于将位于支撑层53下方的牺牲膜层51去除。

66.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。