1.本技术实施例涉及存储技术领域,特别涉及一种存储器的编程方法、存储器及存储系统。

背景技术:

2.近年来,为了进一步提高存储器的存储密度,三维存储器应运而生。三维存储器是指将多个存储串按照阵列方式排布的一种存储器,其中,每个存储串包括多个串联连接的存储单元,每个存储单元包括一个浮栅或电子俘获层,该浮栅或电子俘获层用于存储数据。

3.三维存储器中,对选择字线(word line,wl)所耦合的一行存储单元中待编程的目标存储单元进行编程时,需要向选择字线加载编程电压,该编程电压能够驱使目标存储单元的沟道中的电子隧穿至浮栅或电子俘获层,从而实现将数据写入目标存储单元(也即是实现对目标存储单元的编程)。前述编程过程中,存储器中除目标存储单元外其他存储单元的沟道电子也可能发生隧穿,这样会影响后续对其他存储单元的编程或数据读取,也即是导致其他存储单元中产生干扰。

技术实现要素:

4.本技术实施例提供了一种存储器的编程方法、存储器及存储系统,可以提高对存储器进行预充电的灵活性。所述技术方案如下:

5.一方面,提供了一种编程方法,所述方法包括:

6.在目标编程操作的第一预充电阶段,基于第一预充电方式对所述存储器进行预充电;

7.在所述目标编程操作的第二预充电阶段,基于第二预充电方式对所述存储器进行预充电;

8.其中,所述目标编程操作是指对同一个选择字线所耦合的存储单元行执行的编程操作,所述第一预充电阶段与所述目标编程操作的第一编程阶段对应,所述第二预充电阶段与所述目标编程操作的第二编程阶段对应,所述存储单元行中待编程存储单元在所述第二编程阶段后达到的编程态,高于在所述第一编程阶段后达到的编程态,所述第一预充电方式和所述第二预充电方式不同。

9.在一种可能的实现方式中,所述第一预充电方式采用第一预充电模式和第一预充电时长进行预充电,所述第二预充电方式采用第二预充电模式和第二预充电时长进行预充电;

10.所述第一预充电模式和所述第二预充电模式之间,所述第一预充电时长和所述第二预充电时长之间,存在至少一者不同。

11.在一种可能的实现方式中,所述第一预充电模式和所述第二预充电模式不同。

12.在一种可能的实现方式中,所述第一预充电模式和所述第二预充电模式相同,且所述第二预充电时长大于所述第一预充电时长。

13.在一种可能的实现方式中,所述第一预充电模式包括如下两种方式中的至少一者:

14.向所述存储器的漏极选择线加载第一导通电压,向所述存储器的位线加载第一预充电电压;

15.向所述存储器的源极选择线加载第二导通电压,向所述存储器的源极线加载第二预充电电压。

16.在一种可能的实现方式中,所述第二预充电模式包括如下两种方式中的至少一者:

17.向所述存储器的漏极选择线加载第一偏置电压,向所述存储器的位线加载第二偏置电压,所述第二偏置电压高于所述第一偏置电压;

18.向所述存储器的源极选择线加载第三偏置电压,向所述存储器的源极线加载第四偏置电压,所述第四偏置电压高于所述第三偏置电压。

19.在一种可能的实现方式中,所述方法还包括:

20.在所述目标编程操作的第三预充电阶段,基于第三预充电方式对所述存储器进行预充电;

21.其中,所述第三预充电阶段与所述目标编程操作的第三编程阶段对应,所述存储单元行中待编程存储单元在所述第三编程阶段后达到的编程态,高于在参考编程阶段后达到的编程态,所述参考编程阶段为所述第一编程阶段或所述第二编程阶段;

22.所述第三预充电方式与参考预充电方式采用相同的预充电模式,所述第三预充电方式采用的预充电时长大于所述参考预充电方式采用的预充电时长,所述参考预充电方式为所述参考编程阶段对应的预充电阶段采用的预充电方式。

23.在一种可能的实现方式中,所述方法还包括:

24.在所述目标编程操作的第四编程阶段之前,不对所述存储器进行预充电;

25.其中,所述存储单元行中待编程存储单元在所述第四编程阶段后达到的编程态,低于在所述第一编程阶段后达到的编程态。

26.另一方面,提供了一种存储器,所述存储器包括:

27.存储阵列,所述存储阵列包括多个存储单元行;

28.多个字线,所述多个字线分别耦合到所述多个存储单元行;以及

29.外围电路,所述外围电路耦合到所述多个字线并且被配置为:

30.在目标编程操作的第一预充电阶段,基于第一预充电方式对所述存储器进行预充电;

31.在所述目标编程操作的第二预充电阶段,基于第二预充电方式对所述存储器进行预充电;

32.其中,所述目标编程操作是指对同一个选择字线所耦合的存储单元行执行的编程操作,所述第一预充电阶段与所述目标编程操作的第一编程阶段对应,所述第二预充电阶段与所述目标编程操作的第二编程阶段对应,所述存储单元行中待编程存储单元在所述第二编程阶段后达到的编程态,高于在所述第一编程阶段后达到的编程态,所述第一预充电方式和所述第二预充电方式不同。

33.在一种可能的实现方式中,所述第一预充电方式采用第一预充电模式和第一预充

电时长进行预充电,所述第二预充电方式采用第二预充电模式和第二预充电时长进行预充电;

34.所述第一预充电模式和所述第二预充电模式之间,所述第一预充电时长和所述第二预充电时长之间,存在至少一者不同。

35.在一种可能的实现方式中,所述第一预充电模式和所述第二预充电模式不同。

36.在一种可能的实现方式中,所述第一预充电模式和所述第二预充电模式相同,且所述第二预充电时长大于所述第一预充电时长。

37.在一种可能的实现方式中,所述第一预充电模式包括如下两种方式中的至少一者:

38.向所述存储器的漏极选择线加载第一导通电压,向所述存储器的位线加载第一预充电电压;

39.向所述存储器的源极选择线加载第二导通电压,向所述存储器的源极线加载第二预充电电压。

40.在一种可能的实现方式中,所述第二预充电模式包括如下两种方式中的至少一者:

41.向所述存储器的漏极选择线加载第一偏置电压,向所述存储器的位线加载第二偏置电压,所述第二偏置电压高于所述第一偏置电压;

42.向所述存储器的源极选择线加载第三偏置电压,向所述存储器的源极线加载第四偏置电压,所述第四偏置电压高于所述第三偏置电压。

43.在一种可能的实现方式中,所述外围电路还被配置为:

44.在所述目标编程操作的第三预充电阶段,基于第三预充电方式对所述存储器进行预充电;

45.其中,所述第三预充电阶段与所述目标编程操作的第三编程阶段对应,所述存储单元行中待编程存储单元在所述第三编程阶段后达到的编程态,高于在参考编程阶段后达到的编程态,所述参考编程阶段为所述第一编程阶段或所述第二编程阶段;

46.所述第三预充电方式与参考预充电方式采用相同的预充电模式,所述第三预充电方式采用的预充电时长大于所述参考预充电方式采用的预充电时长,所述参考预充电方式为所述参考编程阶段对应的预充电阶段采用的预充电方式。

47.在一种可能的实现方式中,所述外围电路还被配置为:

48.在所述目标编程操作的第四编程阶段之前,不对所述存储器进行预充电;

49.其中,所述存储单元行中待编程存储单元在所述第四编程阶段后达到的编程态,低于在所述第一编程阶段后达到的编程态。

50.另一方面,提供了一种存储系统,所述存储系统包括:

51.上述另一方面提供的任一所述的存储器;

52.以及耦合到所述存储器并且被配置为控制所述存储器的控制器。

53.在本技术实施例中,在对存储器中同一个选择字线所耦合的存储单元行执行目标编程操作时,在目标编程操作的不同编程阶段对应的预充电阶段内,采用不同的预充电方式进行预充电,提高了预充电的灵活性。另外,如果编程阶段后该存储单元行中待编程存储单元达到的编程态越高,该编程阶段中编程干扰越严重。为了后续便于说明,将编程后存储

selection gate,顶部选择栅极)或漏极选择栅极,第二选择管113也称为下选择管或bsg(bottom selection gate,底部选择栅极)或源极选择栅极。

73.如图1所示,对于任一存储串110,该存储串110的第一选择管111的漏极耦合到bl(bit line,位线),第一选择管111的源极和该存储串110自上而下的第一个存储单元112的漏极连接,该存储串110的多个存储单元112串联连接,该存储串110自上而下的最后一个存储单元112的源极和第二选择管113的漏极连接,第二选择管113的源极耦合到sl(source line,源极线)。sl可以由acs(array common source,阵列公共源极)提供。此时,acs由同一块中的存储串共享,因此acs也称为公共源极线。关于块的内容后续有详细解释说明,在此先不展开阐述。

74.其中,多个存储单元112中的每个存储单元112由控制栅极控制,控制栅极耦合至wl(word line,字线)。第一选择管111的栅极和dsl(drain select line,漏极选择线)耦合,第二选择管113的栅极和ssl(source select line,源极选择线)耦合。

75.需要说明的是,图1所示的存储串可以被划分为多个块,每个块包括多个存储串。块是对存储器执行擦除操作的最小单位,每个块中沿平行于衬底方向的同一平面(图1中xy所在平面)的各个存储单元112的控制栅极耦合至同一字线,图1中示例地有wl1至wlm等m个字线,这m个字线可以称为一组字线。不难理解,对于整个三维存储器,该存储器可以包括多组字线,这多组字线的功能基本相同。

76.如图1所示,位于同一yz平面的各个存储串的第一选择管111的漏极耦合至同一位线,也即是,位于同一yz平面的各个存储串的第一选择管111的漏极共享同一个位线,图1中示例地有bl1至bln等n个位线,每个位线耦合一个yz平面内的各个存储串中的第一选择管111的漏极。

77.此外,存储串110上可以有多个第一选择管111或多个第二选择管113,图1是以存储串上包括一个第一选择管111和一个第二选择管113为例进行说明。如图1所示,位于同一xz平面的存储串中同一行的第一选择管111的栅极共享一个dsl,位于同一xz平面的存储串中同一行的第二选择管113的栅极共享一个ssl。图1中示例地有dsl1至dslx等x个dsl,每个dsl耦合一个xz平面内的存储串中同一行的第一选择管111的栅极。相应地,图1中也有ssl1至sslx等x个ssl(图1中未示出),每个ssl耦合一个xz平面内的存储串中同一行的第二选择管113的栅极。

78.如图1所示,在每个存储串110的第一选择管111和存储单元112之间还可以设置有至少一个虚拟存储单元(dummy cell)114,第二选择管113与存储单元112之间也设置有至少一个虚拟存储单元(dummy cell)115。虚拟存储单元114和115的作用是保护wl和tsg,本技术实施例对虚拟存储单元的相关解释不做过多说明。

79.同一块中位于一个xy平面内的各个虚拟存储单元可称为一个虚设层。靠近bl这一侧的虚设层可称为顶部虚拟层,靠近sl这一侧的虚设层可称为底部虚拟层。如图1所示,同一虚设层中的虚拟存储单元的控制栅极耦合至同一dwl(dummy word line,伪字线)。

80.另外,图1中的每个存储串可以包括32个存储单元,也可以包括64个存储单元,本技术实施例对每个存储串包括的存储单元的数量不做限定。

81.图1所示的三维存储器的结构是本技术实施例涉及的三维存储器的一种示例说明,该三维存储器还可以包括其他图1中未示出的部件,在此不再一一展开说明。换句话说,

本技术实施例并不限定三维存储器的结构,本技术实施例涉及的三维存储器可以为任意阵列式排布的三维存储器。

82.对于图1所示的三维存储器,假设当前需要对其中的目标存储单元进行编程,目标存储单元可以为一个或多个(图1中以一个为例进行说明)。为了后续便于说明,将目标存储单元所在的存储串上的tsg耦合的dsl称为选择dsl(即图1中的dsl1),将dsl1至dsln中的其他dsl称为未选择dsl,其中选择dsl耦合的存储串通常称为选择存储串,未选择dsl耦合的存储串通常称为未选择存储串。将目标存储单元所在的存储串耦合的bl称为编程的bl(即图1中的bln),将bl1至bln中其他的bl称为禁止编程的bl,将目标存储单元耦合的字线称为选择字线(即图1中的wm-1),将wl1至wlm中的其他字线称为未选择字线。基于此,对目标存储单元进行编程的具体过程如下。

83.(1)向编程的bl加载较低的v

ss

(通常为0v),向禁止编程的bl加载其他电压(比如vcc)。

84.其中,编程的bl上加载较低的v

ss

的目的是:后续在目标存储单元的控制栅极加载编程电压后,目标存储单元的控制栅极和沟道之间有较大的电势差,从而驱使沟道中的电子进入目标存储单元的电子俘获层或浮栅,以实现对目标存储单元的编程。

85.禁止编程的bl上加载其他电压的目的是:通过vcc等其他电压使禁止编程的bl耦合的选择存储串的沟道电势升高(boosting),从而禁止这些存储串被编程(program inhibit)。

86.另外,如图1所示,由于编程的bln耦合了沿y方向排布的多个存储串,因此,在对编程的bln加载v

ss

的同时,还需通过第一选择管(tsg)111来关闭bln耦合的未选择存储串,以避免bln耦合的未选择存储串被编程。

87.具体地,可以向选择dsl(即图1中dsl1)加载导通电压,以打开选择dsl所耦合的选择存储串的tsg,向未选择dsl加载vss(通常为0v),以关闭未选择dsl所耦合的未选择存储串的tsg。

88.(2)在选择字线上加载编程电压(v

pgm

),在未选择字线上加载导通电压(vpass)。

89.由于目标存储单元所在存储串上除了目标存储单元外,还有其他存储单元,因此,将未选择字线上加载vpass,以使目标存储单元所在存储串上其他存储单元的源极和漏极导通,从而使得编程的bl上加载的低电位v

ss

加载到目标存储单元的沟道上。

90.图2是本技术实施例提供的一种编程阶段中各个端口的电压波形图。如图2所示,在编程阶段,选择dsl上加载导通电压以导通选择dsl所耦合的选择存储串的tsg,同时编程的bl加载较低电位v

ss

,v

ss

通过导通的tsg加载到目标存储单元所在存储串的沟道上。此外,公共源极acs上加载电压,目的在于:使目标存储单元所在存储串的bsg对应的cmos彻底关断,减小其漏电流。

91.如图2所示,未选择dsl上不加载导通电压,从而关闭未选择存储串的tsg。另外,禁止编程的bl上加载电压v

cc

,该电压v

cc

能够抑制禁止编程的bl耦合的选择存储串被编程。

92.此外,如图1和图2所示,在z方向上,除选择字线外,未选择字线上加载vpass,以使目标存储单元所在存储串上的其他存储单元导通。选择字线上加载v

pgm

,以使目标存储单元被编程。

93.在上述编程阶段中,由于v

pgm

通常较大,因此目标存储单元的控制栅极和沟道之间

有较大的电压差,该电压差大于超过隧穿电压,如此该目标存储单元沟道区的电子隧穿后进入电子俘获层或浮栅,而完成对该目标存储单元的编程。

94.另外,由于vpass通常小于v

pgm

,因此目标存储单元所在存储串中其他存储单元的控制栅极和沟道之间的电压差低于隧穿电压,从而使得这部分存储单元无法被编程,也即是禁止编程。

95.此外,对于未选择存储串上的存储单元,由于这些未选择存储串的第一选择管111处于关闭状态,因此这些未选择存储串的沟道浮空,使得未选择存储串上的存储单元沟道中的电子基本不会隧穿进入电子俘获层或浮栅,达到禁止编程的作用。

96.对于禁止编程的bl所耦合的选择存储串上的存储单元,通过vcc等其他电压使禁止编程的bl耦合的选择存储串的沟道电势升高(boosting),以实现上述禁止编程的作用。

97.通过以上过程,便可实现对目标存储单元进行编程,并且其他存储单元均不会被编程。

98.在上述编程操作的过程中,由于v

pgm

通常较高,对于选择字线耦合的被禁止编程的存储单元,也可能引起电荷载流子的隧穿,从而引起选择字线耦合的被禁止编程的存储单元的阈值电压发生偏移,导致影响后续对这些存储单元的编程和数据读取,也即是,对这些存储单元产生了编程干扰。编程干扰也称为v

pgm

干扰。

99.另外,在上述编程操作过程中,虽然未选择字线上加载的vpass低于v

pgm

,但是未选择字线所耦合的存储单元的沟道的电子也可能隧穿,进而产生vpass干扰。

100.为了抑制上述两类干扰,在对选择字线加载编程电压的过程中,在加载编程电压前,对存储器的沟道进行预充电。通过预充电可以抬高沟道电势,这样后续对目标存储单元进行编程时,存储器的其他存储单元的沟道和控制栅之间的压差较小,从而避免这些存储单元的沟道电子发生隧穿,也即避免产生v

pgm

干扰或vpass干扰。

101.本技术实施例提供的编程方法就应用于上述通过预充电方式来抑制干扰的场景中。

102.另外,本技术实施例中,对目标存储单元的编程可以通过ispp技术实现。ispp技术的基本原理为:通过选择字线向选择字线所耦合的存储单元行的控制栅极依次加载幅值渐增的编程脉冲,在每加载一次编程脉冲,验证选择字线所耦合的存储单元行中待编程的各个存储单元的编程态是否达到目标编程态,如果某个存储单元的编程态达到目标编程态,则通过控制该存储单元所属的存储串耦合的bl以及所属的存储串的tsg,实现后续该存储单元被禁止编程,下一个编程脉冲则仅针对未达到目标编程态的存储单元继续编程。因此针对选择字线所耦合的存储单元行的编程操作包括多个编程循环(loop),每个编程循环包括加载一个编程脉冲的过程和验证编程态的过程,也即是每个编程循环包括一个编程阶段和验证阶段。此外,在本技术实施例中,每个编程阶段前还可选地包括预充电阶段。

103.下面对本技术实施例提供的编程方法进行详细解释说明。

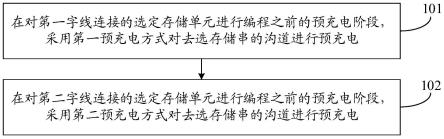

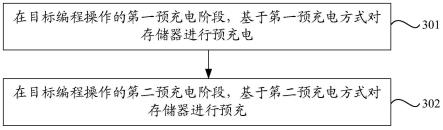

104.图3是本技术实施例提供的一种编程方法流程图。如图3所示,该方法包括如下几个步骤。

105.步骤301:在目标编程操作的第一预充电阶段,基于第一预充电方式对存储器进行预充电。

106.步骤302:在目标编程操作的第二预充电阶段,基于第二预充电方式对存储器进行

预充电。

107.其中,目标编程操作是指对同一个选择字线所耦合的存储单元行执行的编程操作。也即,目标编程操作是指对同一存储单元行执行的编程操作。

108.在本技术实施例中,在对同一个选择字线所耦合的存储单元行进行目标编程操作的过程中,可以在编程操作的不同编程阶段之前的预充电阶段,对存储器进行不同的预充电处理。不仅提高了预充电的灵活性,还能使得预充电更加适应具体的场景,从而提高预充电在抑制编程干扰上的效果。

109.基于此,在上述步骤301和步骤302中,第一预充电阶段与目标编程操作的第一编程阶段对应,第二预充电阶段与目标编程操作的第二编程阶段对应,该同一个选择字线所耦合的存储单元行中待编程存储单元在第二编程阶段后达到的编程态,高于这些存储单元在第一编程阶段后达到的编程态,第一预充电方式和第二预充电方式不同。

110.其中,第一预充电阶段与目标编程操作的第一编程阶段对应,也即第一预充电阶段为在第一编程阶段前进行预充电的阶段。第二预充电阶段与目标编程操作的第二编程阶段对应,也即第二预充电阶段为在第二编程阶段前进行预充电的阶段。

111.需要解释说明的是,对选择字线所耦合的存储单元行执行目标编程操作具体是指:依次向选择字线加载编程脉冲,在依次加载编程脉冲的过程中,该存储单元行中的各个待编程存储单元达到相应的目标编程态。为了便于理解,以三级单元(triple-level cell,tlc)存储器为例进行说明,tlc存储器的编程态包括l0、l1、l2、l3、l4、l5、l6、l7这八个编程态。基于此,选择字线所耦合的存储单元行中的待编程存储单元可以分为八类,每一类存储单元的目标编程态相同。在执行目标编程操作时,逐渐向选择字线加载编程脉冲,以实现逐步让每类存储单元达到相应的目标编程态。

112.其中,在加载编程脉冲后,对于任一类存储单元,如果该类存储单元中大部分存储单元达到相应目标编程态,则认为该类存储单元完成了编程(也即完成了针对相应目标编程态的编程),后续则禁止对该类存储单元进行编程。

113.基于上述解释说明,该同一个选择字线所耦合的存储单元行中待编程存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态,可以有多种实现方式。下面示例说明。

114.在一种可能的实现方式中,该同一个选择字线所耦合的存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态,可以理解为:在第二编程阶段后目标编程态为第二编程态的存储单元中超过参考比例(参考比例示例可以为98.5%至99.5%之间的一个数值,比如99%)的存储单元达到第二编程态,在第一编程阶段后目标编程态为第一编程态的存储单元中超过该参考比例的存储单元达到第一编程态,其中,第二编程态高于第一编程态。也即,第二编程阶段完成的目标编程态高于第一阶段完成的目标编程态。

115.比如,对于tlc存储器,在第二编程阶段后目标编程态为l7的存储单元中超过99%的存储单元达到编程态l7,而在第一编程阶段后目标编程态为l6的存储单元中超过99%的存储单元达到编程态l6。

116.在另一种可能的实现方式中,该同一个选择字线所耦合的存储单元行中待编程存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态,还可以理解为:在第二编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最高目标编

程态,高于在第一编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最高目标编程态。比如,对于tlc存储器,在第二编程阶段后各存储单元中达到的最高目标编程态为l7,而在第一编程阶段后各个存储单元中达到的最高目标编程态l6。

117.或者,在第二编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最低目标编程态,高于在第一编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最低目标编程态。

118.需要说明的是,上述最低目标编程态或最高编程态之间的大小关系,可以通过相应的验证电压来确定。

119.其中,如果第二编程阶段后验证电压中的最高电压,比第一编程阶段后验证电压中的最高电压大,则表明在第二编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最高目标编程态,高于在第一编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最高目标编程态。

120.或者,如果第二编程阶段后验证电压中的最低电压,比第一编程阶段后验证电压中的最低电压大,则表明在第二编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最低目标编程态,高于在第一编程阶段后待编程存储单元中各个存储单元达到的目标编程态的最低目标编程态。

121.在另一种可能的实现方式中,该同一个选择字线所耦合的存储单元行中待编程存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态,还可以理解为:这些存储单元中的指定存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态。比如,对于该同一个选择字线所耦合的存储单元行中的待编程存储单元a,在第二编程阶段后存储单元a达到的编程态为l7,而在第一编程阶段后存储单元a达到的编程态为l6。

122.上述几种实现方式用于举例说明,需要说明的是,本技术实施例不限定“该同一个选择字线所耦合的存储单元行中待编程存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态”的具体实现方式,在此不再一一举例说明。

123.基于前述关于ispp技术的基本原理可知,针对该同一个选择字线的目标编程操作包括多个依次执行的编程循环,每个编程循环包括一个编程阶段,并且依次执行的编程阶段对应的编程电压是逐渐增加的。可以理解的是,编程电压越高,编程阶段后存储单元达到的编程态越高。因此可以预先将目标编程操作划分为不同的时间段,然后基于不同的时间段中的编程阶段实现本技术实施例提供的预充电方法。

124.示例地,可以将编程操作划分为两个时间段,分别称为第一时间段和第二时间段,其中第一时间段位于第二时间段之前,将第一时间段中的编程阶段称为第一编程阶段,将第二时间段中的编程阶段称为第二编程阶段。

125.可选地,也可以将编程操作划分为更多的时间段,比如三个时间段或四个时间段。本技术实施例对此不做限定。比如,在将编程操作划分为三个时间段的情况下,按照从前到后依次命名为第三时间段、第一时间段和第二时间段,这三个时间段中的编程阶段则分别称为第三编程阶段、第一编程阶段以及第二编程阶段。又比如,在将编程操作划分为四个时间段的情况下,按照从前到后依次命名为第四时间段、第三时间段,第一时间段和第二时间段,这四个时间段中的编程阶段则分别称为第四编程阶段,第三编程阶段、第一编程阶段以

及第二编程阶段。

126.需要说明的是,上述的第一编程阶段、第二编程阶段、第三编程阶段以及第四编程阶段是为了后续便于说明,按照实际需求命名的,并不限定各个编程阶段的实际执行顺序,本技术实施例对划分后的编程阶段的名称并不限定。

127.在一种可能的实现方式中,在针对该同一个选择字线所耦合的存储单元行执行目标编程操作的起始时间和结束时间明确的情况下,可以直接将该目标编程操作的时间段划分为不同的时间段。然后在不同时间段中的编程阶段上实现本技术实施例提供的编程方法。

128.在另一种可能的实现方式中,由于目标编程操作具体是指:向选择字线加载一系列幅值渐增的编程电压,以使选择字线所耦合存储单元逐渐被编程。因此,可以根据选择字线被加载的编程电压的幅值划分不同的时间段。比如,可以将选择字线上加载的编程电压低于某个参考电压的时间段作为一个时间段,将选择字线上加载的编程电压高于某个参考电压的时间段作为一个时间段,从而实现将编程操作的时间段划分为不同的时间段。

129.示例地,前述第一时间段是指编程操作过程中加载的编程电压高于第一参考电压但低于第二参考电压的时间段;第二时间段是指编程操作过程中加载的编程电压高于第二参考电压的时间段,第三时间段是指编程操作过程中加载的编程电压低于第一参考电压但高于第三参考电压的时间段,第四时间段是指编程操作过程中加载的编程电压低于第三参考电压的时间段。如此,第四时间段中的第四编程阶段中加载的编程电压,低于所述第三时间段中的第三编程阶段中加载的编程电压,第三时间段中的第三编程阶段中加载的编程电压,低于所述第一时间段中的第一编程阶段中加载的编程电压,而第二时间段中的第二编程阶段中加载的编程电压,高于第一时间段中的第一编程阶段中加载的编程电压。

130.如前述内容可知,编程阶段中加载的编程电压越高,编程阶段后待编程存储单元达到的编程态越高。因此,第四编程阶段和第三编程阶段可以称为低编程态的编程阶段,第一编程阶段可以称为中间编程态的编程阶段,第二编程阶段可以称为高编程态的编程阶段。或者,第四编程阶段可以称为低编程态的编程阶段,第三编程阶段和第一编程阶段可以称为中间编程态的编程阶段,第二编程阶段可以称为高编程态的编程阶段。在此不再一一举例说明。

131.上述第一参考电压、第二参考电压以及第三参考电压可以是预先配置的电压数值。其中,第三参考电压可以是稍微大于0的一个数值,第二参考电压可以是稍微低于编程电压的最大幅值的一个数值,第一参考电压是位于第三参考电压和第二参考电压之间的一个数值。本技术实施例并不限定如何设置第一参考电压、第二参考电压以及第三参考电压的具体过程。

132.在另一种可能的实现方式中,由于目标编程操作具体是指:向选择字线加载一系列幅值渐增的编程电压。因此,还可以按照加载到选择字线的编程电压的数量来划分时间段。比如,将加载前几个编程电压的时间段作为一个时间段,将加载中间几个编程电压的时间段作为一个时间段,将加载后面几个编程电压的时间段作为一个时间段。

133.需要说明的是,上述是将针对目标编程操作过程划分不同时间段的示例说明,本技术实施例并不限定具体如何划分时间段。可选地,也可以将加载前几个编程电压的时间段作为一个时间段,将加载前几个编程电压之后到加载到选择字线的编程电压低于某个参

考电压的时间段作为一个时间段,将加载到选择字线的编程电压低超过该参考电压的时间段作为一个时间段。换句话说,上述几种划分时间段的方式可以融合使用。

134.在基于上述方式划分编程阶段之后,便可基于步骤301以及步骤302实现在不同编程阶段之前进行不同方式的预充电。

135.需要说明的是,本技术实施例中“基于预充电方式进行预充电”具体可以是指采用何种预充电模式进行预充电,预充电模式具体是指预充电阶段对三维存储器中各个单元的端口加载电压情况。或者,“基于预充电方式进行预充电”具体可以是指采用何种预充电模式以及采用该预充电模式进行预充电的预充电时长。或者,“基于预充电方式进行预充电”具体可以是指采用指定的预充电模式进行预充电的预充电时长。关于预充电时长的内容将在后续解释说明,在此先不展开阐述。

136.因此,在一种可能的实现方式中,步骤301和步骤302中的第一预充电方式采用第一预充电模式和第一预充电时长进行预充电,第二预充电方式采用第二预充电模式和第二预充电时长进行预充电。这种场景下,第一预充电方式和第二预充电方式不同可以是指:第一预充电模式和第二预充电模式之间,第一预充电时长和第二预充电时长之间,存在至少一者不同。比如,第一预充电模式和第二预充电模式不同。又比如,第一预充电模式和第二预充电模式相同,且第二预充电时长大于第一预充电时长。

137.下面对第一预充电模式和第二预充电模式进行详细解释说明。

138.在一种可能的实现方式中,第一预充电模式包括:向存储器的第一选择线加载导通电压,向存储器的第一信号线加载预充电电压。

139.第一信号线为存储器的位线、且第一选择线为存储器的漏极选择线,和/或,第一信号线为存储器的源极线、且第一选择线为存储器的源极选择线。

140.其中,导通电压用于打开第一选择线和第一信号线直接耦合的选择管,为了后续便于说明,将第一选择线和第一信号线直接耦合的选择管称为第一目标选择管。因此,第一预充电模式可以理解为:通过第一选择线上的加载的导通电压打开第一目标选择管,并通过第一目标选择管所耦合的第一信号线向存储器的沟道加载预充电电压。在向第一信号线加载预充电电压后,存储串中的沟道电子在预充电电压的驱使下向第一目标选择管的方向移动,如此便可降低沟道中的电子浓度,从而提高沟道的电势。也即是,第一预充电模式为驱使沟道中的电子移动至高电势端以提高沟道电势的预充电模式。

141.基于此,第一预充电模式包括如下两种方式中的至少一者:(1)向存储器的漏极选择线加载第一导通电压,向存储器的位线加载第一预充电电压;(2)向存储器的源极选择线加载第二导通电压,向存储器的源极线加载第二预充电电压。

142.另外,由于第一预充电模式中的第一信号线可以为位线和/或源极线,当第一信号线为位线时,第一预充电模式还可称为bl预充电模式,当第一信号线为源极线时,第一预充电模式还可称为acs预充电模式。

143.在一种可能的实现方式中,第二预充电模式包括:向存储器的第二选择线和第二信号线分别加载不同的偏置电压,加载在第二信号线上的偏置电压,高于加载在第二选择线上的偏置电压。

144.其中,第二信号线为存储器的位线、且第二选择线为存储器的漏极选择线,或者,第二信号线为存储器的源极线、且第二选择线为存储器的源极选择线,或者,第二信号线为

位线和源极线、且第二选择线为漏极选择线和源极选择线。也即,在第二预充电模式中,可以通过位线和漏极选择线进行预充电,也可以通过源极线和源极选择线进行预充电,可选地,还可以同时通过位线和漏极选择线、以及源极线和源极选择线进行预充电。

145.为了后续便于说明将第二选择线和第二信号线直接耦合的选择管称为第二目标选择管。基于图1所示的存储器的结构可知,第二信号线耦合在第二目标选择管的非栅极,第二选择线耦合在第二目标选择管的栅极。因此,当向第二选择线和第二信号线分别加载不同的偏置电压,且加载在第二信号线上的偏置电压,高于加载在第二选择线上的偏置电压时,第二目标选择管中将产生gidl(gate-induced drain leakage,栅诱导漏极泄漏)电流。

146.基于此,第二预充电模式可以理解为:在第二目标选择管的栅极和非栅极上加载不同的偏置电压,以使第二目标选择管中产生gidl电流。可以理解的是,gidl电流是由电子-空穴对构成,因此在第二目标选择管中产生gidl电流后,gidl电流中的空穴在沟道电子的吸引下,移动至沟道从而中和沟道电子,从而提高沟道的电势。也即是,第二预充电模式为驱使gidl电流中的空穴移动至沟道以提高沟道电势的预充电模式。因此,第二预充电模式还可称为gidl预充电模式。

147.基于此,第二预充电模式包括如下两种方式中的至少一者:(1)向存储器的漏极选择线加载第一偏置电压,向存储器的位线加载第二偏置电压,第二偏置电压高于第一偏置电压;(2)向存储器的源极选择线加载第三偏置电压,向存储器的源极线加载第四偏置电压,第四偏置电压高于第三偏置电压。

148.为了后续便于说明,在此先对bl预充电模式、acs预充电模式以及gidl预充电模式这三种预充电模式进行解释说明。

149.(1)bl预充电模式

150.在第一预充电模式中,当第一信号线为位线,第一选择线为漏极选择线时,第一预充电模式即为bl预充电模式,因此bl预充电模式包括:向漏极选择线加载第一导通电压,向位线加载第一预充电电压。

151.也即是,在bl预充电模式中,通过第一导通电压打开第一选择管,并在位线上加载第一预充电电压,以使第一预充电电压通过导通的第一选择管加载到存储串的沟道上。该第一导通电压示例地为3v至5v的一个数值,该第一预充电电压示例地可以为0v至2.2v中的一个数值。

152.对于任一存储串,在打开该存储串的第一选择管之后,如果在该存储串耦合的位线上加载第一预充电电压,第一预充电电压便可驱使该存储串的沟道中的电子移动至位线,从而实现抬高沟道电势的目的,相应地也就抑制了编程干扰的产生。

153.需要说明的是,在本技术实施例中,可以仅仅针对未选择存储串进行预充电。可选地,可以同时对未选择存储串和选择存储串同时进行预充电,本技术实施例对此不做限定。

154.图4是本技术实施例提供的一种bl预充电模式下存储器中各个端口的电压波形图。

155.如图4所示,在预充电阶段时,通过漏极选择线(包括选择dsl和未选择dsl)向所有存储串的第一选择管(tsg)的栅极上加载3v至5v的第一导通电压(图4中标记为v

bias-tsg

),以使各个存储串的第一选择管的漏极和源极能够导通,同时所有存储串的位线(包括编程的

bl和禁止编程的bl)上加载0v至2.2v的第一预充电电压(图4中标记为v

bias-bl

),从而使得加载的第一预充电电压通过导通的第一选择管加载到存储串的沟道,以实现对所有存储串进行预充电的目的。

156.此外,如图4所示,顶部虚设层上也加载电压,该电压比编程的bl和禁止编程的bl上加载的电压大,大概5v左右,用于导通顶部虚设层所对应的晶体管。

157.图4是以对所有存储串进行预充电为例进行说明,可选地,在基于bl预充电模式预充电时,也可以仅仅对未选择存储串进行预充电。

158.图4中的编程阶段的电压波形图的相关解释可以参考图2,在此不再赘述。

159.此外,上述bl预充模式应用于正向编程的场景中。其中,正向编程是从存储器的源极线向存储器的位线的方向进行编程的编程模式。

160.图5是本技术实施例提供的一种正向编程和反向编程的示意图。图5所示的存储串包括自上而下的第一选择管,m个存储单元(图5中将m个存储单元依次连接的字线示例为wl1、wl2、

…

、wlm)和第二选择管,正向编程具体是指从存储串的第二选择管向该存储串的第一选择管的方向依次编程该存储串上的各个存储单元。反向编程是指从该存储串的第一选择管向该存储串的第二选择管的方向依次编程该存储串上的各个存储单元。

161.(2)acs预充电模式

162.在第一预充电模式中,当第一信号线为源极线,第一选择线为源极选择线时,第一预充电模式即为acs预充电模式,因此acs预充电模式包括:向源极选择线加载第二导通电压,向源极线加载第二预充电电压。

163.也即是,在acs预充电模式中,通过第二导通电压打开第二选择管,并在源极选择线加载第二预充电电压,以使第二预充电电压通过导通的第二选择管加载到存储串的沟道上。该第二导通电压示例地为3v至5v的一个数值,该第二预充电电压示例地可以为0v至2.2v中的一个数值。

164.对于任一存储串,在打开该存储串的第二选择管之后,如果在该存储串耦合的源极选择线上加载第二预充电电压之后,该第二预充电电压便可加载到存储串的沟道,使得该存储串的沟道中的电子移动至第二选择管的源极,从而实现抬高沟道电势的目的,相应地也就抑制了编程干扰的产生。

165.图6是本技术实施例提供的一种acs预充电模式下存储器中各个端口的电压波形图。

166.如图6所示,在预充电阶段时,通过源极选择线向所有存储串的第二选择管(bsg)的栅极上加载3v至5v的第二导通电压(图6中标记为v

bias-bsg

),以使各个存储串的第二选择管的漏极和源极能够导通,同时所有存储串的源极线上加载0v至2.2v的第二预充电电压(图6中标记为v

bias-acs

),使得加载的第二预充电电压通过导通的第二选择管加载到存储串的沟道,以实现对所有存储串进行预充电的目的。

167.此外,如图6所示,底部虚设层上也加载电压,该电压和ssl上加载的电压差不多大,大概5v左右,用于导通底部虚设层所对应的晶体管。

168.图6是以对所有存储串进行预充电为例进行说明,可选地,在基于acs预充电模式预充电时,也可以仅仅对未选择存储串进行预充电。

169.图6中加载编程脉冲时(也即编程阶段)各个端口的电压波形图和前述图2中加载

编程脉冲时各个端口的电压波形图一致,在此不再赘述。

170.此外,上述acs预充电模式应用于反向编程的场景中。其中,反向编程是从存储器的位线向存储器的源极线的方向进行编程的编程模式。

171.(3)gidl预充电模式

172.在第二预充电模式中,当第二信号线为位线,第二选择线为漏极选择线时,和/或,当第二信号线为源极线,第二选择线为源极选择线时,第二预充电模式即为gidl预充电模式。因此,其中,gidl预充电模式包括如下两种情况中的至少一种情况:

173.情况一:在第二信号线包括位线的情况下,第二选择线包括存储器的漏极选择线,gidl预充电模式包括:向漏极选择线加载第一偏置电压,向位线加载第二偏置电压,第二偏置电压高于第一偏置电压。也即,在存储器的第一选择管的栅极和漏极分别加载不同的偏置电压,目的在于使得第一选择管处形成高电压差,以使第一选择管中产生gidl电流,

174.情况二:在第二信号线包括源极线的情况下,第二选择线包括存储器的源极选择线,gidl预充电模式包括:向源极选择线加载第三偏置电压,向源极线加载第四偏置电压,第四偏置电压高于第三偏置电压。也即,在存储器的第二选择管的栅极和源极分别加载不同的偏置电压,目的在于使得第二选择管处形成高电压差,以使第二选择管中产生gidl电流。

175.也即是,上述gidl预充电模式可以只在存储串的第一选择管上实现,也可以只在存储串的第二选择管上实现,或者同时在该存储串的第一选择管和第二选择管上实现。

176.图7是本技术实施例提供的一种gidl预充电模式下存储器中各个端口的电压波形图。如图7所示,在预充电阶段时,对于所有存储串(包括选择存储串和未选择存储串)中的任一存储串,在该存储串的位线(bl)上加载第二偏置电压(图7中表示为v

bias-gidl

),在该存储串的漏极选择线(dsl)上加载0v的第一偏置电压vss,以使该存储串的上选择管的栅极接地,从而使得该存储串的第一选择管的栅极和漏极之间形成压差,进而发生栅极和漏极带间隧穿,也即是产生gidl电流,gidl电流中的空穴通过沟道向下传输,以减少沟道中的电子浓度,进而提升沟道电势。同时该存储串的源极线(acs)上加载第四偏置电压(图7中表示为v

bias-gidl

),在该存储串的源极选择线(ssl)上加载0v的第三偏置电压vss,以使第二选择管的栅极接地,从而使得该存储串的第二选择管处也发生带间隧穿,进而产生gidl电流,gidl电流中的空穴通过沟道向下传输,以减少沟道中的电子浓度,进而提升沟道电势。

177.图7是以对所有存储串进行预充电为例进行说明,可选地,在基于acs预充电模式预充电时,也可以仅仅对未选择存储串进行预充电。

178.图7中加载编程脉冲时各个端口的电压波形图和前述图2中加载编程脉冲时各个端口的电压波形图一致,在此不再赘述。

179.需要说明的是,gidl预充电模式可以应用在正向编程中,也可以应用在反向编程中。

180.基于上述对三种预充电模式的说明,示例地,在步骤301中,如果针对存储器中各个字线所耦合的存储单元行的编程操作为正向编程,则第一预充电模式和第二预充电模式可以为bl预充电模式或gidl预充电模式中的一者。如果针对存储器中各个字线所连接的存储单元行的编程操作为反向编程,则第一预充电模式和第二预充电模式可以为acs预充电模式或gidl预充电模式中的一者。

181.基于步骤301和步骤302,便可实现在对某个字线所耦合的存储单元行执行编程操作的过程中,在该编程操作的不同编程阶段之前采用不同的预充电方式进行预充电。不仅提高了预充电的灵活性,还能使得预充电更加适应具体的场景,从而提高预充电在抑制编程干扰上的效果。

182.由于该同一个选择字线耦合的存储单元行中待编程存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态,因此第二编程阶段的编程干扰的严重程度大于第一编程阶段的编程干扰的严重程度。因此本技术实施例需要在第二编程阶段和第一编程阶段采用不同的预充电方式,以实现在编程干扰严重的编程阶段之前进行的预充电效果更优,也即提高第二预充电方式的预充电效果。

183.在一种可能的实现方式中,步骤301中的第一预充电方式和步骤302中的第二预充电方式可以分别采用第一预充电模式和第二预充电模式进行预充电,第一预充电模式和第二预充电模式为不同的预充电模式。如前述内容可知,第一预充电模式包括acs或bl预充电模式,第二预充电模式包括gidl预充电模式。

184.图8是本技术实施例提供的一种gidl预充电模式下的沟道电势示意图,图9是本技术实施例提供的一种acs预充电模式下的沟道电势示意图。如图8和图9所示,gidl预充电模式下的沟道电势明显高于acs预充电模式下的沟道电势。如果预充电后的沟道电势较高,则在后续编程阶段加载的vpass电压无需过高就可以将存储串的沟道电势抬升(boosting)到一个比较高的电势,从而抑制编程干扰。而编程阶段vpass过高,会导致控制栅极加载vpass的存储单元的沟道的电子也可能隧穿,进而产生vpass干扰。因此,通过gidl预充电能够很好的平衡编程阶段产生的编程干扰和vpass干扰。也即是,gidl预充电模式的预充电效果要优于acs或bl预充电模式的预充电效果。

185.可选地,在另一种可能的实现方式中,步骤301中的第一预充电方式和步骤302中的第二预充电方式可以采用相同的预充电模式进行预充电,但是第二预充电方式采用的预充电时长要大于第一预充电方式采用的预充电时长。从而实现第二预充电方式的预充电效果优于第一预充电方式的预充电效果。

186.可以理解的是,预充电时长越长,对存储串的沟道的预充电效果越好。另外,由于该同一个选择字线耦合的存储单元行中待编程存储单元在第二编程阶段后达到的编程态,高于在第一编程阶段后达到的编程态,因此第二编程阶段的编程干扰的严重程度大于第一编程阶段的编程干扰的严重程度。所以在本技术实施例中,通过使得第二预充电方式的预充电时长较长,可以确保能够有效抑制该第二编程阶段产生的较为严重的编程干扰。通过使得第一预充电方式的预充电时长较短,可以在确保有效抑制该第一编程阶段产生的编程干扰的前提下,尽量缩短预充电的时长,进而提升编程效率。

187.也即,在编程后编程态较高的编程阶段(也即高编程态编程阶段)之前,可以对存储串的沟道进行较长时间的预充电,以确保能够有效抑制该编程干扰。而在编程后编程态较低的编程阶段(低编程态编程阶段)之前,则可以对存储串的沟道进行较短时间的预充电,进而可以在确保有效抑制编程干扰的前提下,尽量缩短预充电的时长。其中,该预充电时长的变化范围可以为几微秒至几十微秒。

188.在一种可能的实现方式中,预充电时长可以随着编程后编程态的增大(也即编程干扰的严重程度的增加)而阶梯式增加。也即是,可以将编程后编程态划分为若干档位,每

个档位包括至少一个编程态,且每个档位对应一种预充电时长。相应的,如果在目标编程操作的两个不同编程阶段编程后的编程态不同,但均属于同一档位,则在这两个编程阶段之前进行预充电时的预充电时长可以相同。

189.在另一种可能的实现方式中,预充电时长可以随着编程后编程态的增大而线性增加。也即是,每一个编程态均对应一种预充电时长。相应的,如果在目标编程操作的两个不同编程阶段编程后的编程态不同,在这两个编程阶段之前进行预充电时的预充电时长一定不同。

190.可选地,在另一种可能的实现方式中,在步骤301中的第一预充电方式和步骤302中的第二预充电方式可以分别采用第一预充电模式和第二预充电模式进行预充电,且第一预充电模式包括acs或bl预充电模式,第二预充电模式包括gidl预充电模式的情况下,同样可以将第二预充电方式的预充电时长设置为大于第一预充电方式的预充电时长,这样进一步提高第二预充电方式的预充电效果。

191.此外,上述是以两个编程阶段中采用不同的预充电方式为例进行说明,可选地,在本技术实施例中,还可以在三个编程阶段中采用不同的预充电方式。示例地,在步骤301中的第一预充电方式和步骤302中的第二预充电方式可以分别采用第一预充电模式和第二预充电模式进行预充电,且第一预充电模式和第二预充电模式不同的情况下,在目标编程操作的第三预充电阶段,基于第三预充电方式对存储器进行预充电。

192.其中,第三预充电阶段与目标编程操作的第三编程阶段对应,也即,第二预充电阶段为第三编程阶段之前的预充电阶段。

193.另外,该同一个选择字线耦合的存储单元行中待编程存储单元在第三编程阶段后达到的编程态,高于在参考编程阶段后达到的编程态,参考编程阶段为第一编程阶段或第二编程阶段。因此,第三编程阶段的编程干扰的严重程度,大于参考编程阶段的编程干扰的严重程度,

194.其中,第三预充电方式与参考预充电方式中采用相同的预充电模式,且第三预充电方式的预充电时长大于参考预充电方式的预充电时长,参考预充电方式是在参考编程阶段之前的预充电阶段采用的预充电方式,以实现编程干扰严重程度大的第三编程阶段之前的预充电阶段使用的预充电方式的预充电效果,优于参考编程阶段之前的预充电阶段采用的预充电方式的预充电效果。

195.也即是,在不同的编程阶段中,不同的预充电方式可以组合使用。在此不再一一举例说明。

196.通过上述步骤301和步骤302可以实现在不同编程阶段基于不同的预充电方式对选择字线所耦合的存储单元行进行编程。可选地,在针对该同一个选择字线所耦合的存储单元行进行编程的最开始阶段,由于编程电压还比较低,存储串受到的编程干扰也比较小,因此,这个时间段内可以无需对未选择存储串进行预充电。也即是,在编程操作的第四编程阶段中,不对存储器进行预充电。关于第四编程阶段可以参考前述解释。

197.图10是本技术实施例提供的一种不进行预充电处理时存储器中各个端口的电压波形图。如图10所示,由于不进行预充电,所以在加载编程电压前的预充电阶段,所有端口均加载0v的vss。

198.图10中加载编程脉冲时各个端口的电压波形图和前述图2中加载编程脉冲时各个

端口的电压波形图一致,在此不再赘述。

199.随着针对选择字线所耦合的存储单元行的目标编程操作的进行,编程电压越来越高,选择字线所耦合的禁止编程的存储单元受到的编程干扰也越来越严重,因此,这个时间段可以对存储器进行预充电,以避免产生编程干扰。也即是,在本技术实施例中,在编程操作的前期,可以不对存储器进行预充电,之后在编程操作进行一段时间后,再选择一种预充电方式进行预充电。

200.进一步,在本技术实施例中,在编程操作的前期不进行预充电,在编程操作的中后期,为了提高预充电在抑制编程干扰方面的效果中,在该编程操作的中后期的不同时间段采用不同的预充电方式。不仅提高了预充电的灵活性,还能使得预充电更加适应具体的场景,从而提高预充电在抑制编程干扰上的效果。

201.示例地,在本技术实施例中,在编程操作的最开始阶段,先不对存储器进行预充电。在编程操作进行了一段时间之后,编程电压有所提高,但是编程干扰还不是很严重,此时可以采用acs预充电模式或bl预充电模式。在编程操作的后期,由于编程电压较高使得未选择存储串上的存储单元受到的编程干扰比较严重,此时可以采用gidl预充电模式进行预充电。

202.又示例地,在本技术实施例中,在编程操作的前期,可以不进行预充电,直接在编程操作后期,采用gidl预充电模式进行预充电,从而实现在不同的时间段采用不同的预充电处理方式。

203.又示例地,还可以在编程操作的前期不进行预充电,直接在编程操作的后期采用acs预充电模式或bl预充电模式进行预充电,从而实现在不同的时间段采用不同的预充电处理方式。

204.又示例地,还可以直接在编程操作的前期阶段,采用acs预充电模式或bl预充电模式进行预充电,在编程操作的后期,采用gidl预充电模式进行预充电,从而实现在不同的时间段采用不同的预充电模式。

205.综上,在本技术实施例中,在针对存储器中选择字线所耦合的存储单元行执行目标编程操作时,在目标编程操作的不同编程阶段对应的预充电阶段内,采用不同的预充电方式进行预充电,提高了预充电的灵活性。另外,在高编程态编程阶段和低编程态编程阶段对应的预充电阶段中分别采用不同的预充电方式,从而使得本技术实施例提供的预充电方法更加适应具体的场景,以提高预充电在抑制编程干扰上的效果。

206.上述所有可选技术方案,均可按照任意结合形成本技术的可选实施例,本技术实施例对此不再一一赘述。

207.图11是本技术实施例提供的一种存储系统1100的示意图。如图11所示,该存储系统10包括:一个或多个图1所示的存储器100,以及耦合到存储器100并且被配置为控制存储器100的控制器200。

208.控制器200可以被配置为控制存储器100所执行的操作。比如读取、擦除和编程操作。控制器200还可以被配置为管理关于存储在或要存储在存储器100中的数据的各种功能,包括但不限于坏块管理、垃圾收集、逻辑地址到物理地址的转换、损耗均衡等。可选地,控制器200还可以被配置为处理关于从存储器100读取的或者被写入到存储器100的数据的纠错码(error correcting code,ecc)。控制器200还可以执行任何其他合适的功能。比如,

格式化存储器100。

209.控制器200还可以根据特定通信协议与外部设备通信。示例地,控制器200可以通过各种接口协议中的至少一种与外部设备通信。接口协议可以为通用串行总线(universal serial bus,usb)协议、多媒体卡(multi-media card,mmc)协议、外围部件互连(peripheral component interconnect,pci)协议、pci高速(pci-e)协议、高级技术附件(advanced technology attachment,ata)协议、串行ata协议、并行ata协议、小型计算机小型接口(small computer system interface,scsi)协议、增强型小型磁盘接口(enhanced small drive interface,esdi)协议、集成驱动电子设备(integrated development environment,ide)协议、火线(fire wire)协议等。

210.在一些实施例中,控制器200,以及一个或多个存储器100可以集成到各种类型的电子设备中。该电子设备可以是移动电话、台式计算机、膝上型计算机、平板计算机、车辆计算机、游戏控制台、打印机、定位设备、可穿戴电子设备、智能传感器、虚拟现实(virtual reality,vr)设备、增强现实(augmented reality,ar)设备或者其中具有储存器的任何其他合适的电子设备。这种场景下,如图11所示,存储系统10还包括主机300。控制器200耦合到主机300。控制器200可以管理存储在存储器100中的数据,并且与主机300通信,以实现前述电子设备的功能。

211.在另一些实施例中,控制器200,以及一个或多个存储器100可以集成到各种类型的存储设备中。

212.作为一种示例,如图12所示,控制器200和单个存储器100可以集成到存储卡400中。存储卡400可以包括个人计算机存储器卡国际协会(pcmcia,pc)卡、紧凑闪存(compact flash,cf)卡、智能媒体(smart media,sm)卡、存储器棒、多媒体卡(multi-media card,mmc)、超小型mmc(rs-mmc)、微型mmc(micro-mmc)、安全数码(secure digital,sd)卡、通用闪存存储(universal flash storage,ufs)等。如图12所示,存储卡400还可以包括将存储卡400与主机耦合的连接器410。

213.作为另一种示例,如图13所示,控制器200和多个存储器100可以集成到固态驱动器(solid state disk,ssd)500中。固态驱动器500还可以包括将固态驱动器500与主机耦合的连接器510。其中,固态驱动器500的存储容量和/或操作速度大于存储卡400的存储容量和/或操作速度。

214.此外,存储器100可以是本技术实施例涉及的任何存储器。比如,可以是3d nand(与非门)存储器。

215.如前述图1至图10所示的内容可知,本技术实施例提供的存储器100包括:

216.存储阵列,存储阵列包括多个存储单元行;

217.多个字线,多个字线分别耦合到多个存储单元行;

218.外围电路,外围电路耦合到多个字线并且被配置为对多个存储单元行中的选择存储单元行执行编程操作,选择存储单元行为选择字线所耦合的存储单元行,其中,为了执行编程操作,外围电路被配置为执行本技术实施例提供的编程方法。

219.关于存储器100的其他结构的相关解释说明可以参考图1相应的内容,在此不再赘述。

220.图14是本技术实施例提供的一种图1中的存储串110的截面示意图。如图14所示,

存储串110可以在衬底101上方垂直地延伸并穿过堆叠层102。衬底101可以包括硅(比如,单晶硅)、硅锗(sige)、砷化镓(gaas)、锗(ge)、绝缘体上硅(soi)、绝缘体上锗(goi)或者任何其他合适的材料。

221.堆叠层102可以包括交替的栅极导电层103和栅极到栅极电介质层104。堆叠层102中的栅极导电层103和栅极到栅极电介质层104的成对数量可以确定存储阵列中的存储单元的数量。

222.栅极导电层103可以包括导电材料,导电材料包括但不限于钨(w)、钴(co)、铜(cu)、铝(al)、多晶硅、掺杂硅、硅化物或其任何组合。在一些实施例中,每个栅极导电层103包括金属层,比如,钨层。在另一些实施例中,每个栅极导电层103包括掺杂多晶硅层。此外,每个栅极导电层103可以包括围绕存储单元的控制栅极,并且可以在堆叠层102的顶部处横向地延伸作为dsg线、在堆叠层102的底部处横向地延伸作为ssg线、或者在dsg线与ssg线之间横向地延伸作为字线。

223.如图14所示,存储串110包括垂直地延伸并穿过堆叠层102的沟道结构105。在一些实施例中,沟道结构105包括填充有(一种或多种)半导体材料(比如,作为半导体沟道106)和(一种或多种)电介质材料(比如,作为存储膜107)的沟道孔。半导体沟道106包括硅,比如多晶硅。存储膜107是包括隧穿层108、存储层109(又称为“电荷捕获/存储层”)和阻挡层1010的复合电介质层。

224.在一些实施例中,沟道结构105具有圆柱形状(比如,柱形状)。半导体沟道106、隧穿层108、存储层109和阻挡层1010以此顺序从圆柱的中心朝向圆柱的外表面径向布置。隧穿层108可以包括氧化硅、氮氧化硅或其任何组合。存储层109可以包括氮化硅、氮氧化硅或其任何组合。阻挡层1010可以包括氧化硅、氮氧化硅、高介电常数(高k)电介质或其任何组合。作为一种示例,存储膜107可以是包括氧化硅/氮氧化硅/氧化硅(ono)的复合层。

225.在一些实施例中,如图14所示,衬底101具有阱414(比如,p阱和/或n阱),存储串110的源极端与阱414接触。比如,源极线可以耦合到阱414,以在擦除操作期间将擦除电压加载到阱414(即,存储串的源极)。

226.在一些实施例中,存储串110还包括在存储串的漏极端处的沟道插塞416。

227.应当理解,尽管在图14中未示出,存储阵列还可以包括其他的附加部件,附加部件包括但不限于栅极线缝隙/源极触点、局部触点、互连层等。

228.此外,在本技术实施例中,外围电路可以通过位线、字线、源极线、ssg线和dsg线耦合到存储阵列。外围电路可以包括任何合适的模拟、数字以及混合信号电路,以用于通过经由位线、字线、源极线、ssg线和dsg线将电压信号和/或电流信号加载到存储单元以及从存储单元感测电压信号和/或电流信号来促进存储阵列的操作。

229.外围电路可以包括使用金属-氧化物-半导体(mos)技术形成的各种类型的外围电路。比如,图15示出了一些示例性外围电路,外围电路包括页缓冲器/感测放大器131、列解码器/位线(bl)驱动器132、行解码器/字线(wl)驱动器133、电压发生器134、控制逻辑单元135、寄存器136、接口137和数据总线138。应当理解,在一些示例中,还可以包括图15中未示出的附加外围电路。

230.页缓冲器/感测放大器131可以被配置为根据来自控制逻辑单元135的控制信号从存储阵列读取数据以及向存储阵列编程(写入)数据。比如,页缓冲器/感测放大器131可以

存储要被编程到存储阵列的一个页中的一页编程数据(写入数据)。页缓冲器/感测放大器131还可以执行验证操作,以确保数据已经被正确地编程到选择字线耦合的存储单元中。页缓冲器/感测放大器131还可以感测来自位线的低功率信号,该低功率信号表示存储在存储单元中的数据位,并且在读取操作中将小电压摆幅放大到可识别的逻辑电平。

231.列解码器/位线驱动器132可以被配置为由控制逻辑单元135控制,并且通过加载从电压发生器134生成的位线电压来选择一个或多个存储串。

232.行解码器/字线驱动器133可以被配置为由控制逻辑单元135控制,并且选择/取消选择存储阵列的块,并且选择/取消选择块的字线。行解码器/字线驱动器133还可以被配置为使用从电压发生器134生成的字线电压(vwl)来驱动字线。在一些实施例中,行解码器/字线驱动器133还可以选择/取消选择并且驱动ssg线和dsg线。如下文详细描述的,行解码器/字线驱动器133被配置为对耦合到(一个或多个)选择字线的存储单元执行擦除操作。

233.电压发生器134可以被配置为由控制逻辑单元135控制,并且生成要被供应到存储阵列的字线电压(比如,读取电压、编程电压、通过电压、局部电压、验证电压等)、位线电压和源极线电压。

234.控制逻辑单元135可以耦合到上文描述的外围电路中的各个电路,并且被配置为控制各个电路的操作。

235.寄存器136可以耦合到控制逻辑单元135,寄存器可以包括状态寄存器、命令寄存器和地址寄存器,以用于存储用于控制外围电路中每个电路的操作的状态信息、命令操作码(op码)和命令地址。

236.接口(i/f)137可以耦合到控制逻辑单元135,并且充当控制缓冲器,以缓冲从主机(未示出)接收的控制命令并且并将其中继到控制逻辑单元135,以及缓冲从控制逻辑单元135接收的状态信息并且将其中继到主机。接口137还可以经由数据总线138耦合到列解码器/位线驱动器132,并且充当数据i/o接口和数据缓冲器,以缓冲数据,并且将其中继到存储阵列或从存储阵列中继或缓冲数据。

237.以上存储器相关硬件实施例的描述,具有同上述方法实施例相似的有益效果。对于存储器相关硬件实施例中未披露的技术细节,请参照本技术方法实施例的描述而理解。

238.在本技术实施例中,术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。可以理解地,“第一”、“第二”等在允许的情况下可以互换特定的顺序或先后次序,以使这里描述的本技术实施例能够以除了在这里图示或描述的以外的顺序实施。

239.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

240.以上所述仅为本技术实施例的较佳实施例,并不用以限制本技术实施例,凡在本技术实施例的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。