1.本公开涉及用于通过改进连续时间三角积分adc(∑-δadc,西格玛德尔塔adc)中的dac输出稳定速度来提高连续时间三角积分adc的性能的技术。

背景技术:

2.三角积分调制(∑-δ调制)是用于将模拟信号编码为用于模数转换器(adc)的数字信号的有用技术。三角积分adc(∑-δadc,西格玛德尔塔adc)包括与延迟相关联的反馈环路,所述延迟被称为额外环路延迟(eld),其中eld可以基于许多因素,例如adc量化器的再生时间、从反馈环路中的量化器到数模转换器(dac)的传播延迟,以及dac自身的延迟。eld可以例如在高速adc应用中影响总体adc性能。为了减小eld的影响,三角积分adc可以被配置成具有额外环路延迟(eld)数模转换器(dac)。然而,一些eld dac可能对与三角积分adc相关联的(例如,求和节点上的)寄生电容敏感,且此寄生电容可能会引起eld反馈信息的不完全稳定。另外或可替换的是,寄生电容可能会在三角积分adc的环路滤波器路径中引起寄生极点。这些问题可能会降低三角积分adc的性能,且在一些实施例中,可能会导致三角积分adc不稳定。

技术实现要素:

3.根据一个方面,描述了用于三角积分调制的设备。所述设备可以包括:包括电流数模转换器(idac)的反馈路径;以及与所述idac并联耦合的第一电容器。

4.在一些实施例中,所述idac包括与所述idac并联耦合的第二电容器。

5.在一些实施例中,所述idac包括电流舵eld dac。

6.在一些实施例中,一组电容器包括与所述idac并联耦合的至少两个前馈电容器。在一些实施例中,第一前馈电容器的输入和输出耦合到所述idac的第一输入和第一输出。在一些实施例中,第二前馈电容器的输入和输出耦合到所述idac的第二输入和第二输出。

7.在一些实施例中,第一跨导单元(gm单元)耦合到所述idac,其中所述第一gm单元的第一输出和第二输出耦合到所述idac的第一输出和第二输出。在一些实施例中,所述设备可以包括耦合到所述第一gm单元的第二gm单元,其中所述第二gm单元的第一输出和第二输出耦合到所述第一gm单元的第一输出和第二输出。

8.在一些实施例中,所述设备可以包括锁存器,所述锁存器耦合到所述idac、所述第一gm单元、所述第二gm单元或dac转换器或上述元件的组合。

9.在一些实施例中,所述第二gm单元被配置成补偿与和所述设备相关联的三角积分调制器的一个或多个寄生电容相关联的相移。

10.在一些实施例中,所述设备可以包括耦合到所述第一gm单元的环路滤波器。

11.在一些实施例中,所述设备可以包括耦合到所述第一跨导单元的第二idac,其中所述第二idac的第一输出和第二输出耦合到所述第一gm单元的第一输出和第二输出。在一些实施例中,所述第二idac被配置成接收参考代码并提供参考电流信号。

12.在一些实施例中,所述第一gm单元的传递函数包括用于补偿相移的零。

13.在一些实施例中,第一电容器的电容值基于与所述电流模数转换器相关联的寄生电容。

14.根据另一方面,描述了一种三角积分adc。所述三角积分adc可以包括多个eld dac补偿环路,每一eld dac补偿环路包括idac,以及与所述idac并联耦合的至少两个电容器。

15.在一些实施例中,所述至少两个电容器中的每一电容器的电容值基于与所述三角积分adc相关联的寄生电容。

16.在一些实施例中,所述三角积分adc可以包括耦合到所述idac的第一gm单元以及耦合到所述第一gm单元的第二gm单元。

17.在一些实施例中,每一eld dac补偿环路包括耦合到所述三角积分模数转换器的锁存器的一位比较器,或耦合到所述三角积分模数转换器的多个锁存器的多位比较器。

18.在一些实施例中,所述至少两个电容器为与所述idac并联耦合的前馈电容器。

19.根据另一方面,描述了一种用于装置处的三角积分调制的方法。所述方法可以包括:经由所述装置的idac接收信号;使用与所述装置的所述idac并联耦合的一组电容器,基于与所述装置的连续时间三角积分adc相关联的补偿寄生电容而生成eld反馈信息;以及输出所生成的eld反馈信息。

附图说明

20.通过参考附图,可以更好地理解本公开,并且使本公开的众多特征和优点对本领域的技术人员来说显而易见。在不同的附图中使用相同的附图标记指示类似或相同的物件。

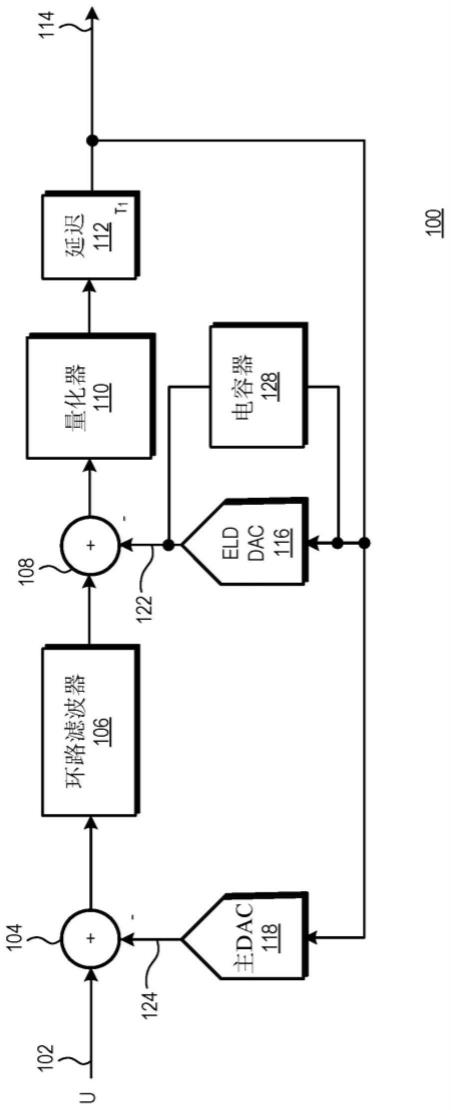

21.图1为根据一些实施例的连续时间三角积分adc的框图。

22.图2为根据一些实施例的连续时间三角积分adc的框图。

23.图3为根据一些实施例的连续时间三角积分adc的框图。

24.图4为根据一些实施例的连续时间三角积分adc的框图。

25.图5为根据一些实施例的连续时间三角积分adc的框图。

26.图6为根据一些实施例的连续时间三角积分adc的框图。

27.图7为根据一些实施例的连续时间三角积分adc的框图。

具体实施方式

28.本公开的各种方面涉及用于通过改进连续时间三角积分adc中的dac输出稳定速度来提高连续时间三角积分adc的性能的技术。在其它例子中,三角积分adc可以被配置成具有eld dac以缓解由于额外环路延迟而产生的问题。然而,eld dac可能会受与三角积分adc相关联的(例如,求和节点上的)寄生电容的影响。例如,寄生电容可能会引起eld反馈信息的不完全稳定。另外,寄生电容可能会在三角积分adc的环路滤波器路径中引起寄生极点。另外或可替换的是,可以在一些连续时间三角积分adc的量化器的输入处采用求和节点以进行系统级优化。然而,在一些情况下,这一求和节点可能会限制连续时间三角积分adc的性能。为了解决上述问题,本公开的各方面涉及包括与电流舵eld dac并联的前馈电容器的连续时间三角积分adc,并且通过在gm单元的传递函数中创建零,恢复了eld反馈环路稳

定和(通过环路滤波器的)主反馈环路传递函数两者。因此,可以实现所述连续时间三角积分adc的性能和稳定性。另外,求和节点可以使连续时间三角积分adc的架构设计变得灵活。

29.图1为根据一些实施例的连续时间三角积分adc(∑-δadc,西格玛德尔塔adc)100的框图。在连续时间三角积分adc 100的以下描述中,可以从连续时间三角积分adc 100添加或省略某些组件。连续时间三角积分adc 100可以通过在连续时间三角积分adc 100的一个或多个组件上处理信号来支持信号的模数转换。在图1的例子中,连续时间三角积分adc 100的组件可以包括但不限于一组求和节点(例如,求和节点104、求和节点108)、环路滤波器106、与对应延迟112相关联的量化器110、eld dac 116和主dac 118。

30.一组求和节点(例如,求和节点104、求和节点108)可以被配置成将连续时间三角积分adc 100的信号相加或相减。环路滤波器106、量化器110、eld dac 116和主dac 118可以被配置成对连续时间三角积分adc 100的信号进行处理(例如,滤波、放大、转换、反馈等)。环路滤波器106、量化器110、eld dac 116和主dac 118可以由一个或多个电路元件(例如,一个或多个电阻器、电容器、电感器等)构成。连续时间三角积分adc 100还可以包括电容器128(例如,一个或多个电容器),其可以被配置成对连续时间三角积分adc 100的寄生电容进行抵消、补偿、减少等操作。

31.连续时间三角积分adc 100的组件可(例如,以操作方式、以通信方式、以功能性方式、以电子方式)彼此耦合。连续时间三角积分adc 100的组件可以包括用于耦合到连续时间三角积分adc 100的其它组件的一个或多个输入和一个或多个输出。求和节点104可以包括一个或多个输入,例如用以接收信号(例如,输入信号102)的第一输入以及耦合到主dac 118的输出以从主dac 118接收另一信号(例如,主dac反馈信号124)的第二输入。求和节点104还可以包括耦合到环路滤波器106的输入以将信号输出到环路滤波器106的输出。

32.求和节点108可以包括耦合到环路滤波器106的输出的第一输入,以及耦合到eld dac 116的输出以接收另一信号(例如,eld dac反馈信号122)的第二输入。量化器110可以包括例如耦合到求和节点108的输出以从求和节点108接收信号的输入。量化器110还可以包括耦合到延迟112的输入以将信号输出到延迟112的输出,所述延迟112可以包括一个或多个输出,所述一个或多个输出包括用以提供输出信号114的第一输出以及耦合到eld dac 116的输入以将信号输出到eld dac 116且耦合到主dac 118的输入以将信号输出到主dac 118的第二输出。

33.在图1的例子中,求和节点104可以经由第一输入接收可以为模拟信号的输入信号102。求和节点104还可以经由第二输入从主dac 118的输出接收主dac反馈信号124。求和节点104可以被配置成将信号相加或相减,例如将主dac反馈信号124与输入信号102相加或相减,以产生所得信号。求和节点104可以经由求和节点104的输出将所得信号提供到环路滤波器106的输入。环路滤波器106可以由一个或多个电路元件构成。例如,环路滤波器106可以由一个或多个电阻器和电容器构成。环路滤波器106还可以与对连续时间三角积分adc 100建模的相应传递函数相关联。

34.环路滤波器106可以经由环路滤波器106的输出将滤波后信号提供到求和节点108的第一输入。求和节点108还可以经由第二输入从eld dac 116的输出接收eld dac反馈信号122。求和节点108可以被配置成将信号相加或相减,例如将eld dac反馈信号122与滤波后信号相加或相减,以产生所得信号。求和节点108可以经由求和节点108的输出将所得信

号提供到量化器110的输入。量化器110可以将环路滤波器106的模拟输出转换成数字代码。例如,从求和节点108输出的模拟信号可以输入到量化器110(例如,多位量化器)且可以是到与量化器110相关联的延迟112的输入(τ1为量化器110的延迟112)。延迟112的输出可以是连续时间三角积分adc 100的输出信号114。

35.连续时间三角积分adc 100包括反馈环路,所述反馈环路包括环路滤波器106、量化器110、eld dac 116和主dac 118。在采样速率高达数ghz的非常高速的三角积分adc中,可能无法忽略反馈环路中的延迟。为了维持连续时间三角积分adc 100的稳定性且为了恢复到最佳性能,需要改进的eld补偿技术。通过建立从量化器110的输出经过eld dac 116到量化器110的输入的直接反馈环路来补偿eld。在一些实施例中,可能需要量化器110的输入处的求和节点108来优化环路滤波器106的内部节点处的热噪声。在一些其它实施例中,可能需要量化器110的输入处的求和节点108来优化信号传递函数。在其它实施例中,前馈环路滤波器架构可能需要在量化器110的输入处的求和节点108。电容器128(即,前馈电容器)可以与eld dac 116并联耦合以改进eld dac 116的输出稳定速度且恢复到如本文中所描述的最佳性能。

36.图2为根据一些实施例的连续时间三角积分adc 200的框图。在连续时间三角积分adc 200的以下描述中,可以从连续时间三角积分adc 200添加或省略某些组件。连续时间三角积分adc 200可以实施如图1所描述的连续时间三角积分adc 100的各方面。例如,连续时间三角积分adc 200可以实施1位量化。连续时间三角积分adc 200可以通过在连续时间三角积分adc 200的一个或多个组件上处理信号来支持信号的模数转换。

37.在图2的例子中,连续时间三角积分adc 200的组件可以包括但不限于求和节点(例如,求和节点202)、环路滤波器204、gm单元206、锁存器210、电流舵eld dac(idac)212和主dac 214。求和节点202可以被配置成将连续时间三角积分adc 200的信号相加或相减。环路滤波器204、gm单元206、锁存器210、idac 212和主dac 214可以被配置成处理连续时间三角积分adc 200的信号。环路滤波器204、gm单元206、锁存器210、idac 212和主dac 214可以由一个或多个电路元件(例如,一个或多个电阻器、电容器、电感器等)构成。

38.连续时间三角积分adc 200的组件可(例如,以操作方式、以通信方式、以功能性方式、以电子方式)彼此耦合。连续时间三角积分adc 200的组件可以包括用于耦合到连续时间三角积分adc 200的其它组件的一个或多个输入和一个或多个输出。求和节点202可以包括一个或多个输入,例如用以接收信号(例如,输入信号u)的第一输入以及耦合到主dac 214的输出以从主dac 214接收另一信号(例如,主dac反馈信号)的第二输入。求和节点202还可以包括耦合到环路滤波器204的输入的输出,所述环路滤波器204可以包括一组输出,所述一组输出包括耦合到gm单元206的第一输入的第一输出和耦合到gm单元206的第二输入的第二输出。gm单元206可以包括一组输入和一组输出。例如,gm单元206可以包括耦合到锁存器210的第一输入的第一输出,而gm单元206的第二输出可以耦合到锁存器210的第二输入。锁存器210可以包括一组输出,所述一组输出包括可用以提供输出信号(例如,数字信号)的第一输出和第二输出。

39.在一些实施例中,锁存器210的第一输出可以耦合到idac 212的第一输入,且锁存器210的第二输出可以耦合到idac 212的第二输入。idac 212可以包括耦合到gm单元206的第一输出的第一输出和耦合到gm单元206的第二输出的第二输出。idac 212可以将eld dac

反馈信号输出到gm单元206的第一输出和耦合到gm单元206的第二输出的第二输出。在一些实施例中,锁存器210的第一输出可以耦合到主dac 214的第一输入,且锁存器210的第二输出可以耦合到主dac 214的第二输入。主dac 214可以经由主dac 214的输出将主dac反馈信号输出到求和节点202的第二输入。

40.在图2的例子中,连续时间三角积分adc 200可以包括与idac 212并联的第一前馈电容器c

ff

218和第二前馈电容器c

ff

220。也就是说,前馈电容器c

ff 218、220添加在idac 212的输入节点与输出节点之间以增强来自idac 212的eld反馈信息的稳定。前馈电容器c

ff 218、220的电容值可以是预配置的。可替换的是,前馈电容器c

ff 218、220的电容值可以基于与连续时间三角积分adc 200相关联的寄生电容。在一些实施例中,在图2的例子中,连续时间三角积分adc 200可以包括在gm单元的传递函数中具有零的零构建gm单元(例如,gm单元206)。零构建gm单元可以补偿由寄生电容c

p 216和gm单元206引起的寄生极点的相移。因此,由eld路径和环路滤波器路径两者上的寄生电容c

p

216引起的问题得到补偿。

41.图3为根据一些实施例的连续时间三角积分adc 300的框图。在连续时间三角积分adc 300的以下描述中,可以从连续时间三角积分adc 300添加或省略某些组件。连续时间三角积分adc 300可以实施如图1所描述的连续时间三角积分adc 100的各方面。例如,连续时间三角积分adc 300可以实施多位量化。连续时间三角积分adc 300可以通过在连续时间三角积分adc 300的一个或多个组件上处理信号来支持信号的模数转换。在图3的例子中,连续时间三角积分adc 300的组件可以包括但不限于求和节点(例如,求和节点302)、环路滤波器304、gm单元306、锁存器310、idac 312、主dac 314和idac 322。求和节点302可以被配置成将连续时间三角积分adc 300的信号相加或相减。环路滤波器304、gm单元306、锁存器310、idac 312、主dac 314和idac 322可以由一个或多个电路元件(例如,一个或多个电阻器、电容器、电感器等)构成。

42.连续时间三角积分adc 300的组件可(例如,以操作方式、以通信方式、以功能性方式、以电子方式)彼此耦合。连续时间三角积分adc 300的组件可以包括用于耦合到连续时间三角积分adc 300的其它组件的一个或多个输入和一个或多个输出。求和节点302可以包括一个或多个输入,例如用以接收信号(例如,输入信号u)的第一输入以及耦合到主dac 314的输出以从主dac 314接收另一信号(例如,主dac反馈信号)的第二输入。求和节点302还可以包括耦合到环路滤波器304的输入的输出,所述环路滤波器304可以包括一组输出,所述一组输出包括耦合到gm单元306的第一输入的第一输出和耦合到gm单元306的第二输入的第二输出。gm单元306可以包括一组输出。例如,gm单元306可以包括耦合到锁存器310的第一输入的第一输出,而gm单元306的第二输出可以耦合到锁存器310的第二输入。锁存器310可以包括一组输出,所述一组输出包括可用以输出输出信号(例如,数字信号)的第一输出和第二输出。

43.在一些实施例中,锁存器310的第一输出可以耦合到idac 312的第一输入,且锁存器310的第二输出可以耦合到idac312的第二输入。idac 312可以包括耦合到gm单元306的第一输出的第一输出和耦合到gm单元306的第二输出的第二输出。idac 312可以将eld dac反馈信号输出到gm单元306的第一输出和耦合到gm单元306的第二输出的第二输出。在一些实施例中,锁存器310的第一输出可以耦合到主dac 314的第一输入,且锁存器310的第二输出可以耦合到主dac 314的第二输入。

44.主dac 314可以经由主dac 314的输出将主dac反馈信号输出到求和节点302的第二输入。idac 322可以包括用以接收参考电流代码的输入。参考电流代码可以对应于参考电流。参考电流可以被设计成对于连续时间三角积分adc 300的每一切片具有相同的共模电流。idac 322可以包括耦合到gm单元306的第一输出的第一输出以及耦合到gm单元306的第二输出以接收参考代码且提供参考电流信号的第二输出。

45.在图3的例子中,连续时间三角积分adc 300可以包括与idac 312并联的第一前馈电容器c

ff 318和第二前馈电容器c

ff 320。前馈电容器c

ff 318、320由此添加在idac 312的输入节点与输出节点之间以增强来自idac 312的eld反馈信息的稳定。在一些实施例中,在图3的例子中,连续时间三角积分adc 300可以包括在gm单元的传递函数中具有零的零构建gm单元(例如,gm单元306)。零构建gm单元可以补偿由寄生电容c

p 316和gm单元306引起的寄生极点的相移。因此,由eld路径和环路滤波器路径两者上的寄生电容c

p 316引起的问题得到补偿。

46.图4为根据一些实施例的连续时间三角积分adc 400的框图。在连续时间三角积分adc 400的以下描述中,可以从连续时间三角积分adc 400添加或省略某些组件。连续时间三角积分adc 400可以通过在连续时间三角积分adc 400的一个或多个组件上处理信号来支持信号的模数转换。在图4的例子中,连续时间三角积分adc 400的组件可以包括但不限于一组求和节点(例如,求和节点404、求和节点408)、环路滤波器406、与对应延迟412相关联的量化器410、eld dac 416、主dac 418和放大器420。一组求和节点(例如,求和节点404、求和节点408)可以被配置成将连续时间三角积分adc 400的信号相加或相减。环路滤波器406、量化器410、eld dac 416、主dac 418和放大器420可以被配置成对连续时间三角积分adc400的信号进行处理(例如,滤波、放大、转换、反馈等)。环路滤波器406、量化器410、eld dac 416、主dac 418和放大器420可以由一个或多个电路元件(例如,一个或多个电阻器、电容器、电感器等)构成。电容器428可以被配置成对连续时间三角积分adc 400的寄生电容进行抵消、补偿、减少等操作。

47.连续时间三角积分adc 400的组件可(例如,以操作方式、以通信方式、以功能性方式、以电子方式)彼此耦合。连续时间三角积分adc 400的组件可以包括用于耦合到连续时间三角积分adc 400的其它组件的一个或多个输入和一个或多个输出。求和节点404可以包括一个或多个输入,例如用以接收信号(例如,输入信号402)的第一输入以及耦合到主dac 418的输出以从主dac 418接收另一信号(例如,主dac反馈信号424)的第二输入。求和节点404还可以包括耦合到环路滤波器406的输入以将信号输出到环路滤波器406的输出。

48.求和节点408可以包括耦合到环路滤波器406的输出的第一输入、耦合到eld dac 416的输出以接收另一信号(例如,eld dac反馈信号422)的第二输入,以及耦合到放大器420的输出的第三输入。放大器420可以包括用以接收信号(例如,输入信号426)的输入。输入信号426(信号x)可以等于三角积分adc输入402(信号u),或环路滤波器406的内部信号。量化器410可以包括例如耦合到求和节点408的输出以从求和节点408接收信号的输入。量化器410还可以包括耦合到延迟412的输入以将信号输出到延迟412的输出,所述延迟412可以包括一个或多个输出,所述一个或多个输出包括用以提供输出信号414的第一输出以及耦合到eld dac 416的输入以将信号输出到eld dac 416且耦合到主dac 418的输入以将信号输出到主dac 418的第二输出。

49.在图4的例子中,求和节点404可以经由第一输入接收可以为模拟信号的输入信号402。求和节点404还可以经由第二输入从主dac 418的输出接收主dac反馈信号424。求和节点404可以被配置成将信号相加或相减,例如将主dac反馈信号424与输入信号402相加或相减,以产生所得信号。求和节点404可以经由求和节点404的输出将所得信号提供到环路滤波器406的输入。环路滤波器406可以由一个或多个电路元件构成。例如,环路滤波器406可以由一个或多个电阻器和电容器构成。环路滤波器406还可以与对连续时间三角积分adc 400建模的相应传递函数相关联。

50.环路滤波器406可以经由环路滤波器406的输出将滤波后信号提供到求和节点408的第一输入。求和节点408还可以经由第二输入从eld dac 416的输出接收eld dac反馈信号422。求和节点408可以被配置成将信号相加或相减,例如将eld dac反馈信号422或来自放大器420的放大信号与滤波后信号相加或相减,以产生所得信号。求和节点408可以经由求和节点408的输出将所得信号提供到量化器410的输入。量化器410可以将环路滤波器406的模拟输出转换成数字代码。例如,从求和节点408输出的模拟信号可以输入到量化器410(例如,多位量化器)且可以是到与量化器410相关联的延迟412的输入(τ1为量化器410的延迟412)。延迟412的输出可以是连续时间三角积分adc 400的输出信号414。

51.连续时间三角积分adc 400包括反馈环路,所述反馈环路包括环路滤波器406、量化器410、eld dac 416和主dac 418。在采样速率高达数ghz的非常高速的三角积分adc中,可能无法忽略反馈环路中的延迟。为了维持连续时间三角积分adc 400的稳定性且为了恢复到最佳性能,需要改进的eld补偿技术。通过建立从量化器410的输出经过eld dac 416到量化器410的输入的直接反馈环路来补偿eld。在一些实施例中,可能需要量化器410的输入处的求和节点408来优化环路滤波器406的内部节点处的热噪声。在一些其它实施例中,可能需要量化器410的输入处的求和节点408来优化信号传递函数。在其它实施例中,前馈环路滤波器架构可能需要在量化器410的输入处的求和节点408。电容器428可以与eld dac 416并联耦合,以改进eld dac 416的输出稳定速度且恢复到如本文中所描述的最佳性能。在一些实施例中,如本文中所描述,求和节点408可以实施为图5中的电流求和。在一些实施例中,如本文中所描述,求和节点408可以实施为图6中的电流求和。

52.图5为根据一些实施例的连续时间三角积分adc 500的框图。在连续时间三角积分adc 500的以下描述中,可以从连续时间三角积分adc 500添加或省略某些组件。连续时间三角积分adc 500可以实施如图4所描述的连续时间三角积分adc 400的各方面。例如,连续时间三角积分adc 500可以实施1位量化。连续时间三角积分adc 500可以实施通用求和节点和用于1位量化的eld补偿技术。

53.连续时间三角积分adc 500可以通过在连续时间三角积分adc 500的一个或多个组件上处理信号来支持信号的模数转换。在图5的例子中,连续时间三角积分adc 500的组件可以包括但不限于求和节点(例如,求和节点502)、环路滤波器504、gm单元506、gm单元508、锁存器510、电流舵eld dac(idac)512和主dac 514。求和节点502可以被配置成将连续时间三角积分adc 500的信号相加或相减。环路滤波器504、gm单元506、gm单元508、锁存器510、idac 512和主dac 514可以被配置成处理连续时间三角积分adc 500的信号。环路滤波器504、gm单元506、gm单元508、锁存器510、idac 512和主dac 514可以由一个或多个电路元件(例如,一个或多个电阻器、电容器、电感器等)构成。

54.连续时间三角积分adc 500的组件可(例如,以操作方式、以通信方式、以功能性方式、以电子方式)彼此耦合。连续时间三角积分adc 500的组件可以包括用于耦合到连续时间三角积分adc 500的其它组件的一个或多个输入和一个或多个输出。求和节点502可以包括一个或多个输入,例如用以接收信号(例如,输入信号u)的第一输入以及耦合到主dac 514的输出以从主dac 514接收另一信号(例如,主dac反馈信号)的第二输入。求和节点502还可以包括耦合到环路滤波器504的输入的输出,所述环路滤波器504可以包括一组输出,所述一组输出包括耦合到gm单元506的第一输入的第一输出和耦合到gm单元506的第二输入的第二输出。

55.gm单元508可以包括一组输入和一组输出。例如,gm单元508可以包括可用以接收输入信号(例如,输入信号x)的第一输入和第二输入,以及耦合到gm单元506的第一输出和gm单元506的第二输出的第一输出和第二输出。gm单元506的第一输出可以耦合到锁存器510的第一输入,而gm单元506的第二输出可以耦合到锁存器510的第二输入。锁存器510可以包括一组输出,所述一组输出包括可用以提供输出信号(例如,数字信号)的第一输出和第二输出。

56.在一些实施例中,锁存器510的第一输出可以耦合到idac 512的第一输入,且锁存器510的第二输出可以耦合到idac 512的第二输入。idac 512可以包括耦合到gm单元506的第一输出的第一输出和耦合到gm单元506的第二输出的第二输出。idac 512可以将eld dac反馈信号输出到gm单元506的第一输出和耦合到gm单元506的第二输出的第二输出。在一些实施例中,锁存器510的第一输出可以耦合到主dac 514的第一输入,且锁存器510的第二输出可以耦合到主dac 514的第二输入。主dac 514可以经由主dac 514的输出将主dac反馈信号输出到求和节点502的第二输入。

57.在图5的例子中,连续时间三角积分adc 500可以包括与idac 512并联的第一前馈电容器c

ff 518和第二前馈电容器c

ff 520。也就是说,前馈电容器c

ff 518、520添加在idac 512的输入节点与输出节点之间以增强来自idac 512的eld反馈信息的稳定。前馈电容器c

ff 518、520的电容值可以是预配置的。可替换的是,前馈电容器c

ff 518、520的电容值可以基于与连续时间三角积分adc 500相关联的寄生电容。在一些实施例中,在图5的例子中,连续时间三角积分adc 500可以包括在gm单元的传递函数中具有零的零构建gm单元(例如,gm单元506或gm单元508)。零构建gm单元可以补偿由寄生电容cp 516和gm单元506、508引起的寄生极点的相移。因此,由eld路径和环路滤波器路径两者上的寄生电容c

p 516引起的问题得到补偿。

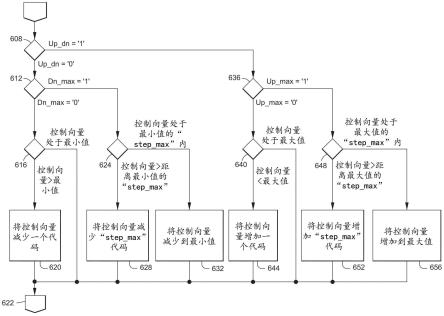

58.图6为根据一些实施例的连续时间三角积分adc 600的框图。在连续时间三角积分adc 600的以下描述中,可以从连续时间三角积分adc 600添加或省略某些组件。连续时间三角积分adc 600可以实施如图4所描述的连续时间三角积分adc 400的各方面。例如,连续时间三角积分adc 600可以实施多位量化。连续时间三角积分adc 600可以实施通用求和节点和用于多位量化的eld补偿技术。连续时间三角积分adc 600可以因此包括多个切片。

59.连续时间三角积分adc 600可以通过在连续时间三角积分adc 600的一个或多个组件上处理信号来支持信号的模数转换。在图6的例子中,连续时间三角积分adc 600的组件可以包括但不限于求和节点(例如,求和节点602)、环路滤波器604、gm单元606、gm单元608、锁存器610、idac 612、主dac 614和idac 622。求和节点602可以被配置成将连续时间

三角积分adc 600的信号相加或相减。环路滤波器604、gm单元606、gm单元608、锁存器610、idac 612、主dac 614和idac 622可以由一个或多个电路元件(例如,一个或多个电阻器、电容器、电感器等)构成。

60.连续时间三角积分adc 600的组件可(例如,以操作方式、以通信方式、以功能性方式、以电子方式)彼此耦合。连续时间三角积分adc 600的组件可以包括用于耦合到连续时间三角积分adc 600的其它组件的一个或多个输入和一个或多个输出。求和节点602可以包括一个或多个输入,例如用以接收信号(例如,输入信号u)的第一输入以及耦合到主dac 614的输出以从主dac 614接收另一信号(例如,主dac反馈信号)的第二输入。求和节点602还可以包括耦合到环路滤波器604的输入的输出,所述环路滤波器604可以包括一组输出,所述一组输出包括耦合到gm单元606的第一输入的第一输出和耦合到gm单元606的第二输入的第二输出。

61.gm单元608可以包括一组输入和一组输出。例如,gm单元608可以包括可用以接收输入信号(例如,输入信号x)的第一输入和第二输入,以及耦合到gm单元606的第一输出和gm单元606的第二输出的第一输出和第二输出。gm单元606的第一输出可以耦合到锁存器610的第一输入,而gm单元606的第二输出可以耦合到锁存器610的第二输入。锁存器610可以包括一组输出,所述一组输出包括可用以输出输出信号(例如,数字信号)的第一输出和第二输出。

62.在一些实施例中,锁存器610的第一输出可以耦合到idac 612的第一输入,且锁存器610的第二输出可以耦合到idac 612的第二输入。idac 612可以包括耦合到gm单元606的第一输出的第一输出和耦合到gm单元606的第二输出的第二输出。idac 612可以将eld dac反馈信号输出到gm单元606的第一输出和耦合到gm单元606的第二输出的第二输出。在一些实施例中,锁存器610的第一输出可以耦合到主dac 614的第一输入,且锁存器610的第二输出可以耦合到主dac 614的第二输入。主dac 614可以经由主dac 614的输出将主dac反馈信号输出到求和节点602的第二输入。idac 622可以包括用以接收参考电流代码的输入。参考电流代码可以对应于参考电流。参考电流可以被设计成对于连续时间三角积分adc 600的每一切片具有相同的共模电流。idac 622可以包括耦合到gm单元606的第一输出的第一输出以及耦合到gm单元606的第二输出以接收参考代码且提供参考电流信号的第二输出。

63.在图6的例子中,连续时间三角积分adc 600可以包括与idac 612并联的第一前馈电容器c

ff 618和第二前馈电容器c

ff 620。前馈电容器c

ff 618、620由此添加在idac 612的输入节点与输出节点之间以增强来自idac 612的eld反馈信息的稳定。在一些实施例中,在图6的例子中,连续时间三角积分adc 600可以包括在gm单元的传递函数中具有零的第二零构建gm单元(例如,gm单元606或gm单元608)。零构建gm单元可以补偿由寄生电容c

p 616和gm单元606、608引起的寄生极点的相移。因此,由eld路径和环路滤波器路径两者上的寄生电容c

p 616引起的问题得到补偿。

64.图7为根据一些实施例的连续时间三角积分adc 700的晶体管级实施方案的框图。在连续时间三角积分adc 700的以下描述中,可以从连续时间三角积分adc 700添加或省略某些组件。连续时间三角积分adc 700可以实施如图6所描述的连续时间三角积分adc 600的各方面。例如,连续时间三角积分adc 700可以实施多位量化。连续时间三角积分adc 700可以实施通用求和节点和用于多位量化的eld补偿技术。连续时间三角积分adc 700可以因

此包括多个切片。

65.环路滤波器702可以具有差分电压输出vi

和vi-。这些差分电压信号可以利用源退化跨导(gm)级转换成差分电流信号。源退化gm级可以由两个pmos晶体管704(即,m1和m2)、两个电流源706(即,i

s1

)、源退化电阻器708(即,r

s1

)和电容器710(即,c

s1

)构成。添加电容710(即,c

s1

)可以在gm级的传递函数中提供零,且补偿由寄生电容712(即,c

p

)引起的相移。电流源706(即,i

s1

)可以例如实施为级联pmos电流源。两个pmos晶体管714(即,m

13

和m

14

)、两个电流源716(即,i

s2

)、源退化电阻器718(即,r

s2

)和电容器720(即,c

s2

)可以构成另一具有零的gm级。输入信号722(例如,信号x)可以转换成电流信号且添加在求和节点760、762中。此输入信号722可以为连续时间三角积分adc 700的输入信号726(例如,信号u),或环路滤波器702中的内部信号。

66.nmos晶体管728(即,nmos晶体管m

5-m6)和电流源730(即,i

ref,u

)构成参考电流736。参考电流736可以被设计成对于每一切片732具有相同的共模电流。对于每一切片732,差分参考电流信号可以不同。切片732中的eld dac为(n 1)级电流舵dac,其由nmos晶体管738(即,m

3-m4)和电流源740(即,i

dac,u

)构成。eld dac 734可以类似方式实施为参考电流736,但其开关可由(n 1)级比较器的数字输出控制。

67.参考电流736和eld dac 734中的电流源可以例如实施为级联nmos电流源。在每一1位电流舵dac中,添加两个前馈电容器742(即,c

ff

)。一个电容器742(即,c

ff

)可以添加在d-与i

o

之间,而另一电容器742(即,c

ff

)可以添加在d

与i

o-之间。

68.在图3的例子中,i

o-节点连接到sum

节点,而io

节点连接到sum-节点。sum

节点和sum-节点是用于gm输出电流、eld dac输出电流734和参考电流736的求和节点。也就是说,这些输出同时是锁存器块744的输入。锁存器块744的输出可以由采样和保持(s&h)电路746(包括路径门748(即,m

7-m8))利用采样时钟750(即,clk

sh

)进行采样。此后,所采样的量化器输出经过由晶体管754-1和754-2(即,m

9-m

12

)构成的两个缓冲器752。第一缓冲器可以由晶体管754-1(即,m

9-m

10

)构成,由此为具有pmos负载的nmos缓冲器。第二缓冲器可以由晶体管754-2(即,m

11-m

12

)构成,由此为cmos缓冲器(例如,cmos反相器)。第二缓冲器输出d

、d-可以为连续时间三角积分adc 700的数字输出v,且还驱动主dac 756和eld dac 734。

69.如图7所示,在重复的求和节点和1位比较器的这些n个切片732中,仅参考电流sp[1]、

…

、sp[n-1]和sn[1]、

…

、sn[n-1]的控制位是不同的。但是具有零的gm单元、具有前馈电容器的eld dac、锁存器块、s&h电路和缓冲器对于这些n个切片来说是相同的。

[0070]

在一些实施例中,可通过执行软件的处理系统的一个或多个处理器来实施上文所描述的技术的某些方面。软件包括存储或以其它方式有形地体现在非暂时性计算机可读存储介质上的一组或多组可执行指令。软件可以包括指令和某些数据,所述指令和数据在由一个或多个处理器执行时,操控一个或多个处理器以执行上文所描述的技术的一个或多个方面。非暂时性计算机可读存储介质可以包括例如磁盘或光盘存储装置、例如快闪存储器的固态存储装置、高速缓冲存储器、随机存取存储器(ram)或其它非易失性存储器装置等。存储在非暂时性计算机可读存储介质上的可执行指令可以呈源代码、汇编语言代码、目标代码的形式,或呈可通过一个或多个处理器解译或以其它方式执行的其它指令格式的形式。

[0071]

计算机可读存储介质可以包括在使用期间可由计算机系统存取以将指令和/或数

据提供到计算机系统的任何存储介质或存储介质的组合。此类存储介质可以包括但不限于,光学介质(例如,压缩光盘(cd)、数字多功能光盘(dvd)、蓝光光盘)、磁性介质(例如,软盘、磁带,或磁性硬盘驱动器)、易失性存储器(例如,随机存取存储器(ram)或高速缓冲存储器)、非易失性存储器(例如,只读存储器(rom)或快闪存储器),或基于微机电系统(mems)的存储介质。计算机可读存储介质可以嵌入在计算系统(例如,系统ram或rom)中、以固定方式附接到计算系统(例如,磁性硬盘驱动器)、以可移除方式附接到计算系统(例如,光学光盘或基于通用串行总线(usb)的快闪存储器),或经由有线或无线网络(例如,网络可存取存储装置(nas))耦合到计算机系统。

[0072]

应注意,上文在总体描述中所描述的活动或元素并非全部是需要的,可能不需要特定活动或装置的一部分,且除所描述的那些活动或元素以外,可以执行一个或多个另外的活动或包括一个或多个另外的元素。又另外,所列的活动次序未必是执行活动的次序。并且,已经参考特定实施例描述了概念。然而,本领域的技术人员应了解,可以在不脱离如以下权利要求书中所阐述的本公开的范围的情况下进行各种修改和改变。尽管在图1-图7中作为例子示出了前馈sdm架构,但本公开还可以用于例如反馈架构的其它sdm架构以及混合的前馈-反馈架构。尽管在图1-图7中作为例子示出了单个环路sdm架构,但本公开还可以用于其它sdm架构,例如多级噪声整形(mash)架构。因此,说明书和图应被认为是说明性的而非限制性的,并且希望所有此类修改都包括在本公开的范围内。

[0073]

上文已关于特定实施例描述了益处、其它优点和对问题的解决方案。然而,这些益处、优点、对问题的解决方案以及可能使任何益处、优点或解决方案发生或变得更明显的任何特征不应被理解为任何或所有权利要求的重要、必要或基本的特征。此外,上文公开的特定实施例仅是说明性的,这是因为所公开的主题可以不同但等效的方式修改和实践,这对于受益于本文中的教示的本领域技术人员来说是显而易见的。除如所附权利要求书中所描述的以外,并不意图限制本文所示的构造或设计的细节。因此,显而易见的是,可以更改或修改上文公开的特定实施例,并且所有此类变化被视为在所公开的主题的范围内。因此,本文寻求的保护如在所附权利要求中阐述。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。