1.根据本公开的实施方案的一个或多个方面涉及封装,并且更确切来说涉及一种包括铜柱和环氧模塑化合物的集成电路封装。

背景技术:

2.被通孔延伸穿过的半导体管芯(诸如具有硅穿孔的硅管芯)可由于形成所述穿孔的工艺而很薄。在一些实施方案中,所述管芯约200微米厚,并且因此其可能相对脆,例如容易破裂或碎裂。

3.因此,需要封装来保护薄的半导体管芯,同时使得可形成到管芯的一个或两个表面的电连接。

技术实现要素:

4.根据本发明的实施方案,提供一种封装,所述封装具有顶表面和底表面,且包括:半导体管芯,所述半导体管芯具有前表面、后表面和多个边缘;模塑化合物,所述模塑化合物位于所述管芯的所述后表面上;多个第一导电元件,所述多个第一导电元件穿过在所述管芯的所述后表面上的所述模塑化合物延伸到所述封装的所述顶表面;以及多个第二导电元件,所述多个第二导电元件位于所述封装的所述底表面上。

5.在一些实施方案中,所述模塑化合物还位于所述管芯的所述边缘上。

6.在一些实施方案中,所述半导体管芯是硅管芯,并且所述模塑化合物是环氧模塑化合物。

7.在一些实施方案中,所述半导体管芯包括多个通孔,所述多个通孔从所述管芯的所述前表面延伸到所述管芯的所述后表面。

8.在一些实施方案中,所述半导体管芯包括位于所述管芯的所述前表面上的多个晶体管。

9.在一些实施方案中,所述封装还包括位于所述管芯的所述前表面上的第一再分布层。

10.在一些实施方案中,所述第一再分布层不延伸通过所述管芯的所述多个边缘中的第一边缘。

11.在一些实施方案中,所述封装还包括位于所述管芯的所述后表面上的第二再分布层。

12.在一些实施方案中:所述第一导电元件中的每一者是直径为至少100微米并且高度为至少50微米的铜柱,相邻第一导电元件之间的距离为至少300微米,所述第二导电元件中的每一者是直径为最多50微米并且高度为最多50微米的铜杆凸块,并且相邻第二导电元件之间的距离为最多120微米。

13.在一些实施方案中,所述封装还包括:第一再分布层,所述第一再分布层位于所述管芯的所述前表面上;以及第二再分布层,所述第二再分布层位于所述管芯的所述后表面

上,其中所述第二导电元件中的每一者通过所述第一再分布层并且通过所述通孔连接到所述管芯的所述前表面。

14.在一些实施方案中:所述半导体管芯包括位于所述半导体管芯的所述前表面上的跨阻抗放大器;并且所述跨阻抗放大器具有:输入端,所述输入端通过所述第一再分布层连接到所述多个第二导电元件中的一个导电元件;以及输出端,所述输出端通过所述第一再分布层、通过所述多个通孔中的一个通孔并且通过所述第二再分布层连接到所述多个第一导电元件中的一个导电元件。

15.在一些实施方案中:所述半导体管芯包括位于所述半导体管芯的所述前表面上的调制器驱动器,所述调制器驱动器具有:输入端,所述输入端通过所述第一再分布层、通过所述多个通孔中的一个通孔并且通过所述第二再分布层连接到所述多个第一导电元件中的一个导电元件;以及输入端,所述输入端通过所述第一再分布层连接到所述多个第二导电元件中的一个导电元件。

16.在一些实施方案中,所述方法还包括:在半导体晶片的表面上形成多个导电柱,所述半导体晶片具有前表面和后表面,所述导电柱形成在所述半导体晶片的所述后表面上;切割所述半导体晶片以形成多个半导体管芯,所述半导体管芯中的每一者具有与所述半导体晶片的所述前表面对应的前表面、与所述半导体晶片的所述后表面对应的后表面以及多个边缘;将模塑化合物施加到所述半导体管芯,所述施加包括使用所述模塑化合物来覆盖所述半导体管芯中的每一者的所述后表面;研磨所述模塑化合物以露出所述导电柱;以及在所述半导体管芯中的每一者的所述前表面上形成多个导电杆凸块。

17.在一些实施方案中,所述模塑化合物的所述施加还包括使用所述模塑化合物来覆盖所述半导体管芯中的每一者的所述边缘。

18.在一些实施方案中,所述导电柱是铜柱,并且所述导电杆凸块是铜杆凸块。

19.在一些实施方案中,所述半导体管芯中的每一者是具有多个硅穿孔的硅管芯,所述多个硅穿孔各自从所述半导体管芯的所述前表面延伸到所述半导体管芯的所述后表面。

20.在一些实施方案中,所述方法还包括在所述多个导电杆凸块的所述形成之前在所述半导体晶片的所述前表面上形成第一再分布层,其中所述多个导电杆凸块的所述形成包括直接在所述第一再分布层上形成所述多个导电杆凸块。

21.在一些实施方案中,所述方法还包括在所述导电柱的所述形成之前在所述半导体晶片的所述后表面上形成第二再分布层,其中所述导电柱的所述形成包括直接在所述第二再分布层上形成所述导电柱。

附图说明

22.参考说明书、权利要求书和附图将了解和理解本公开的这些和其他特征和优点,在附图中:图1a是根据本公开的实施方案的集成电路封装的剖视图;图1b是图1a的一部分的放大图;图2a是根据本公开的实施方案的用于制作集成电路封装的工艺中的中间产品的剖视图;图2b是图2a的一部分的放大图;

图3a是根据本公开的实施方案的用于制作集成电路封装的工艺中的中间产品的剖视图;图3b是图3a的一部分的放大图;图4a是根据本公开的实施方案的用于制作集成电路封装的工艺中的中间产品的剖视图;图4b是图4a的一部分的放大图;图5a是根据本公开的实施方案的集成电路封装的剖视图;图5b是图5a的一部分的放大图;图6a是根据本公开的实施方案的用于制作集成电路封装的工艺中的位于载体上的中间产品的剖视图;图6b是根据本公开的实施方案的用于制作集成电路封装的工艺中的位于载体上的中间产品的剖视图;图6c是根据本公开的实施方案的集成电路封装的剖视图;且图7是根据本公开的实施方案的采用图1a及图1b的集成电路封装的系统的立体图。

具体实施方式

23.下文结合附图所述的详细描述旨在作为对根据本公开所提供的集成电路封装的例示性实施方案的描述,并不旨在表示可构造或利用本公开的唯一形式。所述描述结合所说明的实施方案来阐述本公开的特征。然而,应理解,相同或等效的功能和结构可由也旨在囊括在本公开的范围内的不同实施方案来实现。如本文中别处所述,相似的元件编号旨在指示相似的元件或特征。

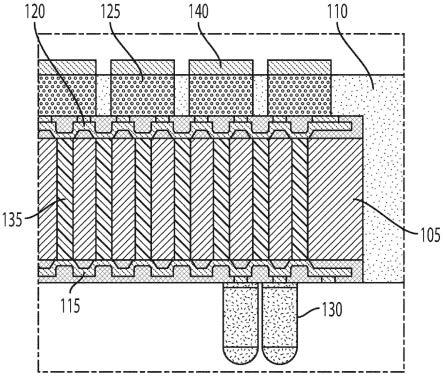

24.参考图1a及图1b(图1b是图1a的一部分的放大图),在一些实施方案中,集成电路封装包括硅管芯105,所述硅管芯105在数个侧面上被模塑化合物(例如,环氧模塑化合物(emc))110包封。在图1a及图1b的定向中,硅管芯105的前表面(上面可在铸造厂制作有有源组件(例如晶体管))是硅管芯105的底表面,且顶表面是后表面。第一再分布层115(或“前侧rdl”)固定到硅管芯105的所述前表面且第二再分布层120(或“后侧rdl”)固定到硅管芯105的后表面。

25.多个第一导电元件(例如,铜柱125)穿过位于硅管芯105的后表面上的环氧模塑化合物110层而形成到第二再分布层120的外部连接。铜柱可被定位成具有至少300微米的中心到中心距离(例如,其可定位在间距为至少300微米的栅格上),且每一个铜柱可具有约200微米的直径(例如,在100微米与1000微米之间的直径)和至少50微米的高度(例如,约100微米的高度)。钝化层(例如,聚酰亚胺钝化层)可存在于第二再分布层120上;可使用穿过所述钝化层的通孔(例如,10微米直径的通孔)来形成穿过钝化层的在第二再分布层120与铜柱125之间的连接。多个第二导电元件(例如,铜杆凸块130)形成到第一再分布层115的外部连接。铜杆凸块可被定位成具有120微米或更小的中心到中心距离(例如,其可定位在间距为最多120微米的栅格上),并且每一个铜杆凸块可具有最多50微米的直径和最多50微米的高度。硅管芯105可包括多个硅穿孔(tsv)135,所述多个硅穿孔(tsv)135形成(i)硅管芯105的前表面和第一再分布层115与(ii)硅管芯105的后表面和第二再分布层120之间的

导电路径。

26.在一些实施方案中,在硅管芯105的周边外侧不形成外部连接,并且第一再分布层115和第二再分布层120中的每一者的每一个边缘可与硅管芯105的对应边缘齐平(如图1b中所示),或硅管芯105可略微延伸超出第一再分布层115和第二再分布层120中的一者或两者的边缘,或第一再分布层115和第二再分布层120中的一者或另一者或两者可略微(例如,小于500微米或小于100微米)延伸超出硅管芯105的边缘。

27.第三再分布层(图1a及图1b中未示出)可形成在集成电路封装的顶表面上,即形成在位于硅管芯105的后表面上的环氧模塑化合物110层上。表面饰面140可形成在第三再分布层(如果存在)和铜柱125的外端上(即,在图1a及图1b的定向中,形成在上端上)。此表面饰面例如可以是(i)镍/金、(ii)无电镍浸金(enig)、或(iii)无电镍、无电钯和浸金(enepig)。所述表面饰面可提供适合于用作搭接栅格阵列的导电接垫,例如以达成到另一集成电路的连接(下文更详细地论述)。

28.(i)硅管芯105的后表面上的环氧模塑化合物110层和(ii)铜柱125的存在可减小到硅管芯105的后表面的连接将损坏硅管芯105的风险。举例来说,在一些实施方案中,另一集成电路(例如,cmos分组交换asic)可在其下表面上具有导体阵列(例如,搭接栅格阵列),所述另一集成电路可在操作中安装在集成电路封装的顶表面上,并且可例如使用包括可压缩导电元件145(图1a中出于图解说明目的示出其中的一者)的阵列的插孔来在cmos分组交换asic的导体阵列与集成电路封装的铜柱125之间达成多个电连接。与(i)位于硅管芯105的后表面上的环氧模塑化合物110层和(ii)铜柱125不存在时由可压缩导电元件145中的每一者施加到硅管芯105的压缩力(和任何剪切力)将分布的面积相比,在存在(i)位于硅管芯105的后表面上的环氧模塑化合物110层和(ii)铜柱125时所述力可分布在硅管芯105的更大面积之上。

29.除了覆盖硅管芯105的后表面之外,环氧模塑化合物110还可覆盖硅管芯105的边缘(即侧表面)。硅管芯105的边缘上存在的环氧模塑化合物110可保护硅管芯105不碎裂。在一些实施方案中,每一个边缘上的环氧模塑化合物110层介于50微米与100微米厚之间。

30.图2a及图2b(图2b是图2a的一部分的放大图)示出可制作为用于制作图1a及图1b的集成电路封装的工艺的一部分的中间产品。图2a及图2b的中间产品可通过首先在铸造厂制作初级硅管芯来制作。初级硅管芯可由硅晶片制作而成,并且初级硅管芯可包括位于其前表面上的结构(例如,晶体管)和从前表面延伸到晶片中达一定深度(例如,约200微米)的通孔(例如,用于形成硅穿孔的盲孔)。可在晶片的前侧上形成第一再分布层115。可将晶片接合到第一载体上,并且可研磨晶片的后侧以露出硅穿孔的端部,以使得在研磨晶片的后侧之后,硅穿孔135一直延伸穿过晶片。接着,可在晶片的后侧上形成第二再分布层120。在一些实施方案中,硅穿孔是在通过研磨将晶片薄化之后形成。

31.图3a及图3b(图3b是图3a的一部分的放大图)示出可由图2a及图2b的中间产品形成的中间产品。可在晶片的后侧上(例如,在第二再分布层120上)形成铜柱125(例如,藉由镀覆),且可将晶片从第一载体剥离。在工艺的此点处,如果将在另一工厂执行其余制作步骤,则晶片可呈适合于包装并运输到另一工厂的形式。

32.图4a及图4b(图4b是图4a的一部分的放大图)示出可由图3a及图3b的中间产品形成的中间产品。可对晶片进行切割并将所得的管芯再次安置到第二载体上,并且使用环氧

模塑化合物110来进行包覆模塑。接着,可研磨包覆模塑的中间产品的后侧以露出(即,暴露出)铜柱125的端部,并且如果第三再分布层是集成电路封装的一部分,则可在位于硅管芯105的后表面上的环氧模塑化合物110层的顶表面上形成第三再分布层(未示出)。接着,可在第三再分布层(如果存在)上并且在铜柱125的外端上形成表面饰面140。图4a及图4b的视图是为了仅示出一个封装而绘制,但在与图4a及图4b对应的制作步骤处,可通过环氧模塑化合物110将多个管芯接合在一起。

33.图5a及图5b(图5b是图5a的一部分的放大图)示出可由图4a及图4b的中间产品形成的集成电路封装。可将图4a及图4b的中间产品从第二载体剥离,并且可将中间产品的后侧接合到第三载体。可在此步骤处在硅管芯的前侧上形成额外(例如,第四)再分布层(或者如果在先前制作步骤中未形成第一再分布层115,则可在此步骤处形成),并且可在前侧再分布层上(例如,如果第一再分布层115和第四再分布层两者皆存在,则在第一再分布层115上或在第四再分布层上)形成铜杆凸块130。可例如在两个或三个步骤中形成铜杆凸块130,所述两个或三个步骤包括:沉积铜(例如,镀覆)的步骤;在铜上沉积镍的任选步骤;以及在(i)镍(如果存在)上或者如果镍不存在则在(ii)铜上沉积锡银合金的步骤。接着,可将中间产品从第三载体剥离,进行切割(例如,在环氧模塑化合物110位于相邻管芯之间的条带处分割开)、包装并运输。

34.图6a示出在第二载体610上的图4a及图4b的中间产品,图6b示出在从第二载体610剥离并接合到第三载体620之后的此中间产品,并且图6c示出在一些实施方案中的最终产品。为了易于图解说明,图6a及图6b仅示出包封在环氧模塑化合物110中的两个管芯;然而,在一些实施方案中,此中间产品中存在更大数目个管芯。

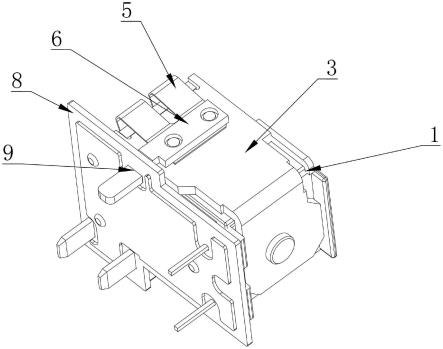

35.图7示出在一些实施方案中的采用集成电路封装705的系统。集成电路封装705安装在光子集成电路(pic)710上,所述光子集成电路继而安装在光学引擎载体715上。铜柱125中的每一者的上表面形成搭接栅格阵列的导电表面720(例如,藉由表面饰面140形成)以形成与一个或多个其他组件(例如,cmos分组交换asic(未示出),如上文所论述)的接触。pic 710可包括v形凹槽和模式转换器,所述模式转换器用于将光纤725对准到pic 710并且用于对pic 710执行光纤的光学本征模式与光波导(例如,3微米的肋状波导或条带波导)的本征模式之间的模式转换。pic还可包括光电子装置(诸如,光电检测器)和用于将光学信号(例如,调幅光)转换成电信号(且反之亦然)的光学调制器,所述光学调制器连接到光波导。所述光电子装置的电端子可通过pic上的导电迹线连接到集成电路封装705的铜杆凸块130。每一个集成电路封装705的硅管芯105的前表面上的结构可包括晶体管电路,例如将光电子装置介接到例如cmos分组交换asic的接口电路(例如,用于放大来自光电检测器的信号电路(诸如跨阻抗放大器)和用于驱动调制器的调制器驱动器)。在所述实施方案中,光电子装置可通过铜杆凸块130且通过第一再分布层115连接到接口电路,并且接口电路可通过第一再分布层115、通过硅穿孔125、通过第二再分布层120且通过铜柱125连接到cmos分组交换asic。

36.如本文中所使用,“铜柱”是按重量计含有至少50%铜的柱。如本文中所使用,“铜杆凸块”是按重量计含有至少50%铜的杆凸块。如本文中所使用,措词“或”是包含性的,以使得例如“a或b”意指(i)a、(ii)b以及(iii)a和b中的任一者。

37.将理解,当元件或层被称为“位于另一元件或层上”、“形成在另一元件或层上”、“连接到另一元件或层”、“耦合到另一元件或层”或“与另一元件或层相邻”时,所述元件或层可直接位于另一元件或层上,直接形成在另一元件或层上、直接连接到另一元件或层、直接耦合到另一元件或层、或与另一元件或层紧邻,或可存在一个或多个中介性元件或层。相比之下,当元件或层被称为“直接位于另一元件或层上”、“直接形成在另一元件或层上”、“直接连接到另一元件或层”、“直接耦合到另一元件或层”或“与另一元件或层紧邻”时,则不存在中介性元件或层。

38.本文中所引述的任何数值范围旨在包括包含在所引述范围内的具有相同数值精确性的所有子范围。举例来说,“1.0到10.0”或“在1.0与10.0之间”的范围旨在包括在所引述的最小值1.0与所引述的最大值10.0之间(且包括)的所有子范围,即具有等于或大于1.0的最小值和等于或小于10.0的最大值,例如2.4到7.6。本文中所引述的任何最大数值限制旨在包括包含在最大数值限制中的所有较低数值限制,并且本说明书中所引述的任何最小数值限制旨在包括包含在最小数值限制中的所有较高数值限制。

39.尽管本文中已具体地描述和说明了集成电路封装的例示性实施方案,但本领域的技术人员将明白诸多修改和变化。因此,应理解,根据本公开原理的集成电路封装构造可体现为除本文中具体描述之外的形式。本发明也由以下权利要求书及其等效内容限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。