1.本发明涉及半导体存储领域,特别涉及一种半导体存储装置。

背景技术:

2.dram(dynamic random access memory)是通过在构成存储单元的电容器中积蓄电荷以存储信息,当不供给电源时会失去存储的信息的易失性存储器。因为经过一定时间后,积蓄于电容器的电荷会放电,dram必须定期进行所谓充电更新的存储保持动作。

3.此外,到下一次更新进行为止的期间,针对同样的行(row)地址,若集中过多的读取及/或写入请求,便可能发生行捶击(row hammer)问题。行捶击问题,是一定时间内针对同样的行地址集中了过多的存取的情况下,由于对应于与所述行地址物理上邻接的行地址所对应的数据位的电荷放电,导致的数据破坏问题。

4.针对半导体存储装置的读写存取请求的态样以及更新间隔之间的关系之一例如图1所示,假设每经过一定时间(间隔i1)便进行更新。如图1的(a)所示,没有频繁地请求读写存取的情况下,存储器的数据保持特性不会受损。然而,如图1的(b)所示,若频繁地请求读写存取,存储器的数据保持特性会受损(也就是数据位的电荷会放电),数据保持时间会变短。因此,会有发生数据破坏的可能性。

5.为了解决上述行捶击问题,举例而言,可以考虑将存储单元的更新间隔(i1)常态地设定为较短。然而,这种情况下,因为更新变成以较短的间隔频繁地进行,半导体存储装置的耗电量会增大。

6.有鉴于此,本发明提供可以回避由于行捶击问题而导致的数据破坏,且抑制耗电增大的半导体存储装置。

技术实现要素:

7.为了解决上述课题,本发明提供一种半导体存储装置,包括:第一控制部,根据从外部输入的包含于特定指令的有关于存储单元的更新间隔的信息,设定所述存储单元的更新间隔。

8.本发明的半导体存储装置,不仅可以抑制耗电的增大,还可以回避由于行捶击问题导致的数据破坏。

附图说明

9.图1为对公知的半导体存储装置进行读写存取请求的态样与更新间隔之间的关系的一示例。

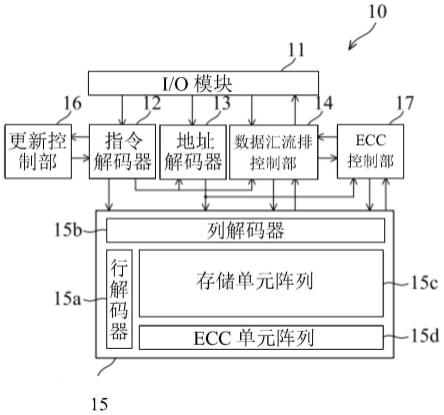

10.图2为关于本发明的第一实施例的半导体存储装置的构成方块图。

11.图3为第一构成暂存器的构成示意图。

12.图4的(a)为更新控制部的构成示例,图4的(b)为除频器的构成示例,图4的(c)为多个模式,每次更新请求信号的时序图。

13.图5为第二构成暂存器的构成示意图。

14.图6为在本实施例的半导体存储装置中,数据控制的一示例的说明图。

15.图7为设定更新间隔时,半导体存储装置的处理的一示例的流程图。

16.图8为关于本发明的第二实施例的半导体存储装置的构成示意图。

17.图9为在本实施例的半导体存储装置中的构成示意图。

18.图10为关于本发明的第三实施例的半导体存储装置的构成示意图。

19.图11为第二构成暂存器的构成示意图。

20.图12为在本实施例的半导体存储装置中,数据控制的一示例的说明图。

21.附图标号:

22.10:半导体存储装置

23.11:i/o模块

24.12:指令解码器

25.13:地址解码器

26.14:数据汇流排控制器

27.15:存储芯片片

28.15a:行解码器

29.15b:列解码器

30.15c:存储单元阵列

31.15d:ecc单元阵列

32.15e:2t2c单元阵列

33.16:更新控制部

34.16a:振荡电路

35.16b:除频器

36.17:ecc控制部

37.17a:错误订正码生成模块

38.17b:错误检测及订正模块

39.18:2t2c控制部

40.sw_a~sw_d:开关模块

41.sw0~sw3:开关模块内的开关

42.sw_modea~sw_moded:模式选择开关

43.s100~s103:流程图步骤

44.bsclk:更新触发信号

45.srefz:更新信号

46.srefz_normal:通常更新信号

47.srefz_modea:模式a下输出的更新信号

48.srefz_modeb:模式b下输出的更新信号

49.srefz_modec:模式c下输出的更新信号

50.srefz_moded:模式d下输出的更新信号

具体实施方式

51.参照图2,关于本实施例的半导体存储装置10,具备i/o(输入输出)模块11;指令解码器12;地址解码器13;数据汇流排控制器14;存储芯片15;更新控制部16;以及ecc(错误修正码)控制部17。半导体存储装置10内的各模块11~17,可以由专用硬件装置或逻辑电路构成。另外,在本实施例中,为了简化说明,不显示例如电源电路、时脉产生器等其他众所周知的构成。

52.关于本实施例的半导体存储装置,可以为dram或被配置以从内部控制更新动作的psram(pseudo-static random access memory)。举例而言,在公知的dram中,设置有通过登录干扰字线地址且追加更新动作将数据回复等,以解决行捶击问题的专用电路。然而,由于psram往小型化迈进,难以像公知的dram可确保在psram中设置专用电路的空间。另外,假设像这样的专用电路设置于psram,psram的成本恐怕会增加。

53.因此,关于本实施例的半导体存储装置为psram时,不设置专用电路,并在抑制耗电增大的同时,可以回避由于行捶击问题导致的数据破坏,是较合适的。

54.i/o模块11,配置为在与外部装置(例如存储体控制器等)之间进行传送、接收信号。具体来说,i/o模块11将从外部装置输入的指令信号输出到指令解码器12。另外,i/o模块11将从外部装置输入的地址信号输出到地址解码器13。更进一步地,i/o模块11将从外部装置输入的数据信号(以下称为“数据”)输出到数据汇流排控制器14,将从数据汇流排控制器14输出的数据输出到外部装置。

55.指令解码器12,解码从外部通过i/o模块11输入的指令信号,生成内部指令。此处,生成的内部指令,举例而言,包括激活信号、读取信号、写入信号、预充电信号等。另外,指令解码器12生成内部指令时,将信号输出到存储芯片15的行解码器15a(详述于后),所述信号用以活化成为读取或写入存取或更新等的对象的字线。更进一步地,指令解码器12生成内部指令时,将信号输出到存储芯片15的列解码器15b(详述于后),所述信号用以活化成为读取或写入存取或更新等的对象的位线。另外,更进一步地,指令解码器12也可以将生成的内部指令输出到地址解码器13以及数据汇流排控制器14,根据内部指令控制各个地址解码器13以及数据汇流排控制器14。

56.另外,在用以设定半导体存储装置10的机能的暂存器写入指令(特定指令)通过外部装置输入i/o模块11时,在显示第一构成暂存器的设定内容的第一构成暂存器信息(如图3所示)被包含于暂存器写入指令的情况下,指令解码器12会将第一构成暂存器信息存储于第一构成暂存器(图示未显示)之中。更进一步地,包含第一构成暂存器信息的暂存器写入指令被输入时,指令解码器12将暂存器写入指令输出到更新控制部16。另外,更进一步地,在每次高位准的更新信号srefz(如图4所示)从更新控制部16输入时,指令解码器12将信号输出到地址解码器13,所述信号显示成为更新对象的存储单元的地址。

57.参照图3,图3显示利用hyperbus

tm

介面的psram的第一构成暂存器(cr0)的一例。第一构成暂存器被配置为使用半导体存储装置10的电力模式或存取协议的动作条件等的定义,可以从外部指定在特定数的位(此例为16bit)内被分配的数种机能(此例为“允许深度断电(deep power down enable)”、“驱动强度”、“更新间隔”、“初期延迟”、“固定延迟”、“混合丛发模式”、“丛发长度”)。另外,由于有关图3所示的“更新间隔”以外的其他机能与本发明没有特别的关系,因此省略详细说明。

58.本实施例中,第一构成暂存器的位11~9被配置为可以指定更新间隔。在图3的示例中,可以指定根据第一构成暂存器的位11~9的数值的多个模式(此例为4个模式“模式a”、“模式b”、“模式c”、及“模式d”)以及通常动作(预设)模式之中的任一模式。此处,各模式皆为本发明中“有关更新间隔的信息”的一例。在图3的示例中,第一构成暂存器位11~9的数值为000b时指定模式a、第一构成暂存器位11~9的数值为001b时指定模式b、第一构成暂存器位11~9的数值为010b时指定模式c、第一构成暂存器位11~9的数值为011b时指定模式d、第一构成暂存器位11~9的数值为111b时指定通常模式。各模式的更新间隔互不相同,在本实施例中,更新间隔的配置以通常模式、模式a、模式b、模式c、模式d的顺序越来越短。

59.举例而言,图3所示第一构成暂存器的内容,可以经由在电源输入半导体存储装置10时,从外部装置输入包含第一构成暂存器信息的暂存器写入指令,写入半导体存储装置10内的第一构成暂存器。另外,在电源输入半导体存储装置10的时间内,包含第一构成暂存器信息的暂存器写入指令可以在任意的时序输入。

60.回到图2,地址解码器13解码通过i/o模块11从外部输入的地址信号,或从指令解码器12输入并显示成为更新对象的存储单元的地址的信号,生成行地址信号,所述行地址信号显示存储芯片15的存储单元阵列15c内的多个字线之中被活性化的字线。接着,地址解码器13将生成的行地址信号输出到存储芯片15的行解码器15a。

61.另外,地址解码器13解码从外部通过i/o模块11输入的地址信号,生成显示存储芯片15的存储单元阵列15c内的多个位线中被活化的位线的列地址信号。接着,地址解码器13将生成的列地址信号输出到存储芯片15的列解码器15b。

62.数据汇流排控制器14,将从外部通过i/o模块11输入的数据,输出到存储芯片15的感应放大器(图示未显示)及ecc控制部17。另外,数据汇流排控制器14将从存储芯片15的感应放大器或ecc控制部17输出的数据输出到i/o模块11。

63.存储芯片15包括:行解码器15a;列解码器15b;存储单元阵列15c;ecc单元阵列15d;以及感应放大器(图示未显示)。

64.行解码器15a在用以活化成为读取或写入存取或更新等的对象的字线的信号从指令解码器12输入时,在存储单元阵列15c内的多个字线之中,经由地址解码器13输出的行地址信号活性化(驱动)显示的字线。

65.列解码器15b在用以活化成为读取或写入存取或更新等的对象的位线的信号从指令解码器12输入时,在存储单元阵列15c内的多个位线之中,经由地址解码器13输出的列地址信号活性化(驱动)显示的位线。

66.存储单元阵列15c,包含行列(阵列)状配置的多个存储单元(图示未显示)。各存储单元中,存储从外部通过i/o模块11输入的数据。各存储单元可以是众所周知的1t1c(1晶体管1电容)型的存储单元。另外,各存储单元可以连接多个字线之中任一者的字线,以及多个位线之中任一者的位线。更进一步地,多个字线各自与行解码器15a连接,多个位线各自与列解码器15b以及感应放大器连接。

67.ecc单元阵列15d与存储单元阵列15c同样地,包含行列状配置的多个存储单元(图示未显示)。各存储单元中,存储从ecc控制部17输出的检查数据(同位数据,parity data)。各存储单元可以是1t1c型的存储单元。另外,各存储单元连接多个字线之中任一者的字线,以及多个位线中任一者的位线。更进一步地,多个字线各自与行解码器15a连接,多个位线

各自与列解码器15b以及感应放大器连接。

68.另外,由于有关存储单元阵列15c以及ecc单元阵列15d的每个存储单元的数据控制细节为众所周知的技术,在此处省略其说明。

69.更新控制部16生成更新信号srefz,输出到指令解码器12。此处,在包含第一构成暂存器信息的暂存器写入指令(特定指令)从指令解码器12输入时,更新控制部16被配置为根据包含于暂存器写入指令的有关存储单元更新间隔的信息,设定存储单元的更新间隔。另外,更新控制部16为本发明中“第一控制部”的一例。

70.另外,更新控制部16也可以在每次从外部输入包含第一构成暂存器信息的暂存器写入指令(特定指令)时,根据包含于暂存器写入指令的有关存储单元更新间隔的信息,设定存储单元的更新间隔。

71.参照图4的(a),更新控制部16具备振荡电路16a以及除频器16b。振荡电路16a以特定频率生成用以开始更新动作的更新触发信号bsclk,输出到除频器16b。

72.除频器16b,将从振荡电路16a输出的更新触发信号bsclk,对应包含于暂存器写入指令的存储单元的更新间隔(此处为模式a、模式b、模式c、模式d中任一模式)进行除频。接着,除频器16b将已除频的信号作为更新信号srefz输出到指令解码器12。另外,此处省略针对通常模式的说明。

73.除频器16b的构成例显示于图4的(b)。如图4的(b)所示,除频器16b具备串联连接的3个t正反器以及4个开关sw_modea、sw_modeb、sw_modec、sw_moded。

74.从振荡电路16a输出的更新触发信号bsclk,输入到三个t正反器之中的第一段t正反器,以及对应4个模式之中的模式d的sw_moded开关的一端。若sw_moded开关开启,会将更新触发信号bsclk作为更新信号srefz输出。

75.从第一段t正反器输出的信号,输入到三个t正反器之中的第二段t正反器,以及对应4个模式之中的模式c的sw_modec开关的一端。若sw_modec开关开启,会将从第一段t正反器输出的信号作为更新信号srefz输出。

76.从第二段t正反器输出的信号,输入到三个t正反器之中的第三段t正反器,以及对应4个模式之中的模式b的sw_modeb开关的一端。若sw_modeb开关开启,会将从第二段t正反器输出的信号作为更新信号srefz输出。

77.从第三段t正反器输出的信号,输入到对应4个模式之中的模式a的sw_modea开关的一端。若sw_modea开关开启,会将从第三段t正反器输出的信号作为更新信号srefz输出。

78.根据所述构成,更新信号srefz的频率,如图4的(c)所示,以模式a、模式b、模式c、模式d的顺序越来越高(也就是更新间隔以模式a、模式b、模式c、模式d的顺序越来越短)。

79.更新控制部16回应包含于暂存器写入指令存储单元的更新间隔,控制除频器16b的各开关sw_modea、sw_modeb、sw_modec、sw_moded之中的任一开关为唯一开启,控制其他开关关闭。举例而言,包含于暂存器写入指令的存储单元的更新间隔为模式a时,控制开关sw_modea开启,控制其他开关sw_modeb、sw_modec、sw_moded关闭。

80.ecc控制部17生成对应从数据汇流排控制器14输出到存储单元阵列15c的数据的错误订正码(编码数据),将生成的错误订正码内的检查数据(同位数据)存储于ecc单元阵列15d。另外,在生成错误订正码的数据从存储单元阵列15c输出(被读取)时,ecc控制部17利用存储于ecc单元阵列15d的检查数据进行所述数据的错误检测及订正处理。接着,ecc控

制部17将错误检测及订正处理后的数据输出到数据汇流排控制器14。

81.另外,在本实施例中,ecc控制部17具备:错误订正码生成模块17a(如图6所示),生成对应存储于存储单元阵列15c的数据的错误订正码(编码数据);以及错误检测及订正模块17b(如图6所示),从存储单元阵列15c读取生成的错误订正码的数据时,进行所述数据的错误检测及订正处理。

82.此处,举例而言,错误订正码的生成以及错误订正处理,可以通过汉明码(hamming code)或bch码(bose-chaudhuri-hocquenghem code)等众所周知的方法进行。另外,成为编码数据的来源数据的长度以及检查数据的长度可以任意选择,此处以编码数据的来源数据的长度为8位,检查数据的长度为4位的情况作为一例进行说明。另外,在此情况下,8位的数据之中的1位进行错误订正。

83.在本实施例中,包含行列(阵列)状配置的多个存储单元的存储单元阵列15c被分割为多个区块时,ecc控制部17被配置为选择多个区块之中任一区块。更进一步地,ecc控制部17将对应存储于被选择的区块内的多个存储单元的数据所生成的错误订正码内的检查数据,存储于ecc单元阵列15d(特定存储区域)。另外,ecc控制部17在本发明中为“第二控制部”的一例。

84.另外,在从外部输入包含第二构成暂存器信息(显示于图5)的暂存器写入指令(特定指令)时,ecc控制部17也可以根据包含于暂存器写入指令的选择区块的信息,选择多个区块之中任一区块。藉此,由于从外部输入暂存器写入指令(特定指令)时,会根据关于包含于所述指令的选择区块的信息,选择多个区块之中任一区块,通过将所述指令从外部装置(例如存储体控制器等)传送到半导体存储装置10,可以从外部设定(选择)多个区块之中任一区块(此处为存储成为错误订正码生成对象的数据的区块)。

85.此处,根据包含于暂存器写入指令的有关选择区块的信息选择任一区块时,指令解码器12通过i/o模块11从外部装置输入包含第二构成暂存器信息的暂存器写入指令(特定指令)时,将第二构成暂存器信息存储于第二构成暂存器(图示未显示)。另外,指令解码器12在包含第二构成暂存器信息的暂存器写入指令输入时,将暂存器写入指令输出到ecc控制部17。

86.图5显示利用hyperbus

tm

介面的psram的第二构成暂存器(cr1)的一例。第二构成暂存器被配置为可以从外部指定在特定数的位(此例为16bit)内被分配的机能(此例为“ecc适用区块控制”)。

87.在本实施例中,在第二构成暂存器的位11~9中被配置为可以指定(选择)ecc适用区块(也就是成为错误订正码生成对象的数据被存储的区块)。在图5所示的例子中,可以根据第二构成暂存器的位11~9的值选择多个(此例为4个)区块之中任一区块。此处,图5所示各区块,系在本发明中“关于选择区块的信息”的一例。图5所示的例子中,第二构成暂存器的位11~9的值为000b时,选择区块n-3(n为3以上的整数);第二构成暂存器的位11~9的值为001b时,选择区块n-2;第二构成暂存器的位11~9的值为010b时,选择区块n-1;第二构成暂存器的位11~9的值为011b时,选择区块n。另外,第二构成暂存器的位11~9的值为111b时,指定通常模式(无选择区块,也就是不选择区块)。

88.举例而言,图5所示的第二构成暂存器的内容,可以在半导体存储装置10电源输入时,通过从外部装置输入包含第二构成暂存器信息的暂存器写入指令,写入半导体存储装

置10内的第二构成暂存器。另外,包含第二构成暂存器信息的暂存器写入指令,也可以在电源输入半导体存储装置10期间的任意时序输入。

89.另外,在图5的示例中,在各个多个区块以及通常模式之中,显示多个开关(在此例为sw0、sw1、sw2、sw3、/sw0、/sw1、/sw2、/sw3)的开关状态。针对上述将参照图6进行说明。

90.参照图6,存储单元阵列15c被分割为行地址连续的多个区块(在此例为区块0、

…

区块n-3、区块n-2、区块n-1、区块n)。在各区块中,数据的存储容量可以相同,也可以不同。举例而言,存储单元阵列15c的存储容量为64m位,各区块的存储容量为2m位的情况下,存储单元阵列15c可以被分割为32个区块。另外,在这个情况下,若成为编码数据的来源数据的长度为8位,检查数据的长度为4位,ecc单元阵列15d的存储容量为1m位。

91.首先,针对于存储单元阵列15c存储数据的情况进行说明。从数据汇流排控制器14输出的数据,输入到存储单元阵列15c的各区块的输入侧。另外,输入到各区块之中被选择的区块(此处为区块n-2)的数据,也会通过开关模块sw_a输入到ecc控制部17的错误订正码生成模块17a。

92.此处,ecc控制部17也可以根据有关于包含于暂存器写入指令的选择区块的信息,选择区块(此处为区块n-2)。另外,ecc控制部17,在数据输入各区块之中的被选择区块(此处为区块n-2)时,也可以控制开关模块sw_a将所述数据输入错误订正码生成模块17a。

93.举例而言,在暂存器写入指令选择区块n-2时,ecc控制部17回应对应区块n-2的各开关的开关状态,控制开关模块sw_a内的各开关。此处,在图6所示的例子中,开关模块sw_a内设有4个开关/sw0、/sw1、/sw2、/sw3。开关模块sw_a的开关/sw0的一端连接区块n-3的输入侧,开关/sw0的另一端连接错误订正码生成模块17a。开关模块sw_a的开关/sw1的一端连接区块n-2的输入侧,开关/sw1的另一端连接错误订正码生成模块17a。开关模块sw_a的开关/sw2的一端连接区块n-1的输入侧,开关/sw2的另一端连接错误订正码生成模块17a。开关模块sw_a的开关/sw3的一端连接区块n的输入侧,开关/sw3的另一端连接错误订正码生成模块17a。

94.另外,在图5的示例中,选择区块n-2时,设定开关/sw1为开启,开关/sw0、/sw2、/sw3为关闭。在此情况下,ecc控制部17控制开关模块sw_a的开关/sw1开启,控制开关模块sw_a的开关/sw0、/sw2、/sw3关闭。藉此,输入到存储单元阵列15c的区块n-2的数据,也会通过开关模块sw_a输入到ecc控制部17的错误订正码生成模块17a。

95.另外,ecc控制部17的错误订正码生成模块17a,在通过开关模块sw_a的开关/sw1将数据输入到被选择区块(此处为区块n-2)时,生成对应所述数据的错误订正码(编码数据),将生成的错误订正码内的检查数据存储于ecc单元阵列15d。

96.接下来,针对从存储单元阵列15c输出数据的情况进行说明。从存储单元阵列15c的各区块之中的被选择区块(此处为区块n-2)以外的其他区块输出的数据,通过开关模块sw_b输入到数据汇流排控制器14。另外,从各区块之中被选择区块(此处为区块n-2)输出的数据,不会通过开关模块sw_b输入到数据汇流排控制器14,而是通过开关模块sw_c输入到ecc控制部17的错误检测及订正模块17b。

97.此处,ecc控制部17,在从各区块之中被选择的区块(此处为区块n-2)输出数据时,也可以将所述数据输入到ecc控制部17的错误检测及订正模块17b以控制开关模块sw_b、sw_c。举例而言,在暂存器写入指令选择区块n-2时,ecc控制部,回应对应区块n-2的各开关

的开关状态,控制开关模块sw_b、sw_c的各开关。此处,在图6的示例中,开关模块sw_b内设有4个开关sw0、sw1、sw2、sw3。开关模块sw_b的开关sw0的一端连接区块n-3的输出侧,开关sw0的另一端连接数据汇流排控制器14。开关模块sw_b的开关sw1的一端连接区块n-2的输出侧,开关sw1的另一端连接数据汇流排控制器14。开关模块sw_b的开关sw2的一端连接区块n-1的输出侧,开关sw2的另一端连接数据汇流排控制器14。开关模块sw_b的开关sw3的一端连接区块n的输出侧,开关sw3的另一端连接数据汇流排控制器14。

98.另外,在图6的示例中,开关模块sw_c内设有4个开关/sw0、/sw1、/sw2、/sw3。开关模块sw_c的开关/sw0的一端连接到区块n-3的输出侧以及开关模块sw_b的开关sw0之间,开关/sw0的另一端连接到错误检测及订正模块17b。开关模块sw_c的开关/sw1的一端连接到区块n-2的输出侧以及开关模块sw_b的开关sw1之间,开关/sw1的另一端连接到错误检测及订正模块17b。开关模块sw_c的开关/sw2的一端连接到区块n-1的输出侧以及开关模块sw_b的开关sw2之间,开关/sw2的另一端连接到错误检测及订正模块17b。开关模块sw_c的开关/sw3的一端连接到区块n的输出侧以及开关模块sw_b的开关sw3之间,开关/sw3的另一端连接到错误检测及订正模块17b。

99.具体而言,在图5中,选择区块n-2时,设定开关/sw1、sw0、sw2、sw3开启,开关/sw0、/sw2、/sw3、sw1关闭。此时,ecc控制部17控制开关模块sw_b的开关sw0、sw2、sw3开启,开关模块sw_b的开关sw1关闭。另外,ecc控制部17控制开关模块sw_c的开关/sw1开启,开关模块sw_c的开关/sw0、/sw2、/sw3关闭。藉此,从存储单元阵列15的区块n-2输出的数据,可以通过开关模块sw_c输入到ecc控制部17的错误检测及订正模块17b。

100.ecc控制部17的错误检测及订正模块17b,在从被选择区块(此处为区块n-2)输出的数据通过开关模块sw_c的开关/sw1输入时,利用存储于ecc单元阵列15d的检查数据,对应输入的数据进行错误检测及订正处理。

101.接着,ecc控制部17也可以控制开关模块sw_d,将错误检测及订正处理后的数据,通过开关模块sw_d输出到数据汇流排控制器14。此处,ecc控制部17,将错误检测及订正处理后的数据,作为从各区块之中被选择的区块(此处为区块n-2)输出的数据输出到数据汇流排控制器14。

102.举例而言,在暂存器输入指令中,区块n-2被选择时,ecc控制部17回应对应区块n-2的各开关的开关状态,控制开关模块sw_d的各开关。此处,在图6的示例中,开关模块sw_d内设有4个开关/sw0、/sw1、/sw2、/sw3。开关模块sw_d的开关/sw0的一端连开关模块sw_b的开关sw0及数据汇流排控制器14之间,开关/sw0的另一端连接错误检测及订正模块17b。开关模块sw_d的开关/sw1的一端连开关模块sw_b的开关sw1及数据汇流排控制器14之间,开关/sw1的另一端连接错误检测及订正模块17b。开关模块sw_d的开关/sw2的一端连开关模块sw_b的开关sw2及数据汇流排控制器14之间,开关/sw2的另一端连接错误检测及订正模块17b。开关模块sw_d的开关/sw3的一端连开关模块sw_b的开关sw3及数据汇流排控制器14之间,开关/sw3的另一端连接错误检测及订正模块17b。

103.另外,在图5的示例中,区块n-2被选择时,开关被设定为/sw1为开启,开关/sw0、/sw2、/sw3为关闭。此时,ecc控制部17控制开关模块sw_d的开关/sw1开启,控制开关模块sw_d的开关/sw0、/sw2、/sw3关闭。藉此,从错误检测及订正模块17b输出的数据可以通过开关模块sw_d的开关/sw1输入数据汇流排控制器14。

104.接下来,参照图7,输入电源到半导体存储装置10时,半导体存储装置10辨别是否已接收包含第一构成暂存器信息的暂存器写入指令(步骤s100)。具体来说,指令解码器12判别暂存器写入指令是否已通过i/o模块11从外部装置输入。

105.在半导体存储装置10已接收暂存器写入指令的情况下(步骤s100:是),半导体存储装置10判别暂存器写入指令是否指定4个模式(模式a、模式b、模式c、模式d)之中的任一模式(步骤s101)。具体来说,指令解码器12,将输入的暂存器写入指令输出到更新控制部16。另一方面,更新控制部16根据包含于输入的暂存器写入指令的更新间隔,判别是否指定任一模式。

106.接着,半导体存储装置10,在指定4个模式(模式a、模式b、模式c、模式d)之中的任一模式的情况下(步骤s101:是),根据被指定的模式控制更新间隔(步骤s102)。具体而言,更新控制部16生成对应指定的模式的更新信号srefz,输出到指令解码器12。接着,半导体存储装置10回到步骤s100。

107.另外,半导体存储装置10,在没有指定4个模式(模式a、模式b、模式c、模式d)之中任一模式的情况下(步骤s101:否),根据预设的设定控制更新间隔(步骤s103)。具体来说,更新控制部16生成对应通常模式的更新信号srefz,输出到指令解码器12。接着,半导体存储装置10回到步骤s100。

108.另外,半导体存储装置10,在步骤s100的处理中,在没有接收到暂存器写入指令的情况下(步骤s100:否),也回到步骤s100。

109.如上所述,半导体存储装置10,从外部输入暂存器写入指令(特定指令)时,由于可以根据包含于暂存器写入指令的有关更新间隔的信息设定存储单元的更新间隔,通过将暂存器写入指令从外部装置(例如存储体控制器等)传送到半导体存储装置10,可以从外部设定存储单元的更新间隔。藉此,由于可以任意地设定存储单元的更新间隔,与一直将存储单元的更新间隔设定得很短相较之下,不只可以抑制耗电的增大,也可以回避起因于行捶击问题导致的数据破坏。

110.另外,暂存器写入指令(特定指令)被配置作为用以设定半导体存储装置的机能的指令。藉此,在设定半导体存储装置的机能的时序(例如输入电源时等)中,可以设定存储单元的更新间隔。

111.更进一步地,更新控制部16(第一控制部)被配置为每次从外部输入暂存器写入指令(特定指令)时,根据包含于暂存器写入指令的有关存储单元的更新间隔的信息,设定存储单元的更新间隔。藉此,由于可以在每次从外部输入暂存器写入指令时设定存储单元的更新间隔,存储单元的更新间隔可以适当地变更。

112.更进一步地,半导体存储装置10具备ecc控制部17(第二控制部),在包含阵列状配置的多个存储单元的存储单元阵列15c被分割为多个区块的情况下,选择多个区块中任一区块,将对应被选择区块内被存储于多个存储单元的数据所生成的错误订正码,存储于ecc单元阵列15d(特定存储区域)。藉此,由于可以只对应存储于存储单元阵列15c内多个区块中被选择的区块的数据,生成错误订正码,可以提高被存储于被选择区块的数据的保持特性。另外,与对应存储于存储单元阵列15c的所有数据生成错误订正码的情况相较之下,可以抑制存储检查数据等的电路规模增大,因而可以降低区域损失。

113.另外,存储检查数据的区域(特定区域),被设置为与存储单元阵列15c相异的ecc

单元阵列15d(其他存储单元阵列)。藉此,由于可以将错误订正码内的检查数据,存储于与存储数据的存储单元阵列15c不同的ecc单元阵列15d,可以通过在同样的存储单元存储检查数据,抑制数据的存储容量降低。

114.以下,针对本发明的第二实施例进行说明。本实施例的半导体存储装置10与第一实施例不同处在于ecc单元阵列15d被设置在存储单元阵列15c内。以下针对与第一实施例不同的构成进行说明。

115.如图8所示,ecc单元阵列15d,设置于存储单元阵列15c之内。如同上述第一实施例,由于ecc单元阵列15d可以与存储单元阵列15c为同样的构成,ecc单元阵列15d可以包含于存储单元阵列15c之内。

116.参照图9,存储单元阵列15c内的多个区块(在此例为区块0、

…

、区块n-4、区块n-3、区块n-2、区块n-1、区块n)之中与被选择区块(在此例为区块n-3)相异的其他区块(在此例为区块n)内的子区块(在此例为子区块n_a),被配置为ecc单元阵列15d。另外,区块n的存储容量比ecc单元阵列15d的存储容量更大的情况下,区块n内的ecc单元阵列15d用的子区块(子区块n_a)以外的其他子区块(在此例为子区块n_b),也可以被配置作为与存储单元阵列15c内的其他区块同样的数据用的存储区域。本实施例中,各开关模块sw_a、sw_b、sw_c、sw_d的控制方法与上述第一实施例相同。

117.在本实施例中,ecc控制部17也可以自动自存储单元阵列15c内的多个区块之中,选择其中的一配置作为ecc单元阵列15d的区块。例如,ecc控制部17也可以在存储单元阵列15c内的多个区块之中,选择在特定期间没有数据被存储的区块,配置作为ecc单元阵列15d的区块,在被选择的区块内配置ecc单元阵列15d。

118.另外,未满足用以在存储单元阵列15c内配置ecc单元阵列15d的特定条件(例如在特定期间内不存在被频繁存取的区块等)的情况下,存储单元阵列15c内的ecc单元阵列15d(在图9的例子中为子区块n_a),也可以不被配置为检查数据用的存储区域,而配置作为数据用的存储区域。此时,可以将存储单元阵列15c内的所有区块作为用以存储数据的存储区域来使用(即,不配置ecc单元阵列15d)。

119.如上所述,在本实施例中,存储检查数据的区域(特定存储区域),被设置为与存储单元阵列15c内的多个区块之中被选择的区块(此处为区块n-3)相异的其他区块(此处为区块n)。藉此,由于可以将错误订正码内的检查数据,存储于与存储数据的存储单元阵列15c相同的存储单元阵列,因此可以抑制电路规模的增大。

120.以下,针对本发明的第三实施例进行说明。本实施例的半导体存储装置10与上述各实施例不同处在于其设有2t2c单元阵列15e。以下,针对与上述各实施例不同的构成进行说明。

121.如图10所示,半导体存储装置10,设有2t2c单元阵列15e以替代上述各实施例中的ecc单元阵列15d,设有2t2c控制部18以替代上述各实施例中的ecc控制部17。另外,2t2c控制部18,也可以由专用的硬件装置或逻辑电路构成。

122.2t2c单元阵列15e,包含行列(阵列)状配置的多个存储单元(图示未显示)。各存储单元中存储通过i/o模块11从外部输入的数据。各存储单元可以是众所周知的2t2c(2晶体管2电容)型的存储单元。另外,由于对应各存储单元的数据控制细节亦为众所周知的技术,在本实施例中省略其说明。

123.2t2c控制部18,将从数据汇流排控制器14输出到存储单元阵列15c的数据存储于2t2c单元阵列15e。另外,2t2c控制部18,在数据从存储单元阵列15c输出(被读取)时,将存储于2t2c单元阵列15e的数据输出到数据汇流排控制器14。

124.另外,2t2c控制部18被配置为,在包含行列(阵列)状配置的2t2c型的多个存储单元的存储单元阵列被分割为多个区块的情况下,选择多个区块之中任一区块。更进一步地,2t2c控制部18被配置为将存储于被选择区块内的多个存储单元的数据,存储于以2t2c型存储单元构成的2t2c单元阵列15e。另外,2t2c控制部18在本发明中为“第二控制部”的一例。

125.更进一步地,2t2c控制部18,可以在每次从外部输入包含第二构成暂存器信息(如图11所示)的暂存器写入指令(特定指令)时,根据包含于暂存器写入指令的有关选择区块的信息,选择多个区块之中任一区块。藉此,从外部输入暂存器写入指令(特定指令)时,由于可以根据包含于所述指令的有关选择区块的信息,选择多个区块之中任一区块,可以通过将所述指令从外部装置(例如存储体控制器等)传送到半导体存储装置10,从外部设定(选择)多个区块之中任一区块(此处为输入于2t2c单元阵列15e所存储的数据的区块)。

126.此处,根据包含于暂存器写入指令的有关选择区块的信息选择任一区块的情况下,指令解码器12在包含第二构成暂存器信息的暂存器写入指令(特定指令)从外部装置通过i/o模块11输入时,将第二构成暂存器信息存储于第二构成暂存器(图示未显示)。另外,指令解码器12在输入包含第二构成暂存器信息的暂存器写入指令时,将暂存器写入指令输出到2t2c控制部18。

127.参照图11,第二构成暂存器被配置为可以从外部指定在特定数的位(此例为16位)内被分配的机能(此例为“2t2c适用区块控制”)。

128.第二构成暂存器的位11~9被配置为可以指定(选择)2t2c适用区块(也就是被输入存储于2t2c单元阵列15e的数据的区块)。在图11的示例中,经由第二构成暂存器的位11~9的值选择多个(在此例为4个)区块之中任一区块。另外,图11所示第二构成暂存器的构成,除了机能从“ecc适用控制区块”变成“2t2c控制区块”之外,其他与图5所示的构成相同。

129.举例而言,图11所示第二构成暂存器的内容,可以通过在半导体存储装置10电源输入时,从外部装置输入包含第二暂存器信息的暂存器写入指令,写入半导体存储装置10内的第二构成暂存器。另外,包含第二构成暂存器信息的暂存器写入指令,可以在电源输入半导体存储装置10的期间的任意时序输入。

130.参照图12,除了作为ecc控制部17以及ecc单元阵列15d的替代,设有2t2c控制部18以及2t2c单元阵列15e,以及除了没有设置开关模块sw_c之外,与第一实施例相同。本实施例中,与第一实施例同样地,存储单元阵列15c被分割为多个区块(在此例为区块0、

…

区块n-3、区块n-2、区块n-1、区块n)。另外,2t2c单元阵列15e的存储容量,也可以与各区块的存储容量相同。举例而言,存储单元阵列15c内的各区块的存储容量为2m位的情况下,2t2c单元阵列15e的存储容量为2m位。

131.首先,针对于存储单元阵列15c存储数据的情况进行说明。存储单元阵列15c的各区块的输入侧,输入(存储)从数据汇流排控制器14输出的数据。另外,输入到各区块之中被选择的区块(在此例为区块n-2)的数据,也会通过开关模块sw_a输入到2t2c控制部18。

132.此处,2t2c控制部18可以与上述各实施例中ecc控制部17同样地,根据包含于暂存器写入指令的有关选择区块的信息,选择区块(此处为区块n-2)。另外,2t2c控制部18,在输

入被存储于各区块之中被选择的区块(此处为区块n-2)的数据时,也控制开关模块sw_a将所述数据输入(存储)到2t2c单元阵列15e。

133.举例而言,2t2c控制部18,与上述各实施例中ecc控制部17同样地,控制开关模块sw_a的开关/sw1开启,控制开关模块sw_a的开关/sw0、/sw2、/sw3关闭。藉此,输入到存储单元阵列15c的区块n-2的数据,也会通过开关模块sw_a输入到2t2c单元阵列15e。

134.接下来,针对从存储单元阵列15c输出数据的情况进行说明。从存储单元阵列15c的各区块之中被选择的区块(此处为区块n-2)以外的其他区块输出的数据,通过开关模块sw_b输入数据汇流排控制器14。另一方面,从各区块之中被选择的区块(此处为区块n-2)输出的数据,不会通过开关模块sw_b输入到数据汇流排控制器14。作为替代,2t2c控制部18会将存储于2t2c单元阵列15e的数据通过开关模块sw_d输出到数据汇流排控制器14。此处,2t2c控制部18控制开关模块sw_b、sw_d,将存储于2t2c单元阵列15e的数据,作为从各区块之中被选择的区块(此处为区块n-2)输出的数据,输入到数据汇流排控制器14。

135.举例而言,2t2c控制部18,控制开关模块sw_b的开关sw0、sw2、sw3开启,控制开关模块sw_b的开关sw1关闭。另外,2t2c控制部18,控制开关模块sw_d的开关/sw1开启,控制开关/sw0、/sw2、/sw3关闭。藉此,可以将从2t2c单元阵列15e输出的数据,通过开关模块sw_d输入到数据汇流排控制器14。

136.藉此,可以只将存储于存储单元阵列15c内的多个区块之中被选择区块(区块n-2)的数据,存储于已知与1t1c型存储单元相较之下数据保持特性更高的2t2c型存储单元,并同时将所述数据从2t2c型的存储单元阵列中输出。

137.另外,本实施例中,虽然以设有作为替代ecc单元阵列15d以及ecc控制部17的2t2c单元阵列15e以及2t2c控制部18作为例子进行说明,上述这些也可以全部配置于半导体存储装置10中。

138.如上所述,根据本实施例的半导体存储装置10,由于可以只将被存储于存储单元阵列15c内多个区块之中被选择的区块的数据,存储于2t2c型的存储单元阵列,可以提高被存储于被选择区块的数据的保持特性。另外,本实施例中,由于不需要将存储单元阵列15c的所有存储单元都配置为2t2c型,因此,与存储单元阵列15c内所有存储单元由2t2c型构成相较之下,根据本实施例的半导体存储装置10,可以抑制电路规模的增大。

139.以上各实施例是为了使本发明容易理解而记载,上述记载并非用以限制本发明。因此,上述各实施例所揭露的各元件,目的为包含属于本发明的技术范围内的所有设计变更或均等物。

140.举例而言,上述各实施例中,虽然以选择存储单元阵列15c内多个区块之中任一区块的情况作为一例进行说明,本发明不限定于此情况。例如,也可以选择多个区块之中两个以上的区块,将存储于被选择的区块的数据存储于ecc单元阵列15d及/或2t2c单元阵列15e。

141.另外,上述各实施例中,虽然以暂存器写入指令包含有关更新间隔的信息以及有关选择区块的信息的情况作为一例进行说明,本发明不限于此情况。例如,有关更新间隔的信息及/或有关选择区块的信息,也可以被包含于其他指令(例如读取指令、写入指令等)之中。

142.更进一步地,虽然上述各实施例中,以ecc控制部17以及2t2c控制部18各自根据包

含于暂存器写入指令的有关选择区块的信息,选择多个区块之中任一区块的情况作为一例进行说明,本发明不限于此情况。举例而言,ecc控制部17及/或2t2c控制部18,也可以选择多个区块之中满足特定条件的区块。此处,举例而言,特定条件可以是特定期间内最频繁被存取(读取及/或写入)的区块。例如,选择特定期间内最频繁被存取的区块的情况下,ecc控制部17及/或2t2c控制部18,可以选择存储了在特定期间内被集中存取的数据(例如全域变数等)的区块。在此情况下,ecc控制部17及/或2t2c控制部18,可以根据从地址解码器13输出的行地址信号,通过计算多个区块中每个区块的存取数,决定(选择)特定期间内最频繁被存取的区块。另外,ecc控制部17及/或2t2c控制部18,可以每到特定的时序(例如每次经过特定时间等)便进行区块的选择。藉此,可以适当地变更被选择的区块。

143.更进一步地,在上述各实施例中,半导体存储装置10内的各模块11~18的构成仅为一例,也可以采用其他各种构成,适宜地进行变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。