1.本揭示案实施例是有关于半导体装置与其制造方法,特别是半导体装置中的气隙间隔物与其制造方法。

背景技术:

2.半导体集成电路(integrated circuit,ic)产业已历经了急速成长。ic材料及设计的技术性进步已产生了数个世代的ics。每个世代都比前一世代具有更小且更复杂的电路。

3.在ic演进的历程中,功能密度(即单位晶片面积的内连线装置数目)通常会增加,而几何尺寸(即可使用制程生产的最小元件(或线))却减少。此微缩化(scaling down)的制程通常通过提高生产效率及降低相关成本来提供效益。

4.然而,此微缩化的进展增加ic制程的复杂性。随着最小特征尺寸的缩小,制程变得更加困难。因此,如何在微缩半导体装置的发展中达到制程可靠度是一门挑战。

技术实现要素:

5.根据本揭示案的一个实施例,一种半导体装置包括基材、半导体鳍部、浅沟槽隔离结构、第一气隙间隔物、以及第一栅极结构。半导体鳍部自基材向上延伸。浅沟槽隔离结构横向地环绕半导体鳍部的下部。第一气隙间隔物介于浅沟槽隔离结构与半导体鳍部之间。第一栅极结构横跨半导体鳍部。

6.根据本揭示案的另一实施例,一种半导体装置包括基材、第一和第二半导体鳍部、浅沟槽隔离结构、第一和第二栅极结构、介电结构、以及第一气隙间隔物。第一和第二半导体鳍部自基材向上延伸。浅沟槽隔离结构横向地环绕第一半导体鳍部的下部和第二半导体鳍部的下部。第一栅极结构跨第一半导体鳍部。第二栅极结构横跨第二半导体鳍部。介电结构介于第一栅极结构的长轴端和第二栅极结构的长轴端之间。第一气隙间隔物横向地环绕介电结构。

7.根据本揭示案的又一实施例,一种制造半导体装置的方法包括:形成金属介层窗在第一介电层中、形成第二介电层在金属介层窗上、形成金属线延伸在第二介电层中并横跨金属介层窗、移除金属线的一部分以形成暴露出第一介电层的沟槽、形成牺牲间隔物作为沟槽的衬垫、形成介电间隔物作为牺牲间隔物的数个侧壁的衬垫、在形成介电间隔物之后移除牺牲间隔物以形成气隙间隔物、以及沉积介电材料在沟槽并密封气隙间隔物。

附图说明

8.阅读以下实施方法时搭配附图以清楚理解本揭示案的观点。应注意的是,根据业界的标准做法,各种特征并未按照比例绘制。事实上,为了能清楚地讨论,各种特征的尺寸可能任意地放大或缩小。

9.图1a至图1d根据本揭示案的一些实施例绘示制造半导体装置的方法m的流程图;

10.图2a至图46c、图47a和图47b根据本揭示案的一些实施例绘示制造半导体装置的其中一个阶段的示意图;

11.图48a至图55b根据本揭示案的一些实施例绘示制造半导体装置的其中一个阶段的示意图;

12.图56a至图61b根据本揭示案的一些实施例绘示制造半导体装置的其中一个阶段的示意图;

13.图62a至图66b根据本揭示案的一些实施例绘示制造半导体装置的其中一个阶段的示意图;

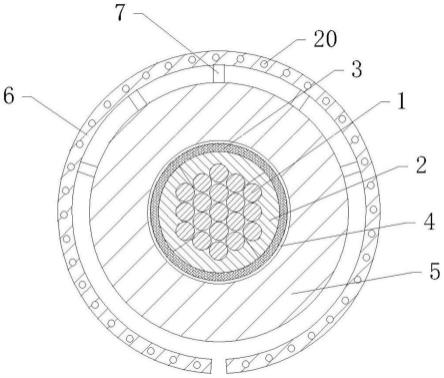

14.图67根据本揭示案的一些实施例绘示电浆制程设备的截面图。

15.【符号说明】

16.10:电浆制程设备

17.12:腔室

18.14:腔壁

19.16:基座抬升组合

20.18:基座组合

21.20:杆子

22.22:盖子/罩子

23.24:线圈

24.26:电源供应

25.28:电源供应

26.30:射频匹配网络

27.32:晶圆

28.100:半导体装置

29.101:基材

30.102:半导体鳍部

31.104:凹部

32.110:绝缘结构

33.112:牺牲层

34.112’:牺牲间隔物

35.114:间隔层

36.114’:间隔物

37.115:气隙间隔物

38.116:顶端

39.120:隔离介电质

40.120s:密封部分

41.130:栅极间隔物

42.131:源极/漏极结构

43.132:接触蚀刻终止层

44.133:层间介电层/隔离介电质

45.134:栅极介电层

46.135:金属栅极电极

47.136:介电覆盖层

48.140a:绝缘结构

49.140b:绝缘结构

50.140c:绝缘结构

51.142:牺牲层

52.142a:牺牲间隔物

53.142b:牺牲间隔物

54.142c:牺牲间隔物

55.144:间隔层

56.144a:间隔物

57.144b:间隔物

58.144c:间隔物

59.145a:气隙间隔物

60.145b:气隙间隔物

61.145c:气隙间隔物

62.146a:顶端

63.146b:顶端

64.146c:顶端

65.147:隔离介电质

66.147a:密封部分

67.147b:密封部分

68.147c:密封部分

69.150a:绝缘结构

70.150b:绝缘结构

71.152:牺牲层

72.152a:牺牲间隔物

73.152b:牺牲间隔物

74.154:间隔层

75.154a:间隔物

76.154b:间隔物

77.155a:气隙间隔物

78.155b:气隙间隔物

79.156a:顶端

80.156b:顶端

81.157:隔离介电质

82.157a:密封部分

83.157b:密封部分

84.158:图案化遮罩

85.160:硅化物层

86.162:导电材料

87.162a:源极/漏极接触件

88.164:介电层

89.165:金属介层窗

90.166:介电层

91.167:金属线

92.170a:绝缘结构

93.170b:绝缘结构

94.172:牺牲层

95.172a:牺牲间隔物

96.172b:牺牲间隔物

97.174:间隔层

98.174a:间隔物

99.174b:间隔物

100.175a:气隙间隔物

101.175b:气隙间隔物

102.176a:顶端

103.176b:顶端

104.177:隔离介电质

105.177a:密封部分

106.177b:密封部分

107.184:介电层

108.185:金属介层窗

109.194:栅极介电层

110.195:虚设栅极电极层

111.200:半导体装置

112.264:介电层

113.265:金属介层窗

114.266:介电层

115.267:金属线

116.270:绝缘结构

117.272:牺牲层

118.274:间隔层

119.275:气隙间隔物

120.276:顶端

121.277:隔离介电质

122.278:隔离介电质

123.278s:密封部分

124.284:介电层

125.285:金属介层窗

126.300:半导体装置

127.364:介电层

128.365:金属介层窗

129.366:介电层

130.367:金属线

131.370:绝缘结构

132.372:牺牲层

133.374:间隔层

134.375:气隙间隔物

135.376:顶端

136.377:隔离介电质

137.378:隔离介电质

138.378s:密封部分

139.384:介电层

140.385:金属介层窗

141.400:半导体装置

142.464:介电层

143.465:金属介层窗

144.466:介电层

145.467:金属线

146.472:牺牲层

147.475:气隙间隔物

148.477:隔离介电质

149.484:介电层

150.485:金属介层窗

151.b1-b1’:线

152.c1-c1’:线

153.b2-b2’:线

154.c2-c2’:线

155.b3-b3’:线

156.c3-c3’:线

157.b4-b4’:线

158.c4-c4’:线

159.d1:尺寸

160.g1:虚设栅极结构

161.g2:虚设栅极结构

162.gt1:栅极沟槽

163.gt2:栅极沟槽

164.h1:高度

165.h2:高度

166.o1:第一开口

167.o2:第二开口

168.o3:源极/漏极接触开口

169.o4:第四开口

170.o5:第五开口

171.o6:第六开口

172.o7:第七开口

173.p1:蚀刻制程

174.p2:蚀刻制程

175.p3:蚀刻制程

176.p4:蚀刻制程

177.p5:蚀刻制程

178.p6:蚀刻制程

179.p7:蚀刻制程

180.p8:蚀刻制程

181.p9:蚀刻制程

182.p10:蚀刻制程

183.p11:蚀刻制程

184.p12:蚀刻制程

185.p13:蚀刻制程

186.p14:蚀刻制程

187.p15:蚀刻制程

188.p16:蚀刻制程

189.rg1:栅极结构

190.rg2:栅极结构

191.s101~s150:步骤

192.t:沟槽

193.t1:厚度

194.t2:厚度

195.t3:厚度

196.t4:厚度

197.t5:厚度

198.t6:厚度

199.t7:厚度

200.t8:厚度

201.w1:宽度

具体实施方式

202.以下的揭示内容提供许多不同的实施例或范例,以展示本揭示案的不同特征。以下将揭示本揭示案各部件及其排列方式的特定范例,用以简化本揭示案叙述。当然,这些特定范例并非用于限定本揭示案。例如,若是本揭示案以下的发明内容叙述了将形成第一结构于第二结构之上或上方,即表示其包括了所形成的第一及第二结构是直接接触的实施例,亦包括了尚可将附加的结构形成于上述第一及第二结构之间,则第一及第二结构为未直接接触的实施例。此外,本揭示案说明中的各式范例可能使用重复的参照符号及/或用字。这些重复符号或用字的目的在于简化与清晰,并非用以限定各式实施例及/或所述外观结构之间的关系。

203.再者,为了方便描述附图中一元件或特征部件与另一(些)元件或特征部件的关系,可使用空间相关用语,例如“在...之下”、“下方”、“下部”、“上方”、“上部”及诸如此类用语。除了附图所绘示的方位外,空间相关用语亦涵盖使用或操作中的装置的不同方位。当装置被转向不同方位时(例如,旋转90度或者其他方位),则其中所使用的空间相关形容词亦将依转向后的方位来解释。

204.关于本文中所使用的“约”、“大约”或“大致上”一般通常是指数值的误差或范围百分之二十以内、或百分之十以内、或百分五之以内。文中若无明确说明,其所提及的数值皆视作为近似值,即如“约”、“大约”或“大致上”所表示的误差或范围。

205.除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本揭示案所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本揭示案的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

206.本揭示案的实施例是有关于但不限于鳍式场效晶体管(fin-like field-effect transistor,finfet)装置。finfet装置可如互补式金属氧化物半导体(complementary metal oxide semiconductor,cmos)装置,其中包括p型金属氧化物半导体(pmos)finfet装置和n型金属氧化物半导体(nmos)finfet装置。下文中使用一或多个finfet作为范例,以描述本揭示案的各种实施例。然而,应理解的是,除非特定申明之外,本揭示案的应用不限于特定装置。

207.可通过任何合适的方法来图案化鳍部。例如,鳍部可使用一或更多个微影制程来图案化,包括双重图案化或多重图案化制程。一般而言,双重图案化或多重图案化制程结合微影术及自对准制程,允许形成图案,此图案具有的间距例如小于使用单一直接微影制程可获得的间距。例如,在一实施例中,牺牲层在基材上形成,并通过使用微影制程而图案化。使用自对准制程在图案化的牺牲层旁边形成间隔物。随后移除牺牲层,留下的间隔物可用作遮罩来图案化鳍部。

208.为了提供电性绝缘和结构支撑给集成电路(integrated circuit,ic)结构的半导体特征(例如,氧化物扩散区(oxide diffusion,od)、金属栅极、源极/漏极接触件、或在多层互连结构中的金属线),可形成物理性间隔物环绕半导体特征。然而,由于物理性间隔物具有较大的介电常数,所以半导体特征上的物理性间隔物可能产生额外的电容使ic结构的

整体电容值增加。故,本揭示案的各个实施例提供一种气隙间隔物环绕ic结构的半导体特征(例如,od、金属栅极、源极/漏极接触件、或在多层互连结构中的金属线)。其中一个益处在于可降低ic结构的整体电容值,进而改善电阻电容延迟(rc delay)亦改善装置表现。详细而言,气隙间隔物的介电常数等于1,较物理性间隔物的介电常数低。因此可通过形成气隙间隔物环绕半导体特征以降低ic结构的整体电容。

209.请参照图1a至图1d,图1a至图1d根据本揭示案的一些实施例绘示制造半导体装置的方法m的流程图,其中制造半导体装置包括形成气隙间隔物在半导体鳍部、栅极结构、及/或金属线上。方法m提供整个ic结构制程中的一部分相关制程。应理解的是,可能须在图1a至图1d操作之前、过程中、或之后进行额外的操作步骤,并且一些所述的操作步骤在一些其他的实施例中可能被置换或省略。操作步骤的顺序可能会交换。应注意的是,图1a至图1d已简化以为了清楚了解本揭示案。再者,集成电路可能配置成系统单晶片(system-on-chip,soc)装置,其中包括各种不同的pmos和nmos晶体管以提供在不同电压下的操作。

210.图2a至图45c、图46b、图46c和图47b根据本揭示案的一些实施例绘示制造半导体装置100的其中一个阶段的示意图。图2a至图45a绘示俯视图。图2b至图11b绘示沿图2a至图11a的线b1-b1’的截面图。图2c至图11c绘示沿图2a至图11a的线c1-c1’的截面图。图12b至图21b绘示沿图12a至图21a的线b2-b2’的截面图。图12c至图21c绘示沿图12a至图21a的线c2-c2’的截面图。图22b至图35b绘示沿图22a至图35a的线b3-b3’的截面图。图22c至图35c绘示沿图22a至图35a的线c3-c3’的截面图。图36b至图45b绘示沿图36a至图45a的线b4-b4’的截面图。图36c至图45c绘示沿图36a至图45a的线c4-c4’的截面图。

211.下方各个实施例将搭配附图图2a至图11c以详细描述如何形成气隙间隔物环绕半导体装置的od区域(例如,半导体鳍部),进而降低两两相邻的od区域之间的电容值。在一些实施例中,围绕在od区域的浅沟槽隔离(shallow trench isolation,sti)结构和形成在sti结构上的气隙间隔物可合称为具有气隙的od切口(air-inside cut od)。

212.方法m始于步骤s101,在步骤s101中,图案化基材以形成一或多个半导体鳍部。在步骤s101的实施例中,如图2a至图2c所示,晶圆(wafer)进行一系列的沉积和微影制程,借此形成衬垫层(pad layer)、遮罩层(mask layer)及图案化的光阻层在晶圆的基材101上。在一些实施例中,基材101可为半导体基材,如块材半导体、绝缘体上半导体(semiconductor-on-insulator,soi)基材等。一般而言,绝缘体上半导体基材是在绝缘层上形成的半导体材料层。绝缘层可为埋置式氧化物(buried oxide,box)层、氧化硅层等。设置绝缘体层的基材一般为硅或玻璃基材。亦可使用其他基材,如多层基材或梯度基材。在一些实施例中,基材101的半导体材料可包括硅、锗、化合物半导体、合金半导体、上述各者的组合、或类似者。化合物半导体可包括碳化硅、砷化镓、磷化镓、磷化铟、砷化铟及/或锑化铟。合金半导体可包括硅锗、磷砷化镓、砷化铝铟、砷化铝镓、砷化镓铟、磷化镓铟及/或镓铟砷磷。

213.在一些实施例中,衬垫层为一层薄膜,其具有氧化层,例如使用热氧化制程形成的氧化层。衬垫层可做为基材101和遮罩层之间的粘附层。在遮罩层的蚀刻过程中,衬垫层亦可做为蚀刻终止层。在一些实施例中,遮罩层包括氮化硅,例如使用低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)或电浆增强cvd(plasma enhanced cvd,pecvd)。在后续微影制程中,遮罩层可做为硬遮罩(hard mask)。光阻层形成在遮罩层上,并

且经过图案化之后形成开口在光阻层中,其中这些开口显露出遮罩层的一部分区域。

214.接下来,透过光阻层对遮罩层和衬垫层进行蚀刻制程,以暴露出位于下方的基材101。暴露出来的基材101随后经过蚀刻而形成沟槽t。位于两两相邻沟槽t之间的基材101部分可被称为半导体鳍部102。在蚀刻基材101之后,移除衬垫层、遮罩层、和图案化的光阻层。接着,可选择性地执行清洁制程以移除半导体基材101的原生氧化层。举例来说,清洁制程可包括使用稀释的氢氟酸(diluted hydrofluoric acid)。

215.请重新参照图1a,方法m继续步骤s102,在步骤s102中,毯覆式沉积第一牺牲层在基材上。在步骤s102的实施例中,如图3a至图3c所示,毯覆式沉积牺牲层112在图2a至图2c的结构上(即,基材101和半导体鳍部102上)。在一些实施例中,牺牲层112可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,牺牲层112可能是如氮化硅的介电材料。在一些实施例中,牺牲层112具有的材料不同于基材101。在一些实施例中,牺牲层112具有约1纳米(nm)至约5nm的厚度t1,例如1、2、3、4或5nm的厚度t1,但本揭示案不限于此。在一些实施例中,牺牲层112可具有多层结构。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或电浆增强原子层沉积(plasma enhanced atomic layer deposition,peald)等以形成牺牲层112。

216.请重新参照图1a,方法m继续步骤s103,在步骤s103中,蚀刻第一牺牲层以形成第一牺牲间隔物。在步骤s103的实施例中,如图4a至图4c所示,形成牺牲间隔物112’在半导体鳍部102的相对侧上。详细而言,执行非等向性蚀刻制程p1(例如,反应性离子蚀刻(reactive ion etching,rie)制程或原子层蚀刻(atomic layer etching,ale))以选择性移除牺牲层112的水平部分。保留的牺牲层112的垂直部分形成牺牲间隔物112’。每个牺牲间隔物112’从基材101的顶表面沿着半导体鳍部102的侧壁垂直延伸。牺牲间隔物112’具有高度h1(从基材101的顶表面量测)。牺牲间隔物112’的高度h1随非等向性蚀刻制程p1的制程条件而变(例如蚀刻操作时间或类似者)。非等向性蚀刻制程p1可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当氮化硅用来做为氮化物牺牲间隔物112’时,可使用磷酸(例如h3po4)来蚀刻牺牲层112(见图3a至图3c),但本揭示案不限于此。

217.进一步详细描述图4a至图4c,非等向性蚀刻制程p1对牺牲层112(见图3a至图3c)的蚀刻速率快于对基材101的蚀刻速率。牺牲层112比基材101的蚀刻选择比可大于约10。当牺牲层112比基材101的蚀刻选择比小于约10时,非等向性蚀刻制程p1可能会明显蚀刻基材101,从而对半导体装置产生不良影响。

218.请重新参照图1a,方法m继续步骤s104,在步骤s104中,毯覆式沉积第一间隔层在基材上。在步骤s104的实施例中,如图5a至图5c所示,毯覆式沉积间隔层114在图4a至图4c所示的结构上(即,基材101、半导体鳍部102、和牺牲间隔物112’)。间隔层114具有的材料可不同于牺牲间隔物112’的材料。在一些实施例中,间隔层114可包括氧化硅、氮化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,间隔层114可能是如氧化硅的介电材料。在一些实施例中,间隔层114可具有多层结构。在一些实施例中,间隔层114具有约1纳米(nm)至约5nm的厚度t2,例如1、2、3、4或5nm的厚度t2,但本揭示案不限于此。在一些实施例

中,可使用沉积技术,例如pecvd、lpcvd、或peald等来形成间隔层114。

219.请重新参照图1a,方法m继续步骤s105,在步骤s105中,蚀刻第一间隔层以形成第一间隔物。在步骤s105的实施例中,如图6a至图6c所示,形成间隔物114’在半导体鳍部102的相对侧上。详细而言,执行非等向性蚀刻制程p2(例如,反应性离子蚀刻(reactive ion etching,rie)制程或原子层蚀刻(atomic layer etching,ale))以选择性移除间隔层114的水平部分。保留的间隔层114的垂直部分形成间隔物114’。每个间隔物114’从基材101的顶表面沿着半导体鳍部102和牺牲间隔物112’的侧壁垂直延伸。间隔物114’具有高度h2(从基材101的顶表面量测)。在一些实施例中,间隔物114’的高度h2可大致上相同于牺牲间隔物112’的高度h1(见图4a至图4c)。间隔物114’的高度h2可随非等向性蚀刻制程p2的制程条件而变(例如蚀刻操作时间或类似者)。非等向性蚀刻制程p2可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当氧化硅用来做为氧化物间隔物114’时,可使用氢氟酸溶液或氟化氢气体来蚀刻间隔层114(见图5a至图5c),但本揭示案不限于此。

220.进一步详细描述图6a至图6c,非等向性蚀刻制程p2对间隔层114(见图5a至图5c)的蚀刻速率快于对基材101和对牺牲间隔物112’的蚀刻速率。举例来说,间隔层114比基材101的蚀刻选择比可大于约10及/或间隔层114比牺牲间隔物112’的蚀刻选择比可大于约10。当间隔层114比基材101的蚀刻选择比小于约10时,非等向性蚀刻制程p2可能会明显蚀刻基材101,从而对半导体装置造成不良影响。同样地,当间隔层114比牺牲间隔物112’的蚀刻选择比小于约10时,非等向性蚀刻制程p2可能会明显蚀刻牺牲间隔物112’,从而对半导体装置造成不良影响。

221.请重新参照图1a,方法m继续步骤s106,在步骤s106中,移除第一牺牲间隔物以形成第一气隙间隔物。在步骤s106的实施例中,如图7a至图7c所示,执行选择性蚀刻制程p3以选择性移除牺牲间隔物112’(见图6a至图6c)。如此一来,气隙间隔物115可形成在半导体鳍部102和间隔物114’之间。换句话说,气隙间隔物115隔开半导体鳍部102和间隔物114’。在气隙间隔物115形成之后,间隔物114’和气隙间隔物115可合称为绝缘结构110。因为通过移除牺牲间隔物112’(见图6a至图6c)而形成绝缘结构110,所以气隙间隔物115具有原本牺牲间隔物112’的形状。在一些实施例中,基材101暴露于气隙间隔物115中。

222.如前所述,牺牲间隔物112’(见图6a至图6c)的厚度在约1nm和约5nm的范围之间。因此,气隙间隔物115的厚度也在约1nm和约5nm的范围之间,例如约1、2、3、4或5nm。如果牺牲间隔物112’的厚度小于1nm,因牺牲间隔物112’太窄以至于蚀刻剂难以进入半导体鳍部102和间隔物114’之间的空间,进而影响气隙间隔物115的形成。在另一方面,如果牺牲间隔物112’的厚度大于5nm,则形成的气隙间隔物115的厚度可能会太宽,以致于后续形成在气隙间隔物115上方的材料可能容易流入气隙间隔物115的底部,进而影响气隙间隔物115的形成。因此,在蚀刻制程p3过程中,牺牲间隔物112’(见图6a至图6c)可能经过蚀刻之后而显露出半导体鳍部102的垂直侧壁,进而影响气隙间隔物115的形成。

223.在本揭示案中,牺牲层112具有例如大于1的介电常数。在另一方面,绝缘结构110包括气隙间隔物115,其中气隙间隔物115具有等于1的介电常数且小于牺牲层112的介电常

数。因此,绝缘结构110的等效介电常数因气隙间隔物115的形成而降低。如此一来,绝缘结构110的整体电容值可降低,进而改善电阻电容延迟(rc delay)亦改善装置表现。除此之外,因为通过移除牺牲间隔物112’(见图6a至图6c)而形成气隙间隔物115,所以气隙间隔物115可具有原本牺牲间隔物112’的形状,故可轻易调控气隙间隔物115的尺寸,并且进一步地调控绝缘结构110的等效电容。

224.在一些实施例中,蚀刻制程p3可包括选择性等向性蚀刻制程(例如,高电压及/或低偏压区域的反应性离子蚀刻)。蚀刻制程p3可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当硅用于牺牲间隔物112’之中时,可使用nh4oh来蚀刻牺牲间隔物112’(见图6a至图6c),但本揭示案不限于此。进一步详细描述图7a至图7c,蚀刻制程p3对牺牲间隔物112’(见图6a至图6c)的蚀刻速率快于对基材101和对间隔物114’的蚀刻速率。举例来说,牺牲间隔物112’比基材101的蚀刻选择比可大于约10及/或牺牲间隔物112’比间隔物114’的蚀刻选择比可大于约10。当牺牲间隔物112’比基材101的蚀刻选择比小于约10时,蚀刻制程p3可能会明显蚀刻基材101,从而对半导体装置产生不良影响。同样地,当牺牲间隔物112’比间隔物114’的蚀刻选择比小于约10时,蚀刻制程p3可能会明显间隔物114’,从而对半导体装置产生不良影响。在一些实施例中,蚀刻制程p3可能是等向蚀刻制程。在一些实施例中,蚀刻制程p3使用蚀刻剂不同于蚀刻制程p2,因为蚀刻制程p3用来选择性蚀刻牺牲间隔物112’内部的材料,而蚀刻制程p2用来选择性蚀刻牺牲间隔物114’外部的材料。

225.请重新参照图1a,方法m继续步骤s107,在步骤s107中,蚀刻第一间隔物的上部以形成弧形顶角在第一间隔物上。在步骤s107的实施例中,如图8a至图8c所示,蚀刻间隔物114’以形成锥形顶端116在间隔物114’上。在图8a至图8c中,对间隔物114’执行蚀刻制程p4。在一些实施例中,蚀刻制程p4可为电浆蚀刻制程并采用一或多个蚀刻剂。一般而言,电浆包括局部离子化的气体混合物,其中一部分的原子或分子失去电子而形成带正电的离子。可通过电场和磁场以形成并控制电浆。施加在气体混合物上的电力可形成电浆。电力转移至电子上,具能量的电子随后碰撞气体混合物内的原子或分子,因起始反应例如离子化、激发、解离而产生离子、更多的电子和自由基。电子的撞击可离子化原子或分子在电浆中或是解离分子而形成自由基。自由基可能与合适的气相物质结合而回到当初的状态或是产生新的物质。

226.进一步详细描述图8a至图8c,执行非零偏压电浆蚀刻(non-zero bias plasma etching)制程以蚀刻间隔物114’的上部,使得间隔物114’的顶端呈现锥形。相较于零偏压,非零偏压可驱动更多的电浆以微缩化间隔物114’。举例来说,非零偏压电浆蚀刻制程以离子轰击(ion bombardment)的方式来移除间隔物114’的物质。因此,间隔物114’的上部的宽度小于间隔物114’的下部的宽度。换句话说,气隙间隔物115的上部的宽度大于气隙间隔物115的下部的宽度,因此后续形成的隔离介电质可流进气隙间隔物115的上部。如此一来,后续形成的隔离介电质可密封气隙间隔物115的上部,并且在后续制程中可避免其他材料填入气隙间隔物115中。

227.间隔物114’的形貌随蚀刻制程p4的制程条件而变(例如蚀刻操作时间或类似者)。

蚀刻制程p4可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,非零偏压电浆蚀刻制程使用c4f6和氩气的混合气体并且偏压操作在约50瓦(w)到约1000w的范围之间。如果偏压功率高于约1000w,则电浆可能对半导体鳍部102产生预期之外的损害。如果偏压功率低于约50w,则间隔物114’的锥形顶端可能不足以让后续形成的隔离介电质填入气隙间隔物115的上部。

228.请参照图67,图67根据本揭示案的一些实施例绘示例示性电浆制程设备10的截面图。在一些实施例中,电浆制程设备10可包括感应耦合电浆(inductively coupled plasma,icp)或电容耦合电浆(capacitive coupling plasma,ccp)的电浆源以及射频(rf)电源供应的偏压供应源。如图67所示,电浆制程设备10包括腔室12,其中腔室12具有接地的腔壁14。腔室12由移动式盖子或罩子22关闭,并且腔室12还包括基座组合18,其中基座抬升组合16可驱动杆子20使基座组合18向上或向下移动。感应耦合电浆线圈24围绕盖子22并连接射频源电源供应26。基座组合18透过射频匹配网络(rf match network)30以匹配阻抗,并连接至射频电源供应28。在电浆制程设备10的操作过程中,基座组合18乘载晶圆32在腔室12中。气体供应器(未绘出)导入可产生电浆的气体,例如氩气,至电浆制程设备10内。通过气体移除机制(未绘出)从电浆制程设备10中移除易挥发的产物以及未反应的电浆物质。射频源电源供应26提供的高电压信号将提供至感应耦合电浆线圈24,以启动(点火)并维持电浆在电浆制程设备10中。因为大电压施加在感应耦合电浆线圈24以及在电浆制程设备10中产生的电场,电浆制程设备10的电浆启动主要是透过感应耦合电浆线圈24的静电耦合搭配来源气体。当启动(点火)之后,随时间变化的磁场所引导出的电磁感应现象可维持电浆在电浆制程设备10内,其中随时间变化的磁场是由应用于感应耦合电浆线圈24的交流电所产生。透过射频电源供应28,基座组合18基本上为电性偏压以提供晶圆32离子能量,其中离子能量与电浆制程设备10中感应耦合电浆线圈24和射频源电源供应26的射频电压无关。这样有助于精准控制轰击晶圆32表面的蚀刻剂离子的能量。非零偏压蚀刻的过程中,在开启射频电源供应28的情况下,非零偏压蚀刻可由感应耦合电浆或电容耦合电浆源电源供应26所产生。相反地,零偏压蚀刻的过程中,在不开启射频电源供应28的情况下,零偏压蚀刻可由感应耦合电浆源电源供应26所产生。非零偏压蚀刻和零偏压蚀刻可产生不同的栅极结构的形貌,相关描述将于下文中讨论。在一些实施例中,电浆制程设备10亦可为电子回旋共振(electron cyclotron resonance,ecr)装置,但本揭示案不限于此。

229.请重新参照图1a,方法m继续步骤s108,在步骤s108中,形成第一隔离介电质以填满超出沟槽以及密封第一气隙间隔物。在步骤s108的实施例中,如图9a至图9c所示,形成隔离介电质120以填满超出沟槽并覆盖半导体鳍部102。沟槽t中的隔离介电质120可被称为浅沟槽隔离(sti)结构。如前所述,由于气隙间隔物115的上部的宽度大于气隙间隔物115的下部的宽度,所以隔离介电质120的材料可流进气隙间隔物115的上部,从而密封气隙间隔物115。相应地,隔离介电质120具有密封部分120s位于半导体鳍部102和间隔物114’之间。因此,隔离介电质120的密封部分120s封住气隙间隔物115的上端,并且在后续制程中可避免其他材料填入气隙间隔物115中。在一些实施例中,隔离介电质120的密封部分120s可被称为介电密封件(dielectric sealer)或介电结构(dielectric structure)。

230.在一些实施例中,隔离介电质120的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fluoride-doped silicate glass,fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质120的形成方式包括高密度电浆cvd(high density plasma cvd,hdpcvd),其中使用硅烷(silane,sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质120的形成方式包括半大气压cvd(sub-atmospheric cvd,sacvd)或高深宽比制程(high aspect-ratio process,harp),其中制程气体可包括四乙氧基硅烷(tetraethylorthosilicate,teos)和臭氧(ozone,o3)。在一些实施例中,隔离介电质120的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质120可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。接下来,选择性地对隔离介电质120进行热退火制程。在一些实施例中,隔离介电质120的组成材料可相同于间隔物114’。在一些实施例中,隔离介电质120的组成材料可不同于间隔物114’。

231.请重新参照图1a,方法m继续步骤s109,在步骤s109中,对第一隔离介电质执行第一平坦化制程。在步骤s109的实施例中,如图10a至图10c所示,执行如化学机械研磨(chemical mechanical polish,cmp)的平坦化制程以移除半导体鳍部102上多余的隔离介电质120,使得半导体鳍部102的顶表面显露出来,而气隙间隔物115保持被隔离介电质120的密封部分120s覆盖住。

232.请重新参照图1a,方法m继续步骤s110,在步骤s110中,凹陷隔离介电质和第一间隔物。在步骤s110的实施例中,如图11a至图11c所示,凹陷隔离介电质120和间隔物114’并且移除隔离介电质120的密封部分120s的上部的一部分,举例来说,使用蚀刻制程,且蚀刻制程的蚀刻剂可包括稀释的氢氟酸、siconi(具有hf和nh3)或类似者。在凹陷隔离介电质120和间隔物114’之后,一部分的半导体鳍部102高于隔离介电质120和间隔物114’的顶表面,而气隙间隔物115保持被隔离介电质120的密封部分120s封住且覆盖。

233.下文将搭配参照图12a至图22c详细地描述实施例,为了使半导体装置的两个栅极结构之间电性绝缘,隔离介电质(例如,如图22a所示的隔离介电质147)形成在两个栅极结构之间。气隙间隔物形成两个栅极结构之间的隔离介电质的周围,借此降低两个相邻栅极结构间的电容值。在一些实施例中,两个栅极结构之间的隔离介电质和形成在隔离介电质上的气隙间隔物可合称为具有气隙的金属栅极切口(air-inside cut metal gate,air-inside cmg)。

234.请重新参照图1a,方法m继续步骤s111,在步骤s111中,形成虚设栅极结构在半导体鳍部上。在步骤s111的实施例中,如图12a至图12c所示,形成虚设栅极结构g1和g2在半导体鳍部102上。详细而言,毯覆式地形成栅极介电层194在基材101上以披覆半导体鳍部102和隔离介电质120,并且形成虚设栅极电极层195在栅极介电层194上。在一些实施例中,栅极介电层194的组成包括高介电常数介电材料,例如金属氧化物、过度金属氧化物、或类似者。高介电常数介电材料例如氧化铪(hafnium oxid,hfo2)、氧化铪硅(hafnium silicon oxide,hfsio)、氧化铪钽(hafnium tantalum oxide,hftao)、氧化铪钛(hafnium titanium oxide,hftio)、氧化铪锆(hafnium zirconium oxide,hfzro)、氧化锆(zirconium oxide)、氧化钛(titanium oxide)、氧化铝(aluminum oxide,al2o3)、氧化铪-氧化铝合金(hfo2—

al2o

3 alloy)、或其他合适的介电材料。在一些实施例中,栅极介电层194是氧化物层。栅极介电层194的形成方式可包括沉积制程如cvd、物理气相沉积(physical vapor deposition,pvd)、原子层沉积(atomic layer deposition,ald)或其他合适的技术。在一些实施例中,虚设栅极电极层195可包括多晶硅、多晶硅锗、金属氮化物、金属硅化物、金属氧化物、或金属。在一些实施例中,虚设栅极电极层195包括含金属的材料,例如tin、tan、tac、co、ru、al、上述的组合、或上述的多层结构。虚设栅极电极层195的形成方式可包括cvd、pvd、溅镀制程、其他合适用于沉积导电材料的技术。

235.接下来,遮罩层形成在虚设栅极电极层195(未绘出)上并通过图案化制程形成分别的遮罩部分。图案化的遮罩层的形成方式可包括一系列的沉积、微影图案化和蚀刻制程。微影图案化制程可包括光阻涂覆(例如旋转涂覆)、软烤、光罩对准、曝光、曝光后烘烤、光阻显影、润洗、干燥(例如硬烤)及/或其他适当的操作。然后,将图案化的遮罩层当作蚀刻遮罩并进行一或多道蚀刻制程以形成虚设栅极结构g1和g2,蚀刻制程之后移除图案化的遮罩层。蚀刻制程可包括干式蚀刻、湿式蚀刻及/或其他的蚀刻方法(例如反应性离子蚀刻)。每个虚设栅极结构g1和g2具有栅极介电层194和虚设栅极电极层195,其中虚设栅极电极层195设置在栅极介电层194上。虚设栅极结构g1和g2的长轴大致上彼此平行,并且虚设栅极结构g1和g2的长轴大致上垂直于半导体鳍部102的长轴。可使用后栅极(gate-last)或置换栅极制程将虚设栅极结构g1和g2替换成置换栅极结构rg1和rg2(见图13a至图13c)。

236.请重新参照图1a,方法m继续步骤s112,在步骤s112中,沿着虚设栅极结构的侧壁形成栅极间隔物。在步骤s112的实施例中,如图12a至图12c所示,沿着虚设栅极结构g1和g2的侧壁形成栅极间隔物130。在一些实施例中,栅极间隔物130可包括氧化硅、氮化硅、氮氧化硅、碳化硅、碳氮化硅、碳氮氧化硅、碳氧化硅、多孔隙介电材料、氢掺杂碳氧化硅(sioc:h)、低介电常数的介电材料、其他合适的介电材料。栅极间隔物130可包括单层或是由不同介电材料组成的多层结构。栅极间隔物130的形成方法可包括毯覆式形成介电层在虚设栅极结构g1和g2以及基材101上,其中可使用cvd、pvd或ald进行毯覆式形成,然后执行蚀刻(例如非等向性蚀刻制程)以移除介电层的水平部分。介电层留在虚设栅极结构g1和g2的侧壁上的部分可做为栅极间隔物130。在一些实施例中,栅极间隔物130可用来决定后续形成的掺杂区域,例如源极/漏极区域。栅极间隔物130可进一步地用来控制或调整源极/漏极区域的形貌。

237.请重新参照图1a,方法m继续步骤s113,在步骤s113中,形成源极/漏极凹部在鳍部中。在步骤s113的实施例中,如图12a至图12c所示,凹陷半导体鳍部102中未受虚设栅极结构g1和g2覆盖的部分以及凹陷栅极间隔物130以形成凹部104。凹部104的形成方式可包括干式蚀刻、湿式蚀刻、或上述的组合。蚀刻制程可包括反应性离子蚀刻,其中将虚设栅极结构g1和g2和栅极间隔物130做为遮罩,或是其他合适的移除制程。在蚀刻制程之后,可执行预清洗制程,预清洗制程使用氢氟酸或其他适当的溶液来清洁凹部104。

238.请参照图1b,方法m继续步骤s114,在步骤s114中,形成源极/漏极结构在凹部中。在步骤s114的实施例中,如图12a至图12c所示,分别形成磊晶源极/漏极结构131在凹部104中。磊晶源极/漏极结构131的形成包括一或多道的磊晶制程,借此在半导体鳍部102上形成结晶态的硅特征、硅锗特征、磷化硅(sip)特征、碳化硅(sic)特征或其他合适的特征。在一些实施例中,由于磊晶源极/漏极结构131的晶格常数不同于半导体鳍部102的晶格常数,所

以磊晶源极/漏极结构131之间的通道区域可能受到磊晶源极/漏极结构131的压缩和拉伸,进而改善半导体装置的载子移动率(carrier mobility)并提升装置表现。

239.在一些实施例中,磊晶制程可包括cvd技术(例如气相磊晶(vapor-phase epitaxy(vpe)及/或超高真空cvd(ultra-high vacuum cvd,uhv-cvd))、分子束磊晶、及/或其他合适的制程。磊晶制程可使用气相及/或液相前驱物,此前驱物可与半导体鳍部102的组成(例如,硅、硅锗、磷化硅等)发生反应。磊晶源极/漏极结构131可进行原位(in-situ)掺杂。掺杂物质可包括p型掺杂剂(如硼或bf2)、n型掺杂剂(如磷或砷)、任何其他合适的掺杂剂、或上述的组合。若磊晶源极/漏极结构131未进行原位掺杂,可执行布植制程以掺杂磊晶源极/漏极结构131。进行一或多道退火制程以活化磊晶源极/漏极结构131。退火制程可包括快速加热退火(rapid thermal annealing,rta)及/或雷射退火制程。

240.请重新参照图1b,方法m继续步骤s115,在步骤s115中,形成接触蚀刻终止层(contact etch stop layer,cesl)和层间介电(interlayer dielectric layer,ild)层在源极/漏极结构、虚设栅极结构和栅极间隔物上。在步骤s115的实施例中,如图12a至图12c所示,形成接触蚀刻终止层(cesl)132在源极/漏极结构131、虚设栅极结构g1和g2、以及栅极间隔物130上,并且形成层间介电(ild)层133在cesl132上,接着进行cmp制程移除ild层133和cesl132多余的材料以显露出虚设栅极结构g1和g2。cmp制程可平坦化ild层133的顶表面使其与虚设栅极结构g1和g2的顶表面和栅极间隔物130的顶表面同高度。在一些实施例中,ild层133包括氧化硅、氮化硅、氮氧化硅、teos、磷硅酸盐玻璃(phosphosilicate glass,psg)、掺硼磷硅酸盐玻璃(borophosphosilicate glass,bpsg)、低介电常数的介电材料及/或其他合适的介电材料。低介电常数的介电材料例如氟掺杂硅酸盐玻璃(fsg)、碳掺杂氧化硅、非晶相氟化碳、聚对二甲苯(perylene)、双苯并环丁烯(bis-benzocyclobutenes,bcb)、或聚酰亚胺(polyimide)。ild层133的形成方式可包括cvd、ald、涂覆式玻璃、或其他合适的方式。在一些实施例中,cesl132可包括氮化硅、氮氧化硅、或其他合适的材料。cesl132的形成方式可包括cvd、低压cvd、ald、或其他合适的方式。

241.请重新参照图1b,方法m继续步骤s116,在步骤s116中,形成栅极结构以置换虚设栅极结构。在步骤s116的实施例中,如图13a至图13c所示,移除图12a至图12c所示的虚设栅极结构g1和g2,并形成栅极沟槽gt1和gt2,其中栅极沟槽gt1和gt2对应于图12a至图12c所示的虚设栅极结构g1和g2。在一些实施例中,虚设栅极结构g1和g2的移除方式可包括进行第一蚀刻制程,以及在第一蚀刻制程之后进行第二蚀刻制程。在一些实施例中,在第一蚀刻制程中移除大部分的虚设栅极电极层195,而在第二蚀刻制程中移除大部分的栅极介电层194,其中第二蚀刻制程和第一蚀刻制程采用不同的蚀刻剂。在一些实施例中,移除虚设栅极电极层195,然而保留栅极介电层194在栅极沟槽gt1和gt2中。随后,分别形成置换栅极结构rg1和rg2在栅极沟槽gt1和gt2内。举例来说,置换栅极结构rg1和rg2的形成方式可包括毯覆式形成栅极介电层在基材101上、形成一或多个功函数金属层在栅极介电层上、填入金属填充层在一或多个功函数金属层上、以及执行cmp制程以移除在栅极沟槽gt1和gt2外侧的多余的金属填充层、一或多个功函数金属层和栅极介电层。如此一来,每个置换栅极结构rg1和rg2可具有栅极介电层134和金属栅极电极135,其中栅极介电层134围绕在金属栅极电极135的周围。

242.在一些实施例中,栅极介电层134的组成包括高介电常数介电材料,例如金属氧化

物、金属氮化物、金属硅化物、过度金属氧化物、过度金属氮化物、过度金属硅化物、金属氮氧化物、金属铝酸盐(metal aluminate)、硅酸锆(zirconium silicate)、铝酸锆(zirconium aluminate)、或上述的组合。在一些实施例中,栅极介电层134的组成可包括hfo2、hfsio、hfsion、hftao、hftio、hfzro、lao、zro、tio、ta2o5、y2o3、srtio3(sto)、batio3(bto)、bazro、hflao、lasio、alsio、al2o3、si3n4、sion、或上述的组合。在一些实施例中,栅极介电层134可为多层结构,其具有一氧化层(例如介电层)和另一高介电常数介电材料层。

243.金属栅极电极135可包括合适的功函数金属以提供适当的功函数。在一些实施例中,金属栅极电极135可具有一或多个n型功函数金属(n金属)以形成n型晶体管在基材101上。例如,n型功函数金属可包括铝化钛(tial)、氮化铝钛(tialn)、碳氮化钽(tacn)、铪(hf)、锆(zr)、钛(ti)、钽(ta)、铝(al)、金属碳化物(例如、碳化铪(hfc)、碳化锆(zrc)、碳化钛(tic)、碳化铝(alc))、铝化物(aluminide)、或其他合适的材料,但本揭示案不限于此。在一些实施例中,金属栅极电极135可具有一或多个p型功函数金属(p金属)以形成p型晶体管在基材101上。例如,p型功函数金属可包括氮化钛(tin)、氮化钨(wn)、钨(w)、钌(ru)、钯(pd)、铂(pt)、钴(co)、镍(ni)、导电金属氧化物、或其他合适的材料,但本揭示案不限于此。金属栅极电极135中的至少两者是由不同功函数金属所组成以达到适当的功函数。在一些实施例中,金属栅极电极135整体可视为一个功函数金属。

244.接下来,执行非零偏压电浆蚀刻制程以窄化栅极结构rg1和rg2,相较于零偏压,非零偏压可驱动更多的电浆以微缩化栅极结构rg1和rg2。在一些实施例中,非零偏压电浆蚀刻制程使用cl2、o2、bcl3和ar的混合气体并在约25伏特(v)至约1200v的偏压下进行。因为非零偏压所驱动的电浆特性,非零偏压电浆蚀刻在邻近栅极间隔物130的区域(例如,栅极结构rg1和rg2的周边区域)的蚀刻速率小于在远离栅极间隔物130的区域(例如,栅极结构rg1和rg2的中间区域)的蚀刻速率。蚀刻速率的差异使得栅极结构rg1和rg2具有曲形顶表面。进一步详细描述图13a至图13c,在非零偏压电浆蚀刻制程的过程中,相邻于栅极间隔物130的金属栅极电极(例如,金属栅极电极135的周边区域)的移除速率小于远离栅极间隔物130的金属栅极电极(例如,金属栅极电极135的中间区域)的移除速率。除此之外,在非零偏压电浆蚀刻制程的过程中,栅极介电层134的移除速率小于金属栅极电极135的移除速率。换句话说,在非零偏压电浆蚀刻制程中,接近栅极间隔物130的金属栅极电极135的移除量小于远离栅极间隔物130的金属栅极电极135的移除量。除此之外,在非零偏压电浆蚀刻制程的过程中,栅极介电层134的移除量少于金属栅极电极135的移除量。因此,在非零偏压电浆蚀刻制程之后,形成的栅极介电层134的最高处比形成的金属栅极电极135的最高处高。形成的金属栅极电极135具有朝向基材101的凹部,意即,呈现出凹状的形貌。

245.请重新参照图1b,方法m继续步骤s117,在步骤s117中,形成介电覆盖层在各别的栅极结构上。在步骤s117的实施例中,如图13a至图13c所示,形成介电覆盖层136在各别的栅极结构rg1和rg2上,例如可通过沉积制程以沉积介电材料在基材101上、并接着可通过cmp制程以移除栅极沟槽外的介电材料。在一些实施例中,介电覆盖层136可包括氮化硅或其他合适的介电材料。介电覆盖层136的蚀刻选择比不同于栅极间隔物130、cesl132、及/或ild层133,因此可选择性回蚀介电覆盖层136。举例来说,当介电覆盖层136包括氮化硅时,栅极间隔物130、cesl132、及/或ild层133的材料则异于氮化硅。介电覆盖层136可用于定义自对准接触(self-aligned contact,sac)区域,因此可被称为sac结构或sac层。

246.请重新参照图1b,方法m继续步骤s118,在步骤s118中,移除栅极结构的一部分、介电覆盖层的一部分(位于栅极结构的这一部分上方)、以及栅极间隔物与接触蚀刻终止层的一部分(相邻于栅极结构的这一部分),以形成暴露出半导体鳍部的第一开口。在步骤s118的实施例中,如图14a至图14c所示,形成图案化遮罩(未绘出)在栅极结构rg1和rg2、栅极间隔物130、cesl132、和ild层133上。执行一或多道蚀刻制程并将图案化遮罩做为蚀刻遮罩。举例来说,在一些实施例中,执行一或多道蚀刻制程以移除栅极结构rg2的一部分、位于栅极结构rg2上方的介电覆盖层136、以及相邻于栅极结构rg2的栅极间隔物130和cesl132,借此形成第一开口o1,第一开口o1贯穿栅极结构rg2并暴露出半导体鳍部102。换句话说,第一开口o1分隔栅极结构rg2所留下的结构。

247.请重新参照图1b,方法m继续步骤s119,在步骤s119中,毯覆式沉积第二牺牲层在基材上。在步骤s119的实施例中,如图15a至图15c所示,毯覆式沉积牺牲层142在图14a至图14c所示的结构上(即,沉积在栅极结构rg1和rg2、栅极间隔物130、cesl132、ild层133上,以及沉积在第一开口o1中的隔离介电质、间隔物114’和半导体鳍部102上)。在一些实施例中,牺牲层142可包括可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,牺牲层142可能是如氮化硅的介电材料。在一些实施例中,牺牲层142具有的材料不同于半导体鳍部102、ild层133(见图15b)、隔离介电质(见图15b)及/或介电覆盖层136(见图15c)。在一些实施例中,牺牲层142具有约1纳米(nm)至约5nm的厚度t3,例如1、2、3、4或5nm的厚度t3,但本揭示案不限于此。在一些实施例中,牺牲层142可具有多层结构。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或sacvd等以形成牺牲层142。

248.请重新参照图1b,方法m继续步骤s120,在步骤s120中,蚀刻第二牺牲层以形成至少一个第二牺牲间隔物。在步骤s120的实施例中,如图16a至图16c所示,蚀刻牺牲层142以形成牺牲间隔物142a、牺牲间隔物142b和牺牲间隔物142c,其中牺牲间隔物142a形成在第一开口o1中的ild层133的相对侧壁上(见图16b),牺牲间隔物142b形成在第一开口o1中的栅极结构rg2的相对侧壁上(见图16c),以及牺牲间隔物142c形成在第一开口o1中的半导体鳍部102的相对侧上(见图16c)。详细而言,执行非等向性蚀刻制程p5(例如,rie制程或ale制程)以选择性移除牺牲层142的水平部分。留下的牺牲层142的垂直部分形成牺牲间隔物142a、142b和142c。每个牺牲间隔物142a从半导体鳍部102的顶表面沿着第一开口o1中ild层133的侧壁垂直地延伸。每个牺牲间隔物142b从隔离介电质120的顶表面沿着第一开口o1中栅极结构rg2的侧壁垂直地延伸。每个牺牲间隔物142c从隔离介电质120的顶表面沿着第一开口o1中半导体鳍部102的侧壁垂直地延伸。非等向性蚀刻制程p5可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。

249.进一步详细描述图16a至图16c,非等向性蚀刻制程p5对牺牲层142(见图15a至图15c)的蚀刻速率快于对ild层133(见图16b)、隔离介电质120(见图16c)及/或介电覆盖层136(见图16c)的蚀刻速率。牺牲层142比ild层133的蚀刻选择比可大于约10、牺牲层142比隔离介电质120的蚀刻选择比可大于约10、及/或牺牲层142比介电覆盖层136的蚀刻选择比可大于约10。当牺牲层142比ild层133、隔离介电质120及/或介电覆盖层136的蚀刻选择比小于约10时,非等向性蚀刻制程p5可能会明显蚀刻ild层133、隔离介电质及/或介电覆盖层

136,从而对半导体装置产生不良影响。

250.请重新参照图1b,方法m继续步骤s121,在步骤s121中,毯覆式沉积第二间隔层在基材上。在步骤s121的实施例中,如图17a至图17c所示,毯覆式沉积间隔层144在图16a至图16c所示的结构上(即,在栅极结构rg1和rg2、栅极间隔物130、cesl132、ild层133、隔离介电质120、间隔物114’以及牺牲间隔物142a和142b上)。在一些实施例中,间隔层144可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,间隔层144可能是如氧化硅的介电材料。在一些实施例中,间隔层144的材料可能异于牺牲间隔物142a、142b和142c。在一些实施例中,间隔层144可具有多层结构。在一些实施例中,间隔层114具有约1nm至约5nm的厚度t4,例如1、2、3、4或5nm的厚度t4,但本揭示案不限于此。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或peald等来形成间隔层144。

251.请重新参照图1b,方法m继续步骤s122,在步骤s122中,蚀刻第二间隔层以形成第二间隔物。在步骤s122的实施例中,如图18a至图18c所示,蚀刻间隔层144以形成间隔物144a、间隔物144b、以及间隔物144c,其中间隔物144a形成在第一开口o1中的ild层133的相对侧壁上(见图18b),间隔物144b形成在第一开口o1中的栅极结构rg2的相对侧壁上(见图18c),以及间隔物144c形成在第一开口o1中的半导体鳍部102的相对侧上(见图18c)。详细而言,执行非等向性蚀刻制程p6(例如,rie制程或ale制程)以选择性移除间隔层144的水平部分。留下的间隔层144的垂直部分形成间隔物144a、144b和144c。间隔物144a从半导体鳍部102的顶表面沿着牺牲间隔物142a的侧表面垂直地延伸。间隔物144b从隔离介电质120的顶表面沿着牺牲间隔物142b的侧表面垂直地延伸。间隔物144c从隔离介电质120的顶表面沿着牺牲间隔物142c的侧表面垂直地延伸。非等向性蚀刻制程p6可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。

252.进一步详细描述图18a至图18c,非等向性蚀刻制程p6对间隔层144(见图17a至图17c)的蚀刻速率快于对ild层133(见图18b)、牺牲间隔物142a(见图18b)、隔离介电质120(见图18c)、牺牲间隔物142b和142c(见图18c)及/或介电覆盖层136(见图18c)的蚀刻速率。间隔层144比ild层133的蚀刻选择比可大于约10、间隔层144比隔离介电质120的蚀刻选择比可大于约10、间隔层144比牺牲间隔物142a/142b/142c的蚀刻选择比可大于约10、及/或间隔层144比介电覆盖层136的蚀刻选择比可大于约10。当间隔层144比ild层133、隔离介电质120、介电覆盖层136、及/或牺牲间隔物142a/142b/142c的蚀刻选择比小于约10时,非等向性蚀刻制程p6可能会明显蚀刻ild层133、隔离介电质120、介电覆盖层136、及/或牺牲间隔物142a/142b/142c,从而对半导体装置产生不良影响。

253.请重新参照图1b,方法m继续步骤s123,在步骤s123中,移除第二牺牲间隔物以形成第二气隙间隔物。在步骤s123的实施例中,如图19a至图19c所示,执行选择性蚀刻制程p7以选择性移除牺牲间隔物142a、142b和142c(见图18a至图18c)。如此一来,气隙间隔物145a可形成在ild层133和间隔物144a之间。气隙间隔物145b可形成在置换栅极结构rg2和间隔物144b之间。气隙间隔物145c可形成在半导体鳍部102的上部和间隔物144c之间。换句话说,气隙间隔物145a隔开ild层133和间隔物144a。气隙间隔物145b隔开置换栅极结构rg2和间隔物144b。气隙间隔物145c隔开半导体鳍部102的上部和间隔物144c。在气隙间隔物

145a、145b和145c形成之后,间隔物144a和气隙间隔物145a可合称为绝缘结构140a、间隔物144b和气隙间隔物145b可合称为绝缘结构140b、以及间隔物144c和气隙间隔物145c可合称为绝缘结构140c。因为通过移除牺牲间隔物142a、142b和142c(见图18a至图18c)而形成绝缘结构140a、140b和140c,所以气隙间隔物145a、145b、和145c具有原本牺牲间隔物142a、142b和142c的形状。在一些实施例中,部分的半导体鳍部102和部分的基材101暴露于气隙间隔物145a、145b、和145c中。

254.如前所述,牺牲间隔物142a、142b和142c(见图18a至图18c)的厚度在约1nm和约5nm的范围之间。因此,气隙间隔物145a、145b、和145c的厚度也在约1nm和约5nm的范围之间,例如约1、2、3、4或5nm。如果牺牲间隔物142a、142b和142c的厚度小于1nm,因牺牲间隔物142a、142b和142c太窄以至于蚀刻剂难以进入ild层133和间隔物144a之间的空间、难以进入栅极结构rg2和间隔物144b之间的空间、以及难以进入半导体鳍部102和间隔物144c之间的空间,进而影响气隙间隔物145a、145b、和145c的形成。在另一方面,如果牺牲间隔物142a、142b和142c的厚度大于5nm,则形成的气隙间隔物145a、145b、和145c的厚度可能会太宽,以致于后续形成在气隙间隔物145a、145b、和145c上方的材料可能容易流入气隙间隔物145a、145b、和145c的底部,进而影响气隙间隔物145a、145b、和145c的形成。因此,在蚀刻制程p7过程中,牺牲间隔物142a、142b和142c(见图18a至图18c)可能经过蚀刻之后而显露出半导体鳍部102、置换栅极结构rg2和ild层133的垂直侧壁,进而影响气隙间隔物145a、145b、和145c的形成。

255.在本揭示案中,牺牲层142具有例如大于1的介电常数。在另一方面,绝缘结构140a、140b和140c包括气隙间隔物145a、145b、和145c,其中气隙间隔物145a、145b、和145c具有等于1的介电常数且小于牺牲层142的介电常数。因此,绝缘结构140a、140b和140c的等效介电常数因为气隙间隔物145a、145b、和145c的形成而降低。如此一来,绝缘结构140a、140b和140c的整体电容值可降低,进而改善电阻电容延迟(rc delay)亦改善装置表现。除此之外,因为通过移除牺牲间隔物142a、142b和142c而形成气隙间隔物145a、145b、和145c,所以气隙间隔物145a、145b、和145c可具有原本牺牲间隔物142a、142b和142c的形状,因此能轻易调控气隙间隔物145a、145b、和145c的尺寸,并且进一步地调控绝缘结构140a、140b和140c的等效电容。

256.在一些实施例中,蚀刻制程p7可包括选择性等向性蚀刻制程(例如,rie制程或ale制程)。蚀刻制程p7可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当硅用于牺牲间隔物142a、142b和142c(见图18a至图18c)之中时,可使用nh4oh来蚀刻牺牲间隔物142a、142b和142c,但本揭示案不限于此。进一步详细描述图19a至图19c,蚀刻制程p7对牺牲间隔物142a、142b和142c(见图18a至图18c)的蚀刻速率快于对半导体鳍部102、ild层133(见图18b)、间隔物144a(见图18b)、间隔物144b和144c(见图18c)、隔离介电质120(见图18c)、和栅极结构rg2(见图18c)的蚀刻速率。举例来说,牺牲间隔物142a、142b和142c比半导体鳍部102、ild层133、间隔物144a/144b/144c、隔离介电质120、和栅极结构rg2的蚀刻选择比可大于约10。当牺牲间隔物142a、142b和142c比半导体鳍部102、ild层133、间隔物144a/144b/144c、隔离介电质120、和栅极结构rg2的蚀刻选择比小

于约10时,蚀刻制程p7可能会明显蚀刻半导体鳍部102、ild层133、间隔物144a/144b/144c、隔离介电质120、和栅极结构rg2,从而对半导体装置产生不良影响。在一些实施例中,蚀刻制程p7可为等向性蚀刻制程。在一些实施例中,蚀刻制程p7使用的蚀刻剂不同于前一个蚀刻制程p6使用的蚀刻剂。

257.请重新参照图1b,方法m继续步骤s124,在步骤s124中,蚀刻第二间隔物的上部以形成弧形顶角在第二间隔物上。在步骤s124的实施例中,如图20a至图20c所示,蚀刻间隔物144a以形成锥形顶端146a在间隔物144a上、蚀刻间隔物144b以形成锥形顶端146b在间隔物144b上、以及蚀刻间隔物144c以形成锥形顶端146c在间隔物144c上。在图20a至图20c中,对间隔物144a、144b、和144c执行蚀刻制程p8。在一些实施例中,蚀刻制程p8可为电浆蚀刻制程并采用一或多个蚀刻剂。

258.进一步详细描述图20a至图20c,执行非零偏压电浆蚀刻制程以蚀刻间隔物144a、144b、和144c的上部,使得间隔物144a、144b、和144c的顶端呈现锥形。相较于零偏压,非零偏压可驱动更多的电浆以微缩化间隔物144a、144b、和144c。举例来说,非零偏压电浆蚀刻制程一开始以离子轰击的方式来移除间隔物144a、144b、和144c的物质。因此,间隔物144a、144b、和144c的上部的宽度小于间隔物144a、144b、和144c的下部的宽度。换句话说,气隙间隔物145a、145b、和145c的上部的宽度大于气隙间隔物145a、145b、和145c的下部的宽度,因此后续形成的隔离介电质可流进气隙间隔物145a、145b、和145c的上部。如此一来,后续形成的隔离介电质可密封气隙间隔物145a、145b、和145c的上部,并且在后续制程中可避免其他材料填入气隙间隔物145a、145b、和145c中。

259.间隔物144a、144b、和144c的形貌随蚀刻制程p8的制程条件而变(例如蚀刻操作时间或类似者)。蚀刻制程p8可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,非零偏压电浆蚀刻制程使用c4f6和氩气的混合气体并且偏压操作在约50瓦(w)到约1000w的范围之间。如果偏压功率高于约1000w,则电浆可能对ild层133(见图20b)、栅极结构rg2(见图20c)和介电覆盖层136(见图20c)产生预期之外的损害。如果偏压功率低于约50w,则间隔物144a、144b、和144c的锥形顶端可能不足以让后续形成的隔离介电质填入气隙间隔物145a、145b、和145c的上部。

260.请重新参照图1b,方法m继续步骤s125,在步骤s125中,形成第二隔离介电质以填满超出第一开口并密封第二气隙间隔物。在步骤s125的实施例中,如图21a至图21c所示,形成隔离介电质147以填满超出第一开口o1并覆盖第一开口o1中的半导体鳍部102。如前所述,由于气隙间隔物145a、145b、和145c的上部的宽度大于气隙间隔物145a、145b、和145c的下部的宽度,所以隔离介电质147的材料可流进气隙间隔物145a、145b、和145c的上部,从而密封气隙间隔物145a、145b、和145c。相应地,隔离介电质147具有密封部分147a(见图21b)、密封部分147b(见图21c)以及密封部分147c(见图21c),其中密封部分147a(见图21b)位于间隔物144a和ild层133之间、密封部分147b(见图21c)位于间隔物144b和栅极结构rg2之间、以及密封部分147c(见图21c)位于间隔物144c和半导体鳍部102之间。因此,隔离介电质147的密封部分147a、147b、和147c封住气隙间隔物145a、145b、和145c的上端,并且在后续制程中可避免其他材料填入气隙间隔物145a、145b、和145c中。

261.在一些实施例中,隔离介电质147的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fluoride-doped silicate glass,fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质147的形成方式包括hdpcvd,其中使用硅烷(sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质147的形成方式包括sacvd或harp,其中制程气体可包括四乙氧基硅烷(teos)和臭氧(o3)。在一些实施例中,隔离介电质147的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质147可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。接下来,选择性地对隔离介电质147进行热退火制程。在一些实施例中,隔离介电质147的组成材料可相同于间隔物144a、144b、和144c。在一些实施例中,隔离介电质147的组成材料可不同于间隔物144a、144b、和144c。

262.请重新参照图1b,方法m继续步骤s126,在步骤s126中,对第二隔离介电质执行第二平坦化制程。在步骤s126的实施例中,如图22a至图22c所示,执行如cmp的平坦化制程以移除ild层133与栅极沟槽gt1/gt2上多余的隔离介电质147,使得ild层133与栅极沟槽gt1/gt2的顶表面显露出来,而气隙间隔物145a、145b、和145c保持被隔离介电质147的密封部分147a、147b、和147c覆盖住。

263.下文将搭配参照图23a至图36c详细地描述实施例,为了使半导体装置的两个源极/漏极接触件之间电性绝缘,隔离介电质(例如,如图36a所示的隔离介电质157)形成在两个源极/漏极接触件之间。气隙间隔物形成两个源极/漏极接触件之间的隔离介电质的周围,借此降低两个相邻源极/漏极接触件间的电容值。在一些实施例中,两个源极/漏极接触件之间的隔离介电质和形成在隔离介电质上的气隙间隔物可合称为具有气隙的接触件切口(air-inside cut metal-to-drain,air-inside cmd)。

264.请参照图1c,方法m继续步骤s127,在步骤s127中,移除层间介电层的一部分以形成暴露出磊晶源极/漏极结构的第二开口。在步骤s127的实施例中,如图23a至图24c所示,形成图案化遮罩(未绘出)在栅极结构rg1和rg2、栅极间隔物130、cesl132、和ild层133上。执行一或多道蚀刻制程并将图案化遮罩做为蚀刻遮罩。举例来说,在一些实施例中,执行一或多道蚀刻制程以移除位于磊晶源极/漏极结构131上方的ild层133的一部分,借此形成第二开口o2,第二开口o2贯穿ild层133并暴露出对应的磊晶源极/漏极结构131。换句话说,第二开口o2分隔ild层133后续形成的结构。

265.请重新参照图1c,方法m继续步骤s128,在步骤s128中,毯覆式沉积第三牺牲层在基材上。在步骤s128的实施例中,如图25a至图25c所示,毯覆式沉积牺牲层152在图24a至图24c所示的结构上(即,沉积在栅极结构rg1和rg2、栅极间隔物130、cesl132、ild层133上,以及沉积在第二开口o2中的磊晶源极/漏极结构131)。在一些实施例中,牺牲层152可包括可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,牺牲层152可能是如氮化硅的介电材料。在一些实施例中,牺牲层152具有的材料不同于ild层133(见图25b)、介电覆盖层136(见图25b)及/或cesl132(见图25c)。在一些实施例中,牺牲层152具有约1纳米(nm)至约5nm的厚度t5,例如1、2、3、4或5nm的厚度t3,但本揭示案不限于此。在一些实施例中,牺牲层152可具有多层结构。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或sacvd等以形成牺牲层152。

266.请重新参照图1c,方法m继续步骤s129,在步骤s129中,蚀刻第三牺牲层以形成至少一个第三牺牲间隔物。在步骤s129的实施例中,如图26a至图26c所示,蚀刻牺牲层152以形成牺牲间隔物152a和牺牲间隔物152b,其中牺牲间隔物152a形成在第二开口o2中栅极结构rg1的侧壁和栅极结构rg2的侧壁上(见图26b),而牺牲间隔物152b形成在第二开口o2中ild层133的相对侧壁上(见图26c)。详细而言,执行非等向性蚀刻制程p9(例如,rie制程或ale制程)以选择性移除牺牲层152的水平部分。留下的牺牲层152的垂直部分形成牺牲间隔物152a和152b。每个牺牲间隔物152a沿着第二开口o2中栅极结构rg1和rg2的侧壁垂直地延伸。每个牺牲间隔物152b从cesl132的顶表面沿着第二开口o2中ild层133的侧壁垂直地延伸。非等向性蚀刻制程p9可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当硅用于牺牲间隔物152a和152b之中时,可使用nh4oh来蚀刻牺牲层152(见图25a至图25c),但本揭示案不限于此。

267.进一步详细描述图26a至图26c,蚀刻制程p9对牺牲层152(见图25a至图25c)的蚀刻速率快于对ild层133、栅极间隔物130、cesl132及/或介电覆盖层136(见图26b)的蚀刻速率。举例来说,牺牲层152比ild层133、栅极间隔物130、cesl132及/或介电覆盖层136的蚀刻选择比可大于约10。当牺牲层152比ild层133、栅极间隔物130、cesl132及/或介电覆盖层136的蚀刻选择比小于约10时,蚀刻制程p9可能会明显蚀刻ild层133、栅极间隔物130、cesl132及/或介电覆盖层136,从而对半导体装置产生不良影响。

268.请重新参照图1c,方法m继续步骤s130,在步骤s130中,毯覆式沉积第三间隔层在半导体基材上。在步骤s130的实施例中,如图27a至图27c所示,毯覆式沉积间隔层154在图26a至图26c所示的结构上(即,在栅极结构rg1和rg2、栅极间隔物130、cesl132、ild层133、磊晶源极/漏极结构131、以及牺牲间隔物152a和152b上)。在一些实施例中,间隔层154可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,间隔层154可能是如氧化硅的介电材料。在一些实施例中,间隔层154的材料可能异于牺牲间隔物152a和152b。在一些实施例中,间隔层154可具有多层结构。在一些实施例中,间隔层154具有约1nm至约5nm的厚度t6,例如1、2、3、4或5nm的厚度t6,但本揭示案不限于此。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或peald等来形成间隔层154。

269.请重新参照图1c,方法m继续步骤s131,在步骤s131中,蚀刻第三间隔层以形成第三间隔物。在步骤s131的实施例中,如图28a至图28c所示,蚀刻间隔层154以形成间隔物154a以及间隔物154b,其中间隔物154a形成在第二开口o2中栅极结构rg1的侧壁和栅极结构rg2的侧壁上(见图28b),而间隔物154b形成在第二开口o2中ild层133的相对侧壁上(见图28c)。详细而言,执行非等向性蚀刻制程p10(例如,rie制程或ale制程)以选择性移除间隔层154的水平部分。留下的间隔层154的垂直部分形成间隔物154a和154b。间隔物154a沿着第二开口o2中栅极结构rg1和rg2的侧壁垂直地延伸。间隔物154b从cesl132的顶表面沿着第二开口o2中ild层133的侧壁垂直地延伸。非等向性蚀刻制程p10可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。

270.进一步详细描述图28a至图28c,非等向性蚀刻制程p10对间隔层154(见图27a至图27c)的蚀刻速率快于对ild层133、栅极间隔物130、cesl132及/或介电覆盖层136(见图28b)的蚀刻速率。间隔层154比ild层133、栅极间隔物130、cesl132及/或介电覆盖层136(见图28b)的蚀刻选择比可大于约10。当间隔层154比ild层133、栅极间隔物130、cesl132及/或介电覆盖层136(见图28b)的蚀刻选择比小于约10时,非等向性蚀刻制程p10可能会明显蚀刻ild层133、栅极间隔物130、cesl132及/或介电覆盖层136(见图28b),从而对半导体装置产生不良影响。

271.请重新参照图1c,方法m继续步骤s132,在步骤s132中,移除第三牺牲间隔物以形成第三气隙间隔物。在步骤s132的实施例中,如图29a至图29c所示,执行选择性蚀刻制程p11以选择性移除牺牲间隔物152a和152b(见图28a至图28c)。如此一来,气隙间隔物155a可形成在栅极结构rg1/rg2和间隔物154a之间。气隙间隔物155b可形成在ild层133和间隔物154b之间。换句话说,气隙间隔物155a隔开栅极结构rg1/rg2和间隔物154a。气隙间隔物155b隔开ild层133和间隔物154b。在气隙间隔物155a和155b形成之后,间隔物154a和气隙间隔物155a可合称为绝缘结构150a、以及间隔物154b和气隙间隔物155b可合称为绝缘结构150b。因为通过移除牺牲间隔物152a和152b(见图28a至图28c)而形成绝缘结构150a和150b,所以气隙间隔物155a和155b具有原本牺牲间隔物152a和152b的形状。在一些实施例中,部分的cesl132暴露于气隙间隔物155a和155b中。

272.如前所述,牺牲间隔物152a和152b(见图28a至图28c)的厚度在约1nm和约5nm的范围之间。因此,气隙间隔物155a和155b的厚度也在约1nm和约5nm的范围之间,例如约1、2、3、4或5nm。如果牺牲间隔物152a和152b的厚度小于1nm,因牺牲间隔物152a和152b太窄以至于蚀刻剂难以进入栅极结构rg1/rg2和间隔物154a之间的空间、以及难以进入ild层133和间隔物154b之间的空间,进而影响气隙间隔物155a和155b的形成。在另一方面,如果牺牲间隔物152a和152b的厚度大于5nm,则形成的气隙间隔物155a和155b的厚度可能会太宽,以致于后续形成在气隙间隔物155a和155b上方的材料可能容易流入气隙间隔物155a和155b的底部,进而影响气隙间隔物155a和155b的形成。因此,在蚀刻制程p11过程中,牺牲间隔物152a和152b(见图28a至图28c)可能经过蚀刻之后而显露出cesl132和ild层133的垂直侧壁,进而影响气隙间隔物155a和155b的形成。

273.在本揭示案中,牺牲层152具有例如大于1的介电常数。在另一方面,绝缘结构150a和150b包括气隙间隔物155a和155b,其中气隙间隔物155a和155b具有等于1的介电常数且小于牺牲层152的介电常数。因此,绝缘结构150a和150b的等效介电常数因为气隙间隔物155a和155b的形成而降低。如此一来,绝缘结构150a和150b的整体电容值可降低,进而改善电阻电容延迟(rc delay)亦改善装置表现。除此之外,因为通过移除牺牲间隔物152a和152b而形成气隙间隔物155a和155b,所以气隙间隔物155a和155b可具有原本牺牲间隔物152a和152b的形状,因此能轻易调控气隙间隔物155a和155b的尺寸,并且进一步地调控绝缘结构150a和150b的等效电容。

274.在一些实施例中,蚀刻制程p11可包括选择性等向性蚀刻制程(例如,rie制程或ale制程)。蚀刻制程p11可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上

述的列举。在一些实施例中,当硅用于牺牲间隔物152a和152b(见图28a至图28c)之中时,可使用nh4oh来蚀刻牺牲间隔物152a和152b,但本揭示案不限于此。进一步详细描述图29a至图29c,蚀刻制程p11对牺牲间隔物152a和152b(见图28a至图28c)的蚀刻速率快于对cesl132(见图29b)、间隔物154a(见图29b)、ild层133(见图29c)、和间隔物144b(见图29c)的蚀刻速率。举例来说,牺牲间隔物152a和152b比cesl132、间隔物154a/154b、及/或ild层133的蚀刻选择比可大于约10。当牺牲间隔物152a和152b比cesl132、间隔物154a/154b、及/或ild层133的蚀刻选择比小于约10时,蚀刻制程p11可能会明显蚀刻cesl132、间隔物154a/154b、及/或ild层133,从而对半导体装置产生不良影响。在一些实施例中,蚀刻制程p11可为等向性蚀刻制程。在一些实施例中,蚀刻制程p11使用的蚀刻剂不同于前一个蚀刻制程p10使用的蚀刻剂。

275.请重新参照图1c,方法m继续步骤s133,在步骤s133中,蚀刻第三间隔物的上部以形成弧形顶角在第三间隔物上。在步骤s133的实施例中,如图30a至图30c所示,蚀刻间隔物154a以形成锥形顶端156a在间隔物154a上、以及蚀刻间隔物154b以形成锥形顶端156b在间隔物154b上。在图30a至图30c中,对间隔物154a和154b执行蚀刻制程p12。在一些实施例中,蚀刻制程p12可为电浆蚀刻制程并采用一或多个蚀刻剂。

276.进一步详细描述图30a至图30c,执行非零偏压电浆蚀刻制程以蚀刻间隔物154a和154b的上部,使得间隔物154a和154b的顶端呈现锥形。相较于零偏压,非零偏压可驱动更多的电浆以微缩化间隔物154a和154b。举例来说,非零偏压电浆蚀刻制程一开始以离子轰击的方式来移除间隔物154a和154b的物质。因此,间隔物154a和154b的上部的宽度小于间隔物154a和154b的下部的宽度。换句话说,气隙间隔物155a和155b的上部的宽度大于气隙间隔物155a和155b的下部的宽度,因此后续形成的隔离介电质可流进气隙间隔物155a和155b的上部。如此一来,后续形成的隔离介电质可密封气隙间隔物155a和155b的上部,并且在后续制程中可避免其他材料填入气隙间隔物155a和155b中。

277.间隔物154a和154b的形貌随蚀刻制程p12的制程条件而变(例如蚀刻操作时间或类似者)。蚀刻制程p12可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,非零偏压电浆蚀刻制程使用c4f6和氩气的混合气体并且偏压操作在约50瓦(w)到约1000w的范围之间。如果偏压功率高于约1000w,则电浆可能对cesl132和ild层133(见图30c)产生预期之外的损害。如果偏压功率低于约50w,则间隔物154a和154b的锥形顶端可能不足以让后续形成的隔离介电质填入气隙间隔物155a和155b的上部。

278.请重新参照图1c,方法m继续步骤s134,在步骤s134中,形成第三隔离介电质以填满超过第二开口并密封第三气隙间隔物。在步骤s134的实施例中,如图31a至图31c所示,形成隔离介电质157以填满超出第二开口o2并覆盖第二开口o2中的磊晶源极/漏极结构131。如前所述,由于气隙间隔物155a和155b的上部的宽度大于气隙间隔物155a和155b的下部的宽度,所以隔离介电质157的材料可流进气隙间隔物155a和155b的上部,从而密封气隙间隔物155a和155b。相应地,隔离介电质157具有密封部分157a(见图31b)以及密封部分157b(见图31c),其中密封部分157a(见图31b)位于间隔物154a和栅极结构rg1/rg2之间,而密封部分157b(见图31c)位于间隔物154b和ild层133之间。因此,隔离介电质157的密封部分157a

和157b封住气隙间隔物155a和155b的上端,并且在后续制程中可避免其他材料填入气隙间隔物155a和155b中。

279.在一些实施例中,隔离介电质157的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质157的形成方式包括hdpcvd,其中使用硅烷(sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质157的形成方式包括sacvd或harp,其中制程气体可包括四乙氧基硅烷(teos)和臭氧(o3)。在一些实施例中,隔离介电质157的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质157可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。接下来,选择性地对隔离介电质157进行热退火制程。在一些实施例中,隔离介电质157的组成材料可相同于间隔物154a和154b。在一些实施例中,隔离介电质157的组成材料可不同于间隔物154a和154b。

280.请重新参照图1c,方法m继续步骤s135,在步骤s135中,对第三隔离介电质执行第三平坦化制程。在步骤s135的实施例中,如图32a至图32c所示,执行如cmp的平坦化制程以移除ild层133与栅极沟槽gt1/gt2上多余的隔离介电质157,使得ild层133与栅极沟槽gt1/gt2的顶表面显露出来,而气隙间隔物155a和155b保持被隔离介电质157的密封部分157a和157b覆盖住。

281.请重新参照图1c,方法m继续步骤s136,在步骤s136中,形成图案化遮罩在基材上以暴露出层间介电层的一部分,其中层间介电层的这一部分横向相邻于平坦化的第三隔离介电质。在步骤s136的实施例中,如图33a至图33c所示,形成图案化遮罩158在基材101上以暴露出ild层133的一部分,其中ild层133所暴露的这一部分相邻于隔离介电质157。图案化遮罩158的形成方式可包括一系列的沉积、微影图案化和蚀刻制程。微影图案化制程可包括光阻涂覆(例如旋转涂覆)、软烤、光罩对准、曝光、曝光后烘烤、光阻显影、润洗、干燥(例如硬烤)及/或其他适当的操作。蚀刻制程可包括干式蚀刻、湿式蚀刻及/或其他的蚀刻方法(例如反应性离子蚀刻)。

282.请重新参照图1c,方法m继续步骤s137,在步骤s137中,蚀刻图案化遮罩暴露出的平坦化第三隔离介电质,以形成暴露出磊晶源极/漏极结构的第三开口。在步骤s137的实施例中,如图34a至图34c所示,蚀刻图案化遮罩158暴露出的平坦化的隔离介电质133,以形成源极/漏极接触开口o3,其中源极/漏极接触开口o3暴露出磊晶源极/漏极结构131。将图案化遮罩158当作蚀刻遮罩并进行一或多道蚀刻制程。蚀刻制程可包括干式蚀刻、湿式蚀刻及/或其他的蚀刻方法(例如反应性离子蚀刻)。在蚀刻平坦化的隔离介电质133之后,可移除图案化遮罩158。

283.请重新参照图1c,方法m继续步骤s138,在步骤s138中,形成硅化物层在磊晶源极/漏极结构上,接着形成导电材料以填满超出第三开口。在步骤s138的实施例中,如图35a至图35c所示,形成硅化物层160在磊晶源极/漏极结构131上。在一些实施例中,硅化物层160可包括金属硅化物,例如cosi2、tisi2、wsi2、nisi2、mosi2、asi2、ptsi、或类似者。接着,使用适当的沉积技术来沉积导电材料162至在ild层133的源极/漏极接触开口o3中,并填满超出源极/漏极接触开口o3,其中适当的沉积技术例如cvd、ald、peald、pecvd、pvd、电镀、无电

镀、其他方法、或上述的组合。在一些实施例中,导电材料162可包括钨、铝、铜、钴、其他合适的导电材料、或上述的组合。

284.请重新参照图1c,方法m继续步骤s139,在步骤s139中,执行第四平坦化制程以移除层间介电层的顶表面上多余的导电材料,借此形成源极/漏极接触件。在步骤s139的实施例中,如图36a至图36c所示,执行平坦化制程(例如cmp制程)以移除ild层133的顶表面上多余的导电材料162,借此形成源极/漏极接触件162a。

285.下文将搭配参照图37a至图47b详细地描述实施例,为了使ic结构中的多层互连的两个金属线之间电性绝缘,隔离介电质(例如,如图47a和图47b所示的隔离介电质177)设置在两个金属线之间。气隙间隔物形成两个金属线之间的隔离介电质的周围,借此降低两个金属线间的电容值。在一些实施例中,两个金属线之间的隔离介电质和形成在隔离介电质上的气隙间隔物可合称为具有气隙的金属切口(air-inside cut metal)。

286.请参照图1d,方法m继续步骤s140,在步骤s140中,形成金属化层在基材上,金属化层具有至少一个金属线和金属介层窗。在步骤s140的实施例中,如图37a至图37c所示,形成金属化层在如图36a至图36c所示的结构上。金属化层可由多个金属线和相应的金属介层窗(via)所制成。金属化层形成在如图36a至图36c所示晶体管上,并且透过如源极/漏极接触件162a(图36a至图36c)电性连接下方的晶体管。除此之外,半导体装置具有金属间介电结构,在许多制程操作中,金属间介电结构可提供ic的金属化层电性绝缘和结构支撑。金属间介电结构可由多个介电层(亦可被称为金属间介电层)所制成。

287.在图37a至图37c中,金属间介电结构的介电层164和166形成在如图36a至图36c所示的结构上。介电层166形成在介电层164上。在一些实施例中,介电层166及/或166可包括碳掺杂氧化硅、非晶相氟化碳、聚对二甲苯(perylene)、双苯并环丁烯(bis-benzocyclobutenes,bcb)、聚四氟乙烯(polytetrafluoroethylene,ptfe)(铁氟龙)或碳氧化硅聚合物(sioc)。在一些实施例中,极低介电常数(extreme low dielectric constant,elk)包括现有介电材料的多孔形式,例如含氢硅氧烷(hsq)、多孔甲基硅氧烷(msq)、多孔聚芳醚(polyarylether,pae)、多孔silk(一种低介电系数材料的产品)或多孔氧化硅。在一些实施例中,介电层164及/或166可以包括sicn、sico、sio2、sin、sic、alon、上述的组合、或其他合适的材料。在一些实施例中,介电层164及/或166的介电常数小于约2.5。在一些实施例中,介电层164的材料相同于介电层166的材料。在一些实施例中,介电层164的材料不同于介电层166的材料。

288.在图37a至图37c中,金属介层窗165(见图37b)嵌埋在介电层164中,而金属线167(见图37a和图37b)嵌埋在介电层166中并且彼此平行延伸。如图37b所示,金属介层窗165及/或金属线167可包括铜、铂、钌、铝、钽、钨、氮化钽、钛、氮化钛、上述的组合、或其他合适的材料。在一些实施例中,金属线167的顶表面与介电层166的顶表面大致上等高。

289.请参照图1d,方法m继续步骤s141,在步骤s141中,移除金属化层中的金属线的一部分以形成暴露出下方介电层的第四开口。在步骤s141的实施例中,如图38a至图38c所示,形成图案化遮罩(未绘出)在介电层166和金属线167上。执行一或多道蚀刻制程并将图案化遮罩做为蚀刻遮罩。举例来说,在一些实施例中,执行一或多道蚀刻制程以移除金属线167的一部分,借此形成第四开口o4(也可被称为沟槽),第四开口o4形成在金属线167后续形成的结构之间,并且暴露暴露出下方的介电层164。换句话说,第四开口o4分隔金属线167后续

形成的结构。在图38a中,第四开口o4具有尺寸d1,尺寸d1大致上垂直于金属线167的长轴延伸方向并且尺寸d1大于金属线167的宽度w1。在一些实施例中,尺寸d1大致上等于金属线167的宽度w1。

290.请重新参照图1d,方法m继续步骤s142,在步骤s142中,毯覆式沉积第四牺牲层在金属化层上。在步骤s142的实施例中,如图39a至图39c所示,毯覆式沉积牺牲层172在图38a至图38c所示的结构上(即,沉积在介电层164/166和金属线167上)。在一些实施例中,牺牲层172可包括可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,牺牲层172可能是如氮化硅的介电材料。在一些实施例中,牺牲层172具有的材料不同于介电层164。在一些实施例中,牺牲层172具有约1nm至约5nm的厚度t7,例如1、2、3、4或5nm的厚度t7,但本揭示案不限于此。在一些实施例中,牺牲层172可具有多层结构。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或peald等以形成牺牲层172。

291.请重新参照图1d,方法m继续步骤s143,在步骤s143中,蚀刻第四牺牲层以形成第四牺牲间隔物。在步骤s143的实施例中,如图40a至图40c所示,蚀刻牺牲层172以形成牺牲间隔物172a和牺牲间隔物172b,其中牺牲间隔物172a形成在第四开口o4中金属线167的相对侧壁上(见图40b),而牺牲间隔物172b形成在第四开口o4中介电层166的相对侧壁上(见图40c)。详细而言,执行非等向性蚀刻制程p13(例如,rie制程或ale制程)以选择性移除牺牲层172的水平部分。留下的牺牲层172的垂直部分形成牺牲间隔物172a和172b。每个牺牲间隔物172a从介电层164的顶表面沿着第四开口o4中金属线167的侧壁垂直地延伸。每个牺牲间隔物172b从介电层164的顶表面沿着第四开口o4中介电层166的侧壁垂直地延伸。

292.非等向性蚀刻制程p13可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当氮化硅用于牺牲间隔物172a和牺牲间隔物172b之中时,可使用nh4oh来蚀刻牺牲层172(见图39a至图39c),但本揭示案不限于此。进一步详细描述图40a至图40c,蚀刻制程p13对牺牲层172(见图39a至图39c)的蚀刻速率快于对介电层164和金属线167的蚀刻速率。举例来说,牺牲层172比介电层164及/或金属线167的蚀刻选择比可大于约10。当牺牲层172比介电层164及/或金属线167的蚀刻选择比小于约10时,蚀刻制程p13可能会明显蚀刻介电层164及/或金属线167,从而对半导体装置产生不良影响。

293.请重新参照图1d,方法m继续步骤s144,在步骤s144中,毯覆式沉积第四间隔层在基材上。在步骤s144的实施例中,如图41a至图41c所示,毯覆式沉积间隔层174在图40a至图40c所示的结构上(即,介电层164、金属线167以及牺牲间隔物172a和172b上)。在一些实施例中,间隔层174的材料可能异于牺牲间隔物172a和172b。在一些实施例中,间隔层174可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,间隔层174可能是如氧化硅的介电材料。在一些实施例中,间隔层174可具有多层结构。在一些实施例中,间隔层174具有约1nm至约5nm的厚度t8,例如1、2、3、4或5nm的厚度t8,但本揭示案不限于此。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或peald等来形成间隔层174。

294.请重新参照图1d,方法m继续步骤s145,在步骤s145中,蚀刻第四间隔层以形成第四间隔物。在步骤s145的实施例中,如图42a至图42c所示,蚀刻间隔层174以形成间隔物

174a以及间隔物174b,其中间隔物174a形成在第四开口o4中金属线167的相对侧壁上(见图42b),而间隔物174b形成在第四开口o4中介电层166的相对侧壁上(见图42c)。详细而言,执行非等向性蚀刻制程p14(例如,rie制程或ale制程)以选择性移除间隔层174的水平部分。留下的间隔层174的垂直部分形成间隔物174a和174b。间隔物174a从介电层164的顶表面沿着第四开口o4中金属线167的侧壁垂直地延伸。间隔物174b从介电层164的顶表面沿着第四开口o4中介电层166的侧壁垂直地延伸。非等向性蚀刻制程p14可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。

295.进一步详细描述图42a至图42c,非等向性蚀刻制程p14对间隔层174(见图41a至图41c)的蚀刻速率快于对介电层164、金属线167、和牺牲间隔物172a/172b的蚀刻速率。间隔层174比介电层164、金属线167、和牺牲间隔物172a/172b的蚀刻选择比可大于约10。当间隔层174比介电层164、金属线167、和牺牲间隔物172a/172b的蚀刻选择比小于约10时,非等向性蚀刻制程p14可能会明显蚀刻介电层164、金属线167、和牺牲间隔物172a/172b,从而对半导体装置产生不良影响。

296.请重新参照图1d,方法m继续步骤s146,在步骤s146中,移除第四牺牲间隔物以形成第四气隙间隔物。在步骤s146的实施例中,如图43a至图43c所示,执行选择性蚀刻制程p15以选择性移除牺牲间隔物172a和172b(见图42a至图42c)。如此一来,气隙间隔物175a可形成在金属线167和间隔物174a之间。气隙间隔物175b可形成在介电层166和间隔物174b之间。换句话说,气隙间隔物175a隔开金属线167和间隔物174a。气隙间隔物175b隔开介电层166和间隔物174b。在气隙间隔物175a和175b形成之后,间隔物174a和气隙间隔物175a可合称为绝缘结构170a、以及间隔物174b和气隙间隔物175b可合称为绝缘结构170b。因为通过移除牺牲间隔物172a和172b(见图42a至图42c)而形成绝缘结构170a和170b,所以气隙间隔物175a和175b具有原本牺牲间隔物172a和172b的形状。在一些实施例中,部分的介电层164暴露于气隙间隔物175a和175b中。

297.如前所述,牺牲间隔物172a和172b(见图42a至图42c)的厚度在约1nm和约5nm的范围之间。因此,气隙间隔物175a和175b的厚度也在约1nm和约5nm的范围之间,例如约1、2、3、4或5nm。如果牺牲间隔物172a和172b的厚度小于1nm,因牺牲间隔物172a和172b太窄以至于蚀刻剂难以进入金属线167、介电层166和间隔物174a/174b之间的空间,进而影响气隙间隔物175a和175b的形成。在另一方面,如果牺牲间隔物172a和172b的厚度大于5nm,则形成的气隙间隔物175a和175b的厚度可能会太宽,以致于后续形成在气隙间隔物175a和175b上方的材料可能容易流入气隙间隔物175a和175b的底部,进而影响气隙间隔物175a和175b的形成。因此,在蚀刻制程p15过程中,牺牲间隔物172a和172b(见图42a至图42c)可能经过蚀刻之后而显露出金属线167和介电层166的垂直侧壁,进而影响气隙间隔物175a和175b的形成。

298.在本揭示案中,牺牲层172具有例如大于1的介电常数。在另一方面,绝缘结构170a和170b包括气隙间隔物175a和175b,其中气隙间隔物175a和175b具有等于1的介电常数且小于牺牲层172的介电常数。因此,绝缘结构170a和170b的等效介电常数因为气隙间隔物175a和175b的形成而降低。如此一来,绝缘结构170a和170b的整体电容值可降低,进而改善

电阻电容延迟(rc delay)亦改善装置表现。除此之外,因为通过移除牺牲间隔物172a和172b而形成气隙间隔物175a和175b,所以气隙间隔物175a和175b可具有原本牺牲间隔物172a和172b的形状,因此能轻易调控气隙间隔物175a和175b的尺寸,并且进一步地调控绝缘结构170a和170b的等效电容。

299.在一些实施例中,蚀刻制程p15可包括选择性等向性蚀刻制程(例如,rie制程或ale制程)。蚀刻制程p11可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当硅用于牺牲间隔物172a和172b(见图42a至图42c)之中时,可使用nh4oh来蚀刻牺牲间隔物172a和172b,但本揭示案不限于此。进一步详细描述图43a至图43c,蚀刻制程p15对牺牲间隔物172a和172b(见图42a至图42c)的蚀刻速率快于对介电层164、金属线167、和间隔物174a/174b的蚀刻速率。举例来说,牺牲间隔物172a和172b比介电层164、金属线167、及/或间隔物174a/174b的蚀刻选择比可大于约10。当牺牲间隔物172a和172b比介电层164、金属线167、及/或间隔物174a/174b的蚀刻选择比小于约10时,蚀刻制程p15可能会明显蚀刻介电层164、金属线167、及/或间隔物174a/174b,从而对半导体装置产生不良影响。在一些实施例中,蚀刻制程p15可为等向性蚀刻制程。在一些实施例中,蚀刻制程p15使用的蚀刻剂不同于前一个蚀刻制程p14使用的蚀刻剂。

300.请重新参照图1d,方法m继续步骤s147,在步骤s147中,蚀刻第四间隔物的上部以形成弧形顶角在第四间隔物上。在步骤s147的实施例中,如图44a至图44c所示,蚀刻间隔物174a和174b以形成锥形顶端176a和176b在间隔物174a和174b上。在图44a至图44c中,对间隔物174a和174b执行蚀刻制程p16。在一些实施例中,蚀刻制程p16可为电浆蚀刻制程并采用一或多个蚀刻剂。

301.进一步详细描述图44a至图44c,执行非零偏压电浆蚀刻制程以蚀刻间隔物174a和174b的上部,使得间隔物174a和174b的顶端呈现锥形。相较于零偏压,非零偏压可驱动更多的电浆以微缩化间隔物174a和174b。举例来说,非零偏压电浆蚀刻制程一开始以离子轰击的方式来移除间隔物174a和174b的物质。因此,间隔物174a和174b的上部的宽度小于间隔物174a和174b的下部的宽度。换句话说,气隙间隔物175a和175b的上部的宽度大于气隙间隔物175a和175b的下部的宽度,因此后续形成的隔离介电质可流进气隙间隔物175a和175b的上部。如此一来,后续形成的隔离介电质可密封气隙间隔物175a和175b的上部,并且在后续制程中可避免其他材料填入气隙间隔物175a和175b中。

302.间隔物174a和174b的形貌随蚀刻制程p16的制程条件而变(例如蚀刻操作时间或类似者)。蚀刻制程p16可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,非零偏压电浆蚀刻制程使用c4f6和氩气的混合气体并且偏压操作在约50瓦(w)到约1000w的范围之间。如果偏压功率高于约1000w,则电浆可能对介电层164和金属线167产生预期之外的损害。如果偏压功率低于约50w,则间隔物174a和174b的锥形顶端可能不足以让后续形成的隔离介电质填入气隙间隔物175a和175b的上部。

303.请重新参照图1d,方法m继续步骤s148,在步骤s148中,形成第四隔离介电质以填

满超过第四开口并密封第四气隙间隔物。在步骤s148的实施例中,如图45a至图45c所示,形成隔离介电质177以填满超出第四开口o4并覆盖介电层166和金属线167。如前所述,由于气隙间隔物175a和175b的上部的宽度大于气隙间隔物175a和175b的下部的宽度,所以隔离介电质177的材料可流进气隙间隔物175a和175b的上部,从而密封气隙间隔物175a和175b。相应地,隔离介电质177具有密封部分177a以及密封部分177b,其中密封部分177a嵌埋于间隔物174a和金属线167之间,而密封部分177b嵌埋于间隔物174b和介电层166之间。因此,隔离介电质177的密封部分177a和177b封住气隙间隔物175a和175b的上端,并且在后续制程中可避免其他材料填入气隙间隔物175a和175b中。

304.在一些实施例中,隔离介电质177的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质157的形成方式包括hdpcvd,其中使用硅烷(sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质157的形成方式包括sacvd或harp,其中制程气体可包括四乙氧基硅烷(teos)和臭氧(o3)。在一些实施例中,隔离介电质177的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质177可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。接下来,选择性地对隔离介电质177进行热退火制程。在一些实施例中,隔离介电质177的组成材料可相同于间隔物174a和174b。在一些实施例中,隔离介电质177的组成材料可不同于间隔物174a和174b。

305.请重新参照图1d,方法m继续步骤s149,在步骤s149中,对第四隔离介电质执行第五平坦化制程。在步骤s149的实施例中,如图46a至图46c所示,执行如cmp的平坦化制程以移除介电层166和金属线167上多余的隔离介电质177,使得介电层166和金属线167的顶表面显露出来,而气隙间隔物175a和175b保持被隔离介电质177的密封部分177a和177b覆盖住。

306.请重新参照图1d,方法m继续步骤s150,在步骤s150中,形成至少一个金属介层窗在介电层和金属线上。在步骤s150的实施例中,如图47a至图47b所示,形成介电层184在图46a至图46c的结构上。接着,形成金属介层窗185嵌埋于介电层184中并电性连接金属线167。在一些实施例中,介电层184可包括碳掺杂氧化硅、非晶相氟化碳、聚对二甲苯(perylene)、双苯并环丁烯(bis-benzocyclobutenes,bcb)、聚四氟乙烯(polytetrafluoroethylene,ptfe)(铁氟龙)或碳氧化硅聚合物(sioc)。在一些实施例中,极低介电常数(elk)包括现有介电材料的多孔形式,例如含氢硅氧烷(hsq)、多孔甲基硅氧烷(msq)、多孔聚芳醚(polyarylether,pae)、多孔silk(一种低介电系数材料的产品)或多孔氧化硅。在一些实施例中,介电层184可以包括sicn、sico、sio2、sin、sic、alon、上述的组合、或其他合适的材料。在一些实施例中,介电层184的介电常数小于约2.5。在一些实施例中,介电层184的材料相同于介电层166的材料。在一些实施例中,介电层184的材料不同于介电层166的材料。在一些实施例中,金属介层窗185可包括铜、铂、钌、铝、钽、钨、氮化钽、钛、氮化钛、上述的组合、或其他合适的材料。

307.下文将搭配参照图48a至图55b详细地描述实施例,当气隙间隔物(例如,如图55a和图55b所示的气隙间隔物275)设置于多层互连结构中的两个金属线之间并且气隙间隔物

围绕在隔离介电质(例如,如图55a和图55b所示的隔离介电质277)的周围时,上述结构的气隙间隔物大致上相同于图47a至图47b所示的气隙间隔物。上述结构的气隙间隔物与图47a至图47b所示的气隙间隔物之间的差异在于气隙间隔物的形成时机在隔离介电质形成之后。

308.图48a至图55b根据本揭示案的一些实施例绘示制造半导体装置200的其中一个阶段的示意图。图48a至图55a绘示沿图37a至图46a的线b4-b4’的截面图。图48b至图55b绘示沿图37a至图46a的线c4-c4’的截面图。半导体装置200在图48a和图48b之前的结构的形成方式大致上相同于半导体装置100在图37a至图39c中方法m的步骤s140至s142的操作方式,因此可参照前述的段落描述而在此不再详述。例如,介电层264和266、金属介层窗265、金属线267、以及牺牲层272的材料和制程大致上相同于图37a至图39c绘示的介电层164和166、金属介层窗165、金属线167、以及牺牲层172的材料和制程,因此可参照前述的段落描述故在此不再详述。

309.请参照图48a至图48b。嵌埋金属介层窗265(见图48a)于介电层264中。形成介电层266在介电层264和金属介层窗265上。移除金属线267的一部分以形成暴露出下方介电层264的第五开口o5,第五开口o5形成在金属线267所留下的结构之间。换句话说,第五开口o5分隔金属线267所留下的各个结构。毯覆式沉积牺牲层272在介电层266、第五开口o5的侧壁、以及在第五开口o5中的介电层264的顶表面上。接下来,毯覆式沉积间隔层274在牺牲层272上。间隔层274的材料不同于牺牲层272的材料。在一些实施例中,牺牲层272具有约1nm至约5nm的厚度,例如1、2、3、4或5nm的厚度,但本揭示案不限于此。在一些实施例中,间隔层274具有约1nm至约5nm的厚度,例如1、2、3、4或5nm的厚度,但本揭示案不限于此。间隔层274可包括氧化硅、氮化硅、氮氧化硅、sicn、sic

x

oynz、其他合适的材料、或上述的组合。举例来说,间隔层274可能是如氧化硅的介电材料。在一些实施例中,间隔层274可具有多层结构。在一些实施例中,可使用沉积技术,例如pecvd、lpcvd、或sacvd等以形成间隔层274。

310.请参照图49a至图49b。形成隔离介电质277在间隔层274上以填满超出第五开口o5。在一些实施例中,隔离介电质277的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fluoride-doped silicate glass,fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质277的形成方式包括hdpcvd,其中使用硅烷(sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质277的形成方式包括sacvd或harp,其中制程气体可包括四乙氧基硅烷(teos)和臭氧(o3)。在一些实施例中,隔离介电质277的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质277可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。接下来,选择性地对隔离介电质277进行热退火制程。在一些实施例中,隔离介电质277的组成材料可相同于间隔层274。在一些实施例中,隔离介电质147的组成材料可不同于间隔层274。

311.请参照图50a至图50b。执行如cmp的平坦化制程以移除第五开口o5上多余的隔离介电质277、间隔层274和牺牲层272,使得介电层266显露出来。

312.请参照图51a至图51b。执行蚀刻制程以选择性移除牺牲层272的垂直部分,借此形成气隙间隔物275在金属线267和间隔层274之间,以及在介电层266和间隔层274之间。换句

话说,气隙间隔物275分隔金属线267和间隔层274。在气隙间隔物275形成之后,间隔层274和气隙间隔物275可合称为绝缘结构270。因为通过移除牺牲层272的垂直部分(见图50a和图50b)而形成绝缘结构270,所以气隙间隔物275具有原本牺牲层272的垂直部分的形状。在一些实施例中,部分的介电层264暴露于气隙间隔物275中。

313.如前所述,牺牲层272(见图48a至图48b)的厚度在约1nm和约5nm的范围之间。因此,气隙间隔物275的厚度也在约1nm和约5nm的范围之间,例如约1、2、3、4或5nm。如果牺牲层272的厚度小于1nm,因牺牲层272太窄以至于蚀刻剂难以进入金属线267、介电层266和间隔层274之间的空间,进而影响气隙间隔物275的形成。在另一方面,如果牺牲层272的厚度大于5nm,则形成的气隙间隔物275的厚度可能会太宽,以致于后续形成在气隙间隔物275上方的材料可能容易流入气隙间隔物275的底部,进而影响气隙间隔物275的形成。因此,在蚀刻制程过程中,牺牲层272的垂直部分(见图50a至图50b)可能经过蚀刻之后而显露出金属线267和介电层266的垂直侧壁,进而影响气隙间隔物275的形成。

314.在本揭示案中,牺牲层272具有例如大于1的介电常数。在另一方面,绝缘结构270包括气隙间隔物275,其中气隙间隔物275具有等于1的介电常数且小于牺牲层272的介电常数。因此,绝缘结构270的等效介电常数因为气隙间隔物275的形成而降低。如此一来,绝缘结构270的整体电容值可降低,进而改善电阻电容延迟(rc delay)亦改善装置表现。

315.在一些实施例中,对牺牲层272的蚀刻制程可包括非等向性蚀刻制程(例如,rie制程或ale制程)。对牺牲层272的蚀刻制程可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当氮化硅用于牺牲层272之中时,可使用磷酸(h3po4)来蚀刻牺牲层272的垂直部分(见图50a至图50b),但本揭示案不限于此。进一步详细描述图51a至图51b,蚀刻制程对牺牲层272(见图50a至图50b)的蚀刻速率快于对介电层264、金属线267、及/或间隔层274的蚀刻速率。举例来说,牺牲层272比介电层264、金属线267、及/或间隔层274的蚀刻选择比可大于约10。当牺牲层272比介电层264、金属线267、及/或间隔层274的蚀刻选择比小于约10时,蚀刻制程可能会明显蚀刻介电层264、金属线267、及/或间隔层274,从而对半导体装置产生不良影响。在一些实施例中,针对牺牲层272的蚀刻制程可为等向性蚀刻制程。

316.请参照图52a至图52b。对间隔层274执行蚀刻制程,通过蚀刻间隔层274的上部以形成锥形顶端276在间隔层274上。在一些实施例中,蚀刻制程可为电浆蚀刻制程并采用一或多个蚀刻剂。

317.进一步详细描述图52a至图52b,执行非零偏压电浆蚀刻制程以蚀刻间隔层274的上部,使得间隔层274的顶端呈现锥形。相较于零偏压,非零偏压可驱动更多的电浆以微缩化间隔层274。举例来说,非零偏压电浆蚀刻制程一开始以离子轰击的方式来移除间隔层274的物质。因此,间隔层274的上部的宽度小于间隔层274的下部的宽度。换句话说,气隙间隔物275的上部的宽度大于气隙间隔物275的下部的宽度,因此后续形成的隔离介电质可流进气隙间隔物275的上部。如此一来,后续形成的隔离介电质可密封气隙间隔物275的上部,并且在后续制程中可避免其他材料填入气隙间隔物275中。

318.间隔层274的形貌随蚀刻制程的制程条件而变(例如蚀刻操作时间或类似者)。针

对间隔层274的蚀刻制程可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,非零偏压电浆蚀刻制程使用c4f6和氩气的混合气体并且偏压操作在约50瓦(w)到约1000w的范围之间。如果偏压功率高于约1000w,则电浆可能对介电层264和金属线267产生预期之外的损害。如果偏压功率低于约50w,则间隔层274的锥形顶端可能不足以让后续形成的隔离介电质填入气隙间隔物275的上部。

319.请参照图53a至图53b。形成隔离介电质278以填满超出第五开口o5并密封气隙间隔物275。如前所述,由于气隙间隔物275的上部的宽度大于气隙间隔物275的下部的宽度,所以隔离介电质278的材料可流进气隙间隔物275的上部,从而密封气隙间隔物275。相应地,隔离介电质278具有密封部分278s位于间隔层274、介电层266和金属线267之间。因此,隔离介电质278的密封部分278s封住气隙间隔物275的上端,并且在后续制程中可避免其他材料填入气隙间隔物275中。

320.在一些实施例中,隔离介电质278的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质278的形成方式包括hdpcvd,其中使用硅烷(sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质278的形成方式包括sacvd或harp,其中制程气体可包括四乙氧基硅烷(teos)和臭氧(o3)。在一些实施例中,隔离介电质278的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质278可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。接下来,选择性地对隔离介电质278进行热退火制程。在一些实施例中,隔离介电质278的组成材料可相同于间隔层274、介电层266及/或隔离介电质277。在一些实施例中,隔离介电质278的组成材料可不同于间隔层274、介电层266及/或隔离介电质277。

321.请参照图54a至图55b。执行如cmp的平坦化制程以移除多余的隔离介电质278,使得介电层266和金属线267的顶表面显露出来,而气隙间隔物275保持被隔离介电质278的密封部分278s覆盖住。

322.请参照图55a至图55b。形成介电层284在如图54a和图54b所示的结构上。接下来,形成金属介层窗285嵌埋于介电层284中并电性连接金属线267。在一些实施例中,介电层284可包括碳掺杂氧化硅、非晶相氟化碳、聚对二甲苯(perylene)、双苯并环丁烯(bis-benzocyclobutenes,bcb)、聚四氟乙烯(polytetrafluoroethylene,ptfe)(铁氟龙)或碳氧化硅聚合物(sioc)。在一些实施例中,极低介电常数(elk)包括现有介电材料的多孔形式,例如含氢硅氧烷(hsq)、多孔甲基硅氧烷(msq)、多孔聚芳醚(polyarylether,pae)、多孔silk(一种低介电系数材料的产品)或多孔氧化硅。在一些实施例中,介电层284可以包括sicn、sico、sio2、sin、sic、alon、上述的组合、或其他合适的材料。在一些实施例中,介电层284的介电常数小于约2.5。在一些实施例中,介电层284的材料相同于介电层266的材料。在一些实施例中,介电层284的材料不同于介电层266的材料。在一些实施例中,金属介层窗285可包括铜、铂、钌、铝、钽、钨、氮化钽、钛、氮化钛、上述的组合、或其他合适的材料。

323.下文将搭配参照图56a至图61b详细地描述实施例,当气隙间隔物(例如,如图61a

和图61b所示的气隙间隔物375)设置于多层互连结构中的两个金属线之间并且气隙间隔物围绕在隔离介电质(例如,如图61a和图61b所示的隔离介电质377)的周围时,上述结构的气隙间隔物大致上相同于图55a至图55b所示的气隙间隔物。上述结构的气隙间隔物与图55a至图55b所示的气隙间隔物之间的差异在于气隙间隔物形成在物理性间隔物和隔离介电质之间并且隔离介电质的外侧壁暴露于气隙间隔物中。

324.图56a至图61b根据本揭示案的一些实施例绘示制造半导体装置300的其中一个阶段的示意图。图56a至图61a绘示沿图37a至图46a的线b4-b4’的截面图。图56b至图61b绘示沿图37a至图46a的线c4-c4’的截面图。半导体装置300在图56a和图56b之前的结构的形成方式大致上相同于半导体装置200在图48a至图50b的形成方式,因此可参照前述的段落描述而在此不再详述。例如,介电层364和366、金属介层窗365、金属线367、牺牲层372、间隔层374、以及隔离介电质377的材料和制程大致上相同于图48a至图50b绘示的介电层264和266、金属介层窗265、金属线267、牺牲层272、间隔层274、以及隔离介电质277的材料和制程,因此可参照前述的段落描述故在此不再详述。

325.本实施例与图48a至图50b的实施例之间的差异在于牺牲层372形成在间隔层374上。请参照图56a至图56b。嵌埋金属介层窗365(见图56a)于介电层364中。形成介电层366在介电层364和金属介层窗365上。移除金属线367的一部分以形成暴露出下方介电层364的第六开口o6,第六开口o6形成在金属线367所留下的结构之间。换句话说,第六开口o6分隔金属线367所留下的各个结构。毯覆式沉积间隔层374在介电层366、第六开口o6的侧壁、以及在第六开口o6中的介电层364的顶表面上。接下来,毯覆式沉积牺牲层372在间隔层374上。然后,形成隔离介电质377在第六开口o6中的牺牲层372上。在一些实施例中,牺牲层372的材料不同于间隔层374和隔离介电质377的材料。在一些实施例中,牺牲层372具有约1nm至约5nm的厚度,例如1、2、3、4或5nm的厚度,但本揭示案不限于此。在一些实施例中,间隔层374具有约1nm至约5nm的厚度,例如1、2、3、4或5nm的厚度,但本揭示案不限于此。

326.请参照图57a至图57b。执行蚀刻制程以选择性移除牺牲层372的垂直部分,借此形成气隙间隔物375在间隔层374和隔离介电质377之间。换句话说,气隙间隔物375分隔间隔层374和隔离介电质377。在气隙间隔物375形成之后,间隔层374和气隙间隔物375可合称为绝缘结构370。因为通过移除牺牲层372的垂直部分(见图56a和图56b)而形成绝缘结构370,所以气隙间隔物375具有原本牺牲层372的垂直部分的形状。在一些实施例中,间隔层374的横向部分暴露于气隙间隔物375中。

327.牺牲层372的厚度可在约1nm和约5nm的范围之间。因此,气隙间隔物375的厚度也可在约1nm和约5nm的范围之间,例如约1、2、3、4或5nm。如果牺牲层372的厚度小于1nm,因牺牲层372太窄以至于蚀刻剂难以进入间隔层374和隔离介电质377之间的空间,进而影响气隙间隔物375的形成。在另一方面,如果牺牲层372的厚度大于5nm,则形成的气隙间隔物375的厚度可能会太宽,以致于后续形成在气隙间隔物375上方的材料可能容易流入气隙间隔物375的底部,进而影响气隙间隔物375的形成。因此,在蚀刻制程过程中,牺牲层372的垂直部分(见图56a至图56b)可能经过蚀刻之后而显露出间隔层374和隔离介电质377的垂直侧壁,进而影响气隙间隔物375的形成。

328.在本揭示案中,牺牲层372具有例如大于1的介电常数。在另一方面,绝缘结构370包括气隙间隔物375,其中气隙间隔物375具有等于1的介电常数且小于牺牲层372的介电常

数。因此,绝缘结构370的等效介电常数因为气隙间隔物375的形成而降低。如此一来,绝缘结构370的整体电容值可降低,进而改善电阻电容延迟(rc delay)亦改善装置表现。

329.在一些实施例中,对牺牲层372的蚀刻制程可包括非等向性蚀刻制程(例如,rie制程或ale制程)。对牺牲层372的蚀刻制程可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,当硅用于牺牲层372之中时,可使用nh4oh来蚀刻牺牲层372的垂直部分(见图56a至图56b),但本揭示案不限于此。进一步详细描述图57a至图57b,蚀刻制程对牺牲层372(见图56a至图56b)的蚀刻速率快于对介电层364、金属线367、及/或间隔层374的蚀刻速率。举例来说,牺牲层372比介电层364、金属线367、及/或间隔层374的蚀刻选择比可大于约10。当牺牲层372比介电层364、金属线367、及/或间隔层374的蚀刻选择比小于约10时,蚀刻制程可能会明显蚀刻介电层364、金属线367、及/或间隔层374,从而对半导体装置产生不良影响。在一些实施例中,针对牺牲层372的蚀刻制程可为等向性蚀刻制程。

330.请参照图58a至图58b。对间隔层374执行蚀刻制程,通过蚀刻间隔层374的上部以形成锥形顶端376在间隔层374上。在一些实施例中,蚀刻制程可为电浆蚀刻制程并采用一或多个蚀刻剂。

331.进一步详细描述图58a至图58b,执行非零偏压电浆蚀刻制程以蚀刻间隔层374的上部,使得间隔层374的顶端呈现锥形。相较于零偏压,非零偏压可驱动更多的电浆以微缩化间隔层374。举例来说,非零偏压电浆蚀刻制程一开始以离子轰击的方式来移除间隔层374的物质。因此,间隔层374的上部的宽度小于间隔层374的下部的宽度。换句话说,气隙间隔物375的上部的宽度大于气隙间隔物375的下部的宽度,因此后续形成的隔离介电质可流进气隙间隔物375的上部。如此一来,后续形成的隔离介电质可密封气隙间隔物375的上部,并且在后续制程中可避免其他材料填入气隙间隔物375中。

332.间隔层374的形貌随蚀刻制程的制程条件而变(例如蚀刻操作时间或类似者)。针对间隔层374的蚀刻制程可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本揭示案不限于上述的列举。在一些实施例中,非零偏压电浆蚀刻制程使用c4f6和氩气的混合气体并且偏压操作在约50瓦(w)到约1000w的范围之间。如果偏压功率高于约1000w,则电浆可能对介电层364和金属线367产生预期之外的损害。如果偏压功率低于约50w,则间隔层374的锥形顶端可能不足以让后续形成的隔离介电质填入气隙间隔物375的上部。

333.请参照图59a至图59b。形成隔离介电质378以填满超出第六开口o6并密封气隙间隔物375。如前所述,由于气隙间隔物375的上部的宽度大于气隙间隔物375的下部的宽度,所以隔离介电质378的材料可流进气隙间隔物375的上部,从而密封气隙间隔物375。相应地,隔离介电质378具有密封部分378s位于间隔层374、介电层366和金属线367之间。因此,隔离介电质378的密封部分378s封住气隙间隔物375的上端,并且在后续制程中可避免其他材料填入气隙间隔物375中。

334.在一些实施例中,隔离介电质378的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅

酸盐玻璃(fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质378的形成方式包括hdpcvd,其中使用硅烷(sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质378的形成方式包括sacvd或harp,其中制程气体可包括四乙氧基硅烷(teos)和臭氧(o3)。在一些实施例中,隔离介电质378的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质378可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。接下来,选择性地对隔离介电质378进行热退火制程。在一些实施例中,隔离介电质378的组成材料可相同于间隔层374、介电层366及/或隔离介电质377。在一些实施例中,隔离介电质378的组成材料可不同于间隔层374、介电层366及/或隔离介电质377。

335.请参照图60a至图60b。执行如cmp的平坦化制程以移除多余的隔离介电质378,使得介电层366和金属线367的顶表面显露出来,而气隙间隔物375保持被隔离介电质378的密封部分378s覆盖住。

336.请参照图61a至图61b。形成介电层384在如图60a和图60b所示的结构上。接下来,形成金属介层窗385嵌埋于介电层384中并电性连接金属线367。在一些实施例中,介电层384可包括碳掺杂氧化硅、非晶相氟化碳、聚对二甲苯(perylene)、双苯并环丁烯(bis-benzocyclobutenes,bcb)、聚四氟乙烯(polytetrafluoroethylene,ptfe)(铁氟龙)或碳氧化硅聚合物(sioc)。在一些实施例中,极低介电常数(elk)包括现有介电材料的多孔形式,例如含氢硅氧烷(hsq)、多孔甲基硅氧烷(msq)、多孔聚芳醚(polyarylether,pae)、多孔silk(一种低介电系数材料的产品)或多孔氧化硅。在一些实施例中,介电层384可以包括sicn、sico、sio2、sin、sic、alon、上述的组合、或其他合适的材料。在一些实施例中,介电层384的介电常数小于约2.5。在一些实施例中,介电层384的材料相同于介电层366的材料。在一些实施例中,介电层384的材料不同于介电层366的材料。在一些实施例中,金属介层窗385可包括铜、铂、钌、铝、钽、钨、氮化钽、钛、氮化钛、上述的组合、或其他合适的材料。

337.下文将搭配参照图62a至图66b详细地描述实施例,当气隙间隔物(例如,如图66a和图66b所示的气隙间隔物475)设置于多层互连结构中的两个金属线之间并且气隙间隔物围绕在隔离介电质(例如,如图66a和图66b所示的隔离介电质477)的周围时,上述结构的气隙间隔物大致上相同于图55a至图55b所示的气隙间隔物。上述结构的气隙间隔物与图55a至图55b所示的气隙间隔物之间的差异在于,在没有任何如图55a至图55b所示的物理性间隔物围绕隔离介电质的条件下,仅气隙间隔物形成在隔离介电质的周围。

338.图62a至图66b根据本揭示案的一些实施例绘示制造半导体装置400的其中一个阶段的示意图。图62a至图66a绘示沿图37a至图46a的线b4-b4’的截面图。图62b至图66b绘示沿图37a至图46a的线c4-c4’的截面图。半导体装置400在图62a和图62b之前的结构的形成方式大致上相同于半导体装置100在图37a至图39c中方法m的步骤s140至s142的操作方式,因此可参照前述的段落描述而在此不再详述。例如,介电层464和466、金属介层窗465、金属线467、以及牺牲层472的材料和制程大致上相同于图37a至图39c绘示的介电层164和166、金属介层窗165、金属线167、以及牺牲层172的材料和制程,因此可参照前述的段落描述故在此不再详述。

339.请参照图62a至图62b。嵌埋金属介层窗465(见图62a)于介电层464中。形成介电层

466在介电层464和金属介层窗465上。移除金属线467的一部分以形成暴露出下方介电层464的第七开口o7,第七开口o7形成在金属线467所留下的结构之间。换句话说,第七开口o7分隔金属线467所留下的各个结构。毯覆式沉积牺牲层472在介电层466、第七开口o7的侧壁、以及在第七开口o7中的介电层464的顶表面上。在一些实施例中,牺牲层472具有约1nm至约5nm的厚度,例如1、2、3、4或5nm的厚度,但本揭示案不限于此。

340.请参照图63a至图63b。形成隔离介电质477在牺牲层472上以填满超出第七开口o7。在一些实施例中,隔离介电质477的组成包括氧化硅、氮化硅、氮氧化硅、氟掺杂硅酸盐玻璃(fsg)、或低介电常数的介电材料。在一些实施例中,隔离介电质477的形成方式包括hdpcvd,其中使用硅烷(sih4)和氧气当作反应前驱物。在一些其他的实施例中,隔离介电质477的形成方式包括sacvd或harp,其中制程气体可包括四乙氧基硅烷(teos)和臭氧(o3)。在一些实施例中,隔离介电质477的形成方式可包括旋涂式介电质(spin-on-dielectric,sod)制程,例如含氢硅氧烷(hydrogen silsesquioxane,hsq)或甲基硅氧烷(methyl silsesquioxane,msq)。可使用其他制程或其他材料。在一些实施例中,隔离介电质477可为多层结构,例如,热氧化衬垫层和形成在衬垫层上的氮化硅。在此之后,选择性地对隔离介电质477进行热退火制程。在一些实施例中,隔离介电质477的组成材料可不同于牺牲层472。

341.请参照图64a至图64b。执行如cmp的平坦化制程以移除第七开口o7上多余的隔离介电质477和牺牲层472,使得介电层466显露出来。

342.请参照图65a至图66b。执行蚀刻制程以选择性移除牺牲层472的垂直部分,借此形成气隙间隔物475在金属线467和隔离介电质477之间、以及在介电层466和隔离介电质477之间。换句话说,气隙间隔物475分隔金属线467和隔离介电质477。气隙间隔物475具有原本牺牲层472的垂直部分的形状。在一些实施例中,部分的介电层464暴露于气隙间隔物475中。

343.牺牲层472的厚度可在约1nm和约5nm的范围之间。因此,气隙间隔物475的厚度也可在约1nm和约5nm的范围之间,例如约1、2、3、4或5nm。如果牺牲层472的厚度小于1nm,因牺牲层472太窄以至于蚀刻剂难以进入介电层466、金属线467和隔离介电质477之间的空间,进而影响气隙间隔物475的形成。在另一方面,如果牺牲层472的厚度大于5nm,则形成的气隙间隔物475的厚度可能会太宽,以致于后续形成在气隙间隔物475上方的材料可能容易流入气隙间隔物475的底部,进而影响气隙间隔物475的形成。因此,在蚀刻制程过程中,牺牲层472的垂直部分(见图64a至图64b)可能经过蚀刻之后而显露出金属线467和介电层466的垂直侧壁,进而影响气隙间隔物475的形成。

344.在本揭示案中,牺牲层472具有例如大于1的介电常数。在另一方面,气隙间隔物475具有等于1的介电常数且小于牺牲层472的介电常数。因此,半导体装置400的等效介电常数因为气隙间隔物475的形成而降低。如此一来,半导体装置400的整体电容值可降低,进而改善电阻电容延迟(rc delay)亦改善装置表现。

345.在一些实施例中,对牺牲层472的蚀刻制程可包括非等向性蚀刻制程(例如,rie制程或ale制程)。对牺牲层472的蚀刻制程可使用含氧气体、含氟气体(例如,cf4、sf6、ch2f2、chf3、c4f6及/或c4f8)、含氯气体(例如,cl2、chcl3、ccl4及/或bcl3)、含溴气体(例如,hbr及/或chbr3)或含磷气体(例如h3po4)、含碘气体、其他合适的气体或电浆、及/或上述的组合,本

揭示案不限于上述的列举。在一些实施例中,当硅用于牺牲层472之中时,可使用nh4oh来蚀刻牺牲层472的垂直部分(见图64a至图64b),但本揭示案不限于此。进一步详细描述图65a至图66b,蚀刻制程对牺牲层472(见图64a至图64b)的蚀刻速率快于对介电层464及/或金属线467的蚀刻速率。举例来说,牺牲层472比介电层464及/或金属线467的蚀刻选择比可大于约10。当牺牲层472比介电层464及/或金属线467的蚀刻选择比小于约10时,蚀刻制程可能会明显蚀刻介电层464及/或金属线467,从而对半导体装置产生不良影响。在一些实施例中,针对牺牲层472的蚀刻制程可为等向性蚀刻制程。

346.请参照图66a至图66b。形成介电层484在如图65a和图66b所示的结构上。接下来,形成金属介层窗485嵌埋于介电层484中并电性连接金属线467。在一些实施例中,介电层484可包括碳掺杂氧化硅、非晶相氟化碳、聚对二甲苯(perylene)、双苯并环丁烯(bis-benzocyclobutenes,bcb)、聚四氟乙烯(polytetrafluoroethylene,ptfe)(铁氟龙)或碳氧化硅聚合物(sioc)。在一些实施例中,极低介电常数(elk)包括现有介电材料的多孔形式,例如含氢硅氧烷(hsq)、多孔甲基硅氧烷(msq)、多孔聚芳醚(polyarylether,pae)、多孔silk(一种低介电系数材料的产品)或多孔氧化硅。在一些实施例中,介电层484可以包括sicn、sico、sio2、sin、sic、alon、上述的组合、或其他合适的材料。在一些实施例中,介电层484的介电常数小于约2.5。在一些实施例中,介电层484的材料相同于介电层466的材料。在一些实施例中,介电层484的材料不同于介电层466的材料。在一些实施例中,金属介层窗485可包括铜、铂、钌、铝、钽、钨、氮化钽、钛、氮化钛、上述的组合、或其他合适的材料。

347.综合以上,本揭示案的实施例提供益处。然而,应理解的是,本文中未必揭露所有益处,因此其他的实施例可能提供额外的益处,并且全部的实施例不限于特定的益处。在本揭示案中,气隙间隔物是透过移除介于半导体特征(例如,od、金属栅极、源极/漏极接触件、或在多层互连结构中的金属线)和介电间隔物的牺牲层而形成。一个益处在于在半导体装置上形成气隙间隔物可降低ic结构的整体电容值以改善电阻电容延迟(rc delay),进而改善装置表现。再者,因为通过移除半导体特征和介电间隔物之间的牺牲层而形成气隙间隔物,所以能轻易调控气隙间隔物尺寸。除此之外,由于介电材料封住气隙间隔物的上部,因此在后续沉积或蚀刻制程中介电材料可提供气隙间隔物保护。

348.在一些实施例中,一种半导体装置包括基材、半导体鳍部、浅沟槽隔离结构、第一气隙间隔物、以及第一栅极结构。半导体鳍部自基材向上延伸。浅沟槽隔离结构横向地环绕半导体鳍部的下部。第一气隙间隔物介于浅沟槽隔离结构与半导体鳍部之间。第一栅极结构横跨半导体鳍部。在一些实施例中,半导体鳍部的下部暴露在第一气隙间隔物。在一些实施例中,基材暴露在第一气隙间隔物。在一些实施例中,第一栅极结构与第一气隙间隔物重叠。在一些实施例中,半导体装置进一步包括介电结构以密封第一间隔物的顶端。在一些实施例中,介电结构的材料相同于浅沟槽隔离结构的材料。在一些实施例中,半导体装置进一步包括介电间隔物,介于浅沟槽隔离结构和第一气隙间隔物之间。在一些实施例中,介电间隔物的上部的宽度小于介电间隔物的下部的宽度。在一些实施例中,介电间隔物的材料相同于浅沟槽隔离结构的材料。在一些实施例中,半导体装置进一步包括第二栅极结构、源极/漏极结构、介电结构、以及第二气隙间隔物。第二栅极结构横跨半导体鳍部。源极/漏极结构在半导体鳍部上并介于第一栅极结构和第二栅极结构之间。介电结构在源极/漏极结构上。第二气隙间隔物介于第一栅极结构和介电结构之间,亦介于第二栅极结构与介电结

构之间。

349.在一些实施例中,一种半导体装置包括基材、第一和第二半导体鳍部、浅沟槽隔离结构、第一和第二栅极结构、介电结构、以及第一气隙间隔物。第一和第二半导体鳍部自基材向上延伸。浅沟槽隔离结构横向地环绕第一半导体鳍部的下部和第二半导体鳍部的下部。第一栅极结构跨第一半导体鳍部。第二栅极结构横跨第二半导体鳍部。介电结构介于第一栅极结构的长轴端和第二栅极结构的长轴端之间。第一气隙间隔物横向地环绕介电结构。在一些实施例中,浅沟槽隔离结构暴露在第一气隙间隔物。在一些实施例中,半导体装置进一步包括介电密封件以密封第一气隙间隔物的顶端。在一些实施例中,介电密封件的材料相同于介电结构的材料。在一些实施例中,半导体装置进一步包括介电间隔物介于第一气隙间隔物和介电结构之间。在一些实施例中,半导体装置进一步包括第二气隙间隔物,横向地环绕第二半导体鳍部的上部。

350.在一些实施例中,一种制造半导体装置的方法包括:形成金属介层窗在第一介电层中、形成第二介电层在金属介层窗上、形成金属线延伸在第二介电层中并横跨金属介层窗、移除金属线的一部分以形成暴露出第一介电层的沟槽、形成牺牲间隔物作为沟槽的衬垫、形成介电间隔物作为牺牲间隔物的数个侧壁的衬垫、在形成介电间隔物之后移除牺牲间隔物以形成气隙间隔物、以及沉积介电材料在沟槽并密封气隙间隔物。在一些实施例中,形成牺牲间隔物作为沟槽的衬里包括:保形地沉积牺牲层在金属线和第二介电层上、以及移除牺牲层的横向部分并保留牺牲层的纵向部分在沟槽的数个侧壁上。在一些实施例中,制造半导体装置的方法进一步包括在移除牺牲间隔物之后且在沉积介电材料之前,选择性蚀刻介电间隔物以形成锥形顶端在介电间隔物上。在一些实施例中,金属线的长轴端暴露在气隙间隔物。

351.以上概略说明了本揭示案数个实施例的特征,使所属技术领域内具有通常知识者对于本揭示案可更为容易理解。任何所属技术领域内具有通常知识者应了解到本揭示案可轻易作为其他结构或制程的变更或设计基础,以进行相同于本揭示案实施例的目的及/或获得相同的优点。任何所属技术领域内具有通常知识者亦可理解与上述等同的结构并未脱离本揭示案的精神及保护范围内,且可在不脱离本揭示案的精神及范围内,可作更动、替代与修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。