1.本技术涉及一种驱动电路。具体地,本技术涉及根据触发信号输出驱动信号的驱动电路,以及通过从驱动电路输出的驱动信号驱动像素的成像装置。

背景技术:

2.随着成像装置的速度和尺寸的增加,驱动像素区域的驱动电路也需要高驱动能力。因此,已经提出了用于提高驱动电路的驱动能力的技术。例如,已经提出了一种驱动电路,其增加了驱动电路中的晶体管的栅极到源极电压以增加在源极与漏极之间流动的电流,从而提高驱动能力(例如,参见专利文献1)。

3.现有技术文献

4.专利文献

5.专利文献1:日本专利申请公开号2006-279883

技术实现要素:

6.本发明要解决的问题

7.在上述现有技术中,通过增加栅极到源极电压来提高驱动能力。然而,因为驱动电路的输出电压限定在电源电压与接地电位之间,所以需要升压电路来输出高于电源电压的电压,并且需要降压电路来输出低于接地电位的电压。在这种情况下,从升压电路和降压电路提取大量的电力,从电力消耗的角度来看,这可能是个问题。此外,从热设计的角度来看,功耗的增加可能是阻碍驱动电路的高度集成的因素。

8.鉴于这种情况做出本技术,并且其目的是减少驱动电路的功耗。

9.问题的解决方案

10.为了解决上述问题而做出了本技术,并且其第一方面是一种驱动电路,包括:驱动信号输出电路,被配置为根据预定的触发信号输出驱动信号;升压开关,被配置为在上述驱动信号上升时,按照升序依次选择多个电压并且将所选择的电压提供给上述驱动信号输出电路;以及降压开关,被配置为在上述驱动信号下降时,按照降序依次选择多个电压并且将所选择的电压提供给上述驱动信号输出电路。由此,具有使驱动信号的充放电所需的负荷分散的效果。

11.此外,在该第一方面中,还可以包括控制电路,该控制电路被配置为基于上述触发信号,通过在上述升压开关和上述降压开关中生成选择信号来执行控制。根据该结构,起到基于触发信号对升压开关和降压开关的选择进行控制的效果。

12.此外,该第一方面可以适配以使得,在上述驱动信号上升时,上述升压开关选择第一电压直至达到上述第一电压,并且选择高于上述第一电压的第二电压直至达到上述第二电压,以提供给上述驱动信号输出电路,并且在上述驱动信号下降时,上述降压开关选择第三电压直至达到上述第三电压,并且选择低于上述第三电压的第四电压直至达到上述第四电压,以提供给上述驱动信号输出电路。该配置带来用四个振幅电平控制驱动电路的效果。

13.此外,在该第一方面中,可还包括:升压电路,被配置为生成上述第二电压并且将该第二电压提供给上述升压开关;以及降压电路,被配置为生成上述第四电压并且将该第四电压提供给上述降压开关,其中,上述第一电压可以是电源电压,并且上述第三电压可以是接地电位。该配置带来了在利用电源电压预充电或利用接地电位预充电之后通过升压电路或降压电路执行充电和放电的效果。

14.此外,在该第一方面中,还可以包括电容器,该电容器被配置为连接在上述电源电压与上述接地电位之间。该配置带来在驱动电路中提供所需电流的效果。

15.此外,在该第一方面中,还可以包括电压控制偏置电路,该电压控制偏置电路被配置为执行控制以将在晶体管的耐受电压内的电压提供给包括在上述驱动信号输出电路中的晶体管。该配置带来不施加超过晶体管的耐受电压的振幅的效果。

16.此外,在该第一方面中,还可以包括电流控制偏置电路,该电流控制偏置电路被配置为控制流过包括在上述升压开关和上述降压开关中的晶体管的电流。该配置带来控制转换速率的效果。

17.此外,本技术的第二方面是一种成像装置,包括:像素区域,在该像素区域中布置有多个成像元件;以及多个驱动电路,以每个驱动电路与上述多个成像元件对应地包括:驱动信号输出电路,被配置为根据预定的触发信号将驱动信号输出至每个上述成像元件,升压开关,被配置为在上述驱动信号上升时,按照升序依次选择多个电压,以将该电压提供给上述驱动信号输出电路,以及降压开关,被配置为在上述驱动信号下降时,按照降序依次选择多个电压以将该电压提供给上述驱动信号输出电路。该配置带来分散成像装置中的驱动信号的充电和放电所需的负载的效果。

18.此外,在该第二方面中,对于多个驱动电路中的每预定数量的驱动电路,该成像装置还可以包括偏置电路,该偏置电路被配置为将在晶体管的耐受电压内的电压提供给包括在上述驱动信号输出电路中的晶体管,并且控制电流流过包括在上述升压开关和上述降压开关中的晶体管的电流。该配置带来这样的效果:根据驱动电路的布置位置处的电源下降,偏置电压也下降相同的量。

19.此外,在该第二方面中,每个上述偏置电路可以以菊花链形状连接。该构造带来减少布线数量的效果。

附图说明

20.图1是示出根据本技术的实施方式的包括驱动电路的成像装置的配置示例的图。

21.图2是示出根据本技术的实施方式的驱动电路21的块配置示例的图。

22.图3是示出根据本技术的实施方式的驱动电路21的电路配置示例的图。

23.图4是示出根据本技术的实施方式的输入控制电路的电路配置示例的图。

24.图5是示出根据本技术的实施方式的选择信号和驱动信号vsout的时序示例的视图。

25.图6是示出根据本技术的实施方式的转换速率控制的操作示例的视图。

26.图7是示出根据本技术的实施方式的建立时间的比较例的视图。

27.图8是示出根据本技术的实施方式的高频回路的比较例的图。

28.图9是示出根据本技术的实施方式的驱动电路21中的偏置电路167与局部块109之

间的关系的第一示例的图。

29.图10是示出根据本技术的实施方式的驱动电路21中的偏置电路167与局部块109之间的关系的第二示例的图。

30.图11是示出根据本技术的实施方式的驱动电路21中的偏置电路167与局部块109之间的关系的第一示例和第二示例的比较例的图。

31.图12是示出根据本技术的实施方式的驱动电路21的多个偏置电路167的连接示例的图。

具体实施方式

32.在下文中,将描述用于实现本技术的实施方式(在下文中,被称为实施方式)。将按照以下顺序进行描述。

33.1.成像装置和驱动电路

34.2.转换速率控制

35.3.emi

36.4.偏置电路

37.《1.成像装置和驱动电路》

38.[成像装置]

[0039]

图1是示出根据本技术的实施方式的包括驱动电路的成像装置的配置示例的图。该成像装置包括像素区域10和外围电路单元。外围电路单元包括垂直驱动电路20、水平驱动电路30、控制电路40、列信号处理电路50和输出电路60。

[0040]

像素区域10是像素阵列,在该像素阵列中,包括光电转换单元的多个像素11以二维阵列布置。该像素11包括多个像素晶体管和例如用作光电转换单元的光电二极管。这里,多个像素晶体管可包括例如转移晶体管、复位晶体管、选择晶体管和放大晶体管这四种晶体管。

[0041]

垂直驱动电路20用于基于行来驱动像素11。该垂直驱动电路20包括针对每个像素驱动布线的驱动电路21,并且将用于驱动像素11的驱动信号提供给所选择的像素驱动布线。因此,垂直驱动电路20基于行在垂直方向上连续地选择性地扫描像素区域10的单独像素11,并且经由垂直信号线19将基于根据每个像素11的光电转换单元中接收的光的量而生成的信号电荷的像素信号提供给列信号处理电路50。

[0042]

水平驱动电路30基于列来驱动列信号处理电路50。该水平驱动电路30例如由移位寄存器构成。该水平驱动电路30通过依次输出水平扫描脉冲依次地选择每个列信号处理电路50,并且使每个列信号处理电路50经由水平信号线59将像素信号输出至输出电路60。

[0043]

控制电路40控制整个成像装置。该控制电路40接收输入时钟和指示操作模式等的数据,并输出诸如成像装置的内部信息的数据。即,该控制电路40基于垂直同步信号、水平同步信号和主时钟生成用作垂直驱动电路20、列信号处理电路50、水平驱动电路30等的操作的基准的时钟信号或控制信号。然后,这些信号输入到垂直驱动电路20、列信号处理电路50、水平驱动电路30等。

[0044]

列信号处理电路50例如针对每列的像素11进行布置,并且针对每个像素列对从一行的像素11输出的信号执行诸如噪声去除的信号处理。即,该列信号处理电路50执行信号

处理,诸如用于去除像素11特有的固定模式噪声的相关双采样(cds)、信号放大以及模数(ad)转换。在列信号处理电路50的输出级中,水平选择开关(未示出)与水平信号线59连接。

[0045]

输出电路60对通过水平信号线59从每个列信号处理电路50依次提供的信号执行信号处理,并且输出该信号。此时,该输出电路60缓冲来自列信号处理电路50的信号。此外,该输出电路60可以对来自列信号处理电路50的信号执行黑电平调整、列变化校正、各种类型的数字信号处理等。

[0046]

[驱动电路]

[0047]

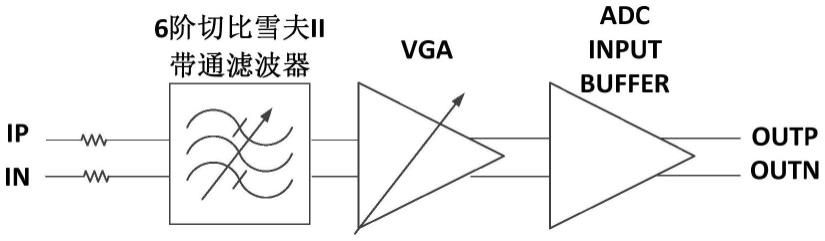

图2是示出根据本技术的实施方式的驱动电路21的块配置示例的图。

[0048]

驱动电路21包括驱动信号输出电路190、a开关110、b开关120、c开关130、d开关140、升压电路210、降压电路310和电容器420。

[0049]

此外,该驱动电路21包括焊盘911、912、921和922。在焊盘911与912之间连接电源910。电源电压vddh被提供给焊盘911,并且接地电位vssh被提供给焊盘912。升压电路210的输出电压vpi被提供给焊盘921。此外,降压电路310的输出电压vrl被提供给焊盘922。这里,升压电路210的输出电压vpi是高于电源电压vddh的电压。此外,降压电路310的输出电压vrl是低于接地电位vssh的电压。

[0050]

驱动信号输出电路190是被配置为根据触发信号trg输出驱动信号vsout的电路。驱动信号vsout被分配给对应行的各个像素。这里,统一示出了线的总布线电阻510和总寄生电容520。

[0051]

a开关110是选择是否将电源电压vddh提供给驱动信号输出电路190的开关。b开关120是选择是否将升压电路210的输出电压vpi提供给驱动信号输出电路190的开关。在驱动信号vsout上升时,a开关110和b开关120中的任一个独占地将电压提供给驱动信号输出电路190。结果,选择电源电压vddh直到达到该电源电压vddh为止,并且之后选择电压vpi直到达到该电压vpi为止,以将该电源vddh电压和电压vpi提供给驱动信号输出电路190。即,a开关110和b开关120按照升序依次选择多个电压,并将所选择的电压提供给驱动信号输出电路190。注意,a开关110和b开关120是权利要求中描述的升压开关的示例。

[0052]

c开关130是选择是否将接地电位vssh提供给驱动信号输出电路190的开关。d开关140是选择是否将降压电路310的输出电压vrl提供给驱动信号输出电路190的开关。在驱动信号vsout下降时,c开关130和d开关140中的任一个独占地将电压提供给驱动信号输出电路190。结果,选择接地电位vssh直至达到该接地电位vssh,并且此之后选择电压vrl直至达到该电压vrl,并且将该接地电位vssh和电压vrl提供给驱动信号输出电路190。即,c开关130和d开关140按照降序依次选择多个电压,并且将所选择的电压提供给驱动信号输出电路190。注意,c开关130和d开关140是权利要求中所述的降压开关的示例。

[0053]

升压电路210用于生成输出电压vpi并且将电压vpi提供给b开关120。如上所述,该升压电路210的输出电压vpi是高于电源电压vddh的电压。

[0054]

降压电路310用于生成输出电压vrl并且将电压vrl提供给d开关140。如上所述,该降压电路310的输出电压vrl是低于电源电压vssh的电压。

[0055]

电容器420是被配置为在电源电压vddh与接地电位vssh之间连接的电容元件。如稍后将描述的,当触发信号trg改变时,陡电流可以流动。在这种情况下,该电容器420被提供电流。

[0056]

[功耗]

[0057]

这里,将描述驱动电路21的功耗。在驱动电路21中,当施加触发信号trg时,a开关110、b开关120、c开关130以及d开关140依次接通。

[0058]

首先,在驱动信号vsout上升时,a开关110接通,并且执行从初始状态下的电压vrl到电源电压vddh的充电。此后,当达到电源电压vddh时,b开关120接通,并执行从电源电压vddh到电压vpi的充电。也就是说,代替从电压vrl一次全部充电到电压vpi,从电源电压vddh执行充电直到达到电源电压vddh,以及通过使用升压电路210执行充电直到剩下的电压vpi。结果,可以减小从升压电路210提供的电流。

[0059]

在下文中,作为示例,假设电源电压vddh是2.8v,接地电位vssh是0v,电压vpi是3.0v,并且电压vrl是-1.2v。因为负载电流与振幅比成比例,所以升压电路210所需的电流与总电流的比率如下。

[0060]

(vpi-vddh)/(vpi-vrl)=0.2/4.2

[0061]

=4.8%

[0062]

即,假设驱动电路21的负载电流是10ma,升压电路210所需的电流大约为0.5ma。

[0063]

此外,当假设相对于负载电流iload的损耗α%时,上升时的功耗由以下公式表示。

[0064]

vddh

×

iload(1 α)

ꢀꢀꢀꢀꢀꢀꢀꢀ

公式(1)

[0065]

在以上公式中,假设电源电压vddh是2.8v并且损耗α=50%,在从升压电路210供应全部电流的情况下在上升时的功耗如下。

[0066]

2.8v

×

10ma(1 0.5)=42.0mw

[0067]

然而,在从升压电路210仅提供电源电压vddh和电压vpi之间的电流的情况下,上升时的功耗如下。

[0068]

2.8v

×

0.5ma(1 0.5)=2.1mw

[0069]

接下来,在驱动信号vsout下降时,c开关130接通,并且执行从电压vpi到接地电位vssh的放电。此后,当达到接地电位vssh时,则d开关140接通,并且执行从接地电位vssh到电压vrl的放电。即,代替从电压vpi一次全部放电到电压vrl,执行放电到接地电位vssh直到达到接地电位vssh,并且通过使用降压电路310执行放电直到剩下的电压vrl。结果,可以减小从降压电路310供给的电流。

[0070]

如上所述,由于负载电流与振幅比成比例,所以降压电路310所需的电流与总电流的比率如下。

[0071]

(vssh-vrl)/(vpi-vrl)=1.2/4.2

[0072]

=29%

[0073]

即,假设驱动电路21的负载电流如上所述为10ma,则降压电路310所需的电流为约2.9ma。

[0074]

此外,下降时的功耗也由公式(1)表示,并且在从降压电路310供应全部电流的情况下在下降时的功耗如下。

[0075]

2.8v

×

10ma(1 0.5)=42.0mw

[0076]

然而,在从降压电路310仅提供电源电压vddh和电压vrl之间的电流的情况下,上升时的功耗如下。

[0077]

2.8v

×

2.9ma(1 0.5)=12.2mw

[0078]

此外,作为这种功耗改善的次要效果,开关电容器电容(cfly)也可以减小至相同程度,这也可以有助于减小面积。

[0079]

如上所述,在本技术的实施方式中,通过切换一次至电源电压vddh或接地电位vssh并且在消耗最多电力的上升或下降转变时从电源电压vddh或接地电位vssh提取大部分电力,从升压电路210和降压电路310提取的电力减小,并且能够减小升压电路210和降压电路310的电力和面积。

[0080]

注意,在上述示例中,假定通过四个开关选择四种电压类型,并将其提供给驱动信号输出电路190。然而,不限于此,可以根据需要改变电压的类型和开关的数量。

[0081]

[电路配置]

[0082]

图3是示出根据本技术的实施方式的驱动电路21的电路配置示例的图。

[0083]

该驱动电路21使用触发信号trg作为输入信号。该图示出从触发信号trg生成的选择信号xa、xb、c、xc、d和xd。稍后将描述这些选择信号和触发信号trg之间的关系。

[0084]

a开关110包括pmos晶体管111和112。pmos晶体管111根据选择信号xa来操作。pmos晶体管112是用于转换速率控制的晶体管,并且根据来自稍后描述的转换速率控制偏置电路170的控制信号vbp来操作。

[0085]

b开关120包括pmos晶体管121。pmos晶体管121根据选择信号xb来操作。

[0086]

c开关130包括nmos晶体管131和132。nmos晶体管131根据来自pmos晶体管186的信号来操作,pmos晶体管186根据选择信号xc来操作。nmos晶体管132是用于转换速率控制的晶体管,并且根据来自稍后描述的转换速率控制偏置电路170的控制信号vbn来操作。

[0087]

d开关140包括nmos晶体管141。nmos晶体管141根据来自pmos晶体管187的信号来操作,pmos晶体管187根据选择信号xd来操作。

[0088]

pmos晶体管191和nmos晶体管192输出驱动信号vsout作为驱动信号输出电路190。该驱动信号vsout的振幅在上述示例中为4.2v(=vpi-vrl)。然而,由于pmos晶体管191和nmos晶体管192的耐压被假定为3v,所以pmos晶体管151至154和nmos晶体管155至158被设置为用于这些晶体管的耐压保护的耐压保护电路150。pmos晶体管191和151至154的栅极电压被固定到接地电位vssh,并且nmos晶体管192和155至158的栅极电压根据来自稍后描述的耐压保护偏置电路160的控制信号vbm来操作。

[0089]

nmos晶体管181和182以及nmos晶体管183和184分别是负电平移位器。因为c开关130和d开关140由低于接地电位vssh的负电压vrl控制,所以经由这些负电平移位器控制c开关130和d开关140的信号生成。

[0090]

pmos晶体管185和186是控制nmos晶体管131的振幅的电平移位器。pmos晶体管187和188是控制nmos晶体管141的振幅的电平移位器。

[0091]

耐压保护偏置电路160是用于生成耐压保护电路150的nmos晶体管155至158和192的栅极偏置信号vbm的电路。耐压保护偏置电路160包括nmos晶体管161和可变电阻器162。注意,耐压保护偏置电路160是权利要求中描述的电压控制偏置电路的示例。

[0092]

nmos晶体管161是nmos晶体管192和155至158的电流镜电路的副本。该配置使得可以消除工艺-电压-温度(pvt)变化。

[0093]

可变电阻器162是微调电阻器,其两端的电压dv由电阻值r1和电流iref1的乘积确定。因此,当nmos晶体管161的栅极到源极电压为vgsn时,耐压保护偏置电路160的输出信号

vbm为dv vgsn。当要经受耐压保护的晶体管的耐受电压是3.0v时,可以通过调整可变电阻器162来实现与晶体管的耐压匹配的设计,从而获得以下。

[0094]

dv vgsn-vgsn-vrl=dv-vrl《3.0v

[0095]

转换速率控制偏置电路170是在a开关110被接通的时间段期间限制电流并控制转换速率的偏置电路。该转换速率控制偏置电路170包括被配置为生成pmos晶体管112的控制信号vbp的pmos晶体管171、以及被配置为生成nmos晶体管132的控制信号vbn的nmos晶体管172和173。稍后将描述该转换速率控制偏置电路170的细节。

[0096]

图4是示出根据本技术的实施方式的输入控制电路的电路配置示例的图。

[0097]

驱动电路21使用触发信号trg作为输入信号,以基于该触发信号trg生成内部信号。即,驱动电路21将触发信号trg反相以生成反相触发信号xtrg。此外,驱动电路21使触发信号trg移位以生成移位触发信号trg_sft。此外,驱动电路21将移位触发信号trg_sft反相以生成反相移位触发信号xtrg_sft。

[0098]

然后,通过组合这些信号,驱动电路21生成控制a开关110、b开关120、c开关130和d开关140所需的选择信号。与(and)电路101生成触发信号trg和反相移位触发信号xtrg_sft的逻辑积并且输出信号a。与电路102生成触发信号trg和移位触发信号trg_sft的逻辑积并且输出信号b。与电路103生成反相触发信号xtrg与移位触发信号trg_sft的逻辑积并且输出信号c。与电路104生成反相触发信号xtrg与反相移位触发信号xtrg_sft的逻辑积,并输出信号d。此外,反相器105至108分别反相与电路101至104的输出a至d,并且输出信号xa至xd。注意,与电路101至104和反相器105至108是权利要求中描述的控制电路的示例。

[0099]

[操作时序]

[0100]

图5是示出根据本技术的实施方式的选择信号和驱动信号vsout的时序示例的视图。

[0101]

在信号a激活的周期期间,a开关110接通,并且将驱动信号vsout从电压vrl充电至电源电压vddh。该期间是预充电期间。在信号b被激活的期间,b开关120接通,驱动信号vsout从电源电压vddh被充电到电压vpi。

[0102]

在信号c激活的时段期间,c开关130接通,并且驱动信号vsout从电压vpi放电到接地电位vssh。该时间段是预充电时间段。在信号d激活的周期期间,d开关140接通,并且驱动信号vsout从接地电位vssh放电至电压vrl。

[0103]

《2.转换速率控制》

[0104]

在成像装置中,因为驱动电路21设置用于每个控制信号和用于每个线路,所以成千上万的部件根据实现方式作为整体同时移动。在它们同时操作的情况下,生成大的峰值电流,并且由于具有电源寄生电阻的ir下降,电源电压降低,这可引起故障。为了防止这一点,在本实施方式中,转换速率控制偏置电路170被设置为控制流过a开关110和c开关130的电流的恒定电流偏置电路。因此,执行经由a开关110和c开关130的操作时的转换速率控制。转换速率是输出信号的变化率。当转换速率慢时,其作为输出波形的斜率变得明显。因此,通过控制该转换速率可适当地确保输出波形。注意,转换速率控制偏置电路170是权利要求中所述的电流控制偏置电路的示例。

[0105]

[峰值电流抑制]

[0106]

图6是示出根据本技术的实施方式的转换速率控制的操作示例的视图。

[0107]

在该图中,a是在没有执行转换速率控制的情况下作为电压驱动器操作的情况下的图像示例。在电压驱动器中,电流由晶体管的大小和vgs确定。在这种情况下,在触发信号trg升高时,在电源电流和电源电压中出现大峰值,并且在输出的驱动信号vsout中出现舍入(rounding)。

[0108]

然而,该图中的b示出通过提供转换速率控制偏置电路170而作为恒定电流驱动器操作的情况的示例。在电流驱动器中,流过的电流由恒定电流源限制。在这种情况下,由于iref1是恒定的,所以斜率由iref1/c确定,并且不出现大峰值。此外,通过改变pmos晶体管171和nmos晶体管173的尺寸比或iref2,能够控制到任何转换速率。

[0109]

[设置时间的改善]

[0110]

根据本实施方式的驱动电路21在a开关110或c开关130接通时用作电流驱动器,并且此后,在b开关120或d开关140接通时用作使用升压电路210或降压电路310的电压驱动器。

[0111]

电压驱动器的时间常数tau如下。

[0112]

tau=(z r)

×c[0113]

在此,z表示驱动器的输出阻抗,r表示布线寄生电阻。该电压驱动器具有以下两个问题。首先,z需要充分小于r以便增加速度,但是驾驶员面积增加。其次,大的驱动器尺寸导致瞬时生成大的峰值电流并且电源电压下降,使得在转变时驱动器输出阻抗z增加,并且稳定进一步减慢。因此,电压驱动器的配置实质上不能驱动大容量的负载,并且操作速度受到限制。

[0114]

然而,在本实施方式中,由于电容器最初通过电流驱动器用恒定电流控制进行充电,因此没有z的影响。通过在某个固定部分以恒定电流驱动之后切换到电压驱动器,由于电压驱动器要供应的电荷量本身已经减少,所以电源电压下降较小。结果,可以比全部由电压驱动器驱动的情况更快地执行安定,这有助于加速。

[0115]

图7是示出根据本技术的实施方式的建立时间的比较例的视图。

[0116]

在该图中,链线(chain line)表示在从开始使用升压电路210或降压电路310作为电压驱动器操作的情况下的波形。在这种情况下,从开始起,电压曲线地增加时间常数tau(0.63倍)。

[0117]

然而,例如,实线表示在本实施方式的驱动电路21中在由电流驱动器控制电流源高达目标电压v的0.63倍并且此后切换至电压驱动器的情况下的波形。在这种情况下,电压首先通过电流驱动器线性增加,并且然后曲线地增加上述时间常数tau。因为作为电流驱动器提供0.63的必要电荷量,所以将由作为电压驱动器的升压电路210和降压电路310提供的电荷量仅需要是0.63。

[0118]

《3.emi》

[0119]

图8是示出根据本技术的实施方式的高频回路的比较例的图。

[0120]

如上所述,在本实施方式中,电容器420用于在触发信号trg改变时提供电流。由于外部电容器不执行高频响应,因此期望以这种方式结合电容器420。另一方面,如该图的a所示,在始终向驱动信号输出电路供给电压vpi和电压vrl的配置中,存在振幅宽度变大、电压超过电容元件的耐受电压的可能性,因此难以配置电容器。因此,由于在转变时执行操作以从外部汲取电流,所以出现意外的大电流回路,这导致电磁干扰(emi)的劣化。

[0121]

在这方面,在本实施方式中,由于在电源电压vddh与接地电位vssh之间交换大部分电流,所以可布置片上电容器420。结果,如该图的b中所示,可以使电流回路变小,并且可以抑制emi。此外,由于采用恒流驱动器,大部分频率分量成为直流分量,因此谐波分量比电压驱动器的谐波分量小,因此可以使电容器420的尺寸小。

[0122]

《4.偏置电路》

[0123]

本实施方式中的驱动电路21包括如上所述的耐压保护偏置电路160和转换速率控制偏置电路170。在下文中,这些被缩写为偏置电路167。在驱动电路21中,可以与其他电路(局部块109)独立地提供的偏置电路167(全局块),并且可以针对多个局部块109布置一个偏置电路167。

[0124]

图9是示出根据本技术的实施方式的驱动电路21中的偏置电路167与局部块109之间的关系的第一示例的图。

[0125]

在该第一示例中,偏置信号经由长布线被分配到用于一个偏置电路167的多个局部块109。如上所述,在成像装置中,由于根据芯片中的实现方式可以同时使用几千个驱动电路21,所以生成非常大的峰值电流。在不能充分地布置电源焊盘的情况下,电源ir下降在焊盘的近端和远端处是不同的。然而,由于偏置信号组不允许电流流动,所以近端和远端之间没有太大差异。因此,虽然vgs没有差异,因此在近端建立较快,但是存在vgs小并且在远端建立较慢的问题。

[0126]

图10是示出根据本技术的实施方式的驱动电路21中的偏置电路167与局部块109之间的关系的第二示例的图。

[0127]

在该第二示例中,偏置电路167针对若干局部块109中的每个以分布式方式布置。结果,根据局部块109的布置位置处的电源下降,可以降低相同量的偏置电压,可以使vgs恒定,并且可以消除稳定差。

[0128]

图11是示出根据本技术的实施方式的驱动电路21中的偏置电路167与局部块109之间的关系的第一示例和第二示例的比较例的图。

[0129]

这里,作为示例,关注a开关110的pmos晶体管111和112的部分。在该图中的a中,如在第一示例中,随着触发信号trg的变化,ir下降发生在焊盘远端的电源电压vddh中,但是偏置信号vbp不波动,并且因此,pmos晶体管111的vgs减小,并且安定延迟。

[0130]

另一方面,在该图的b中,通过如在第二示例中那样分配偏置电路167,偏置信号vbp也根据该位置处的电源电压vddh的ir下降而下降。结果,vgs保持恒定,并且可以消除稳定中的差异。

[0131]

图12是示出根据本技术的实施方式的驱动电路21的多个偏置电路167的连接示例的图。

[0132]

在如上所述的第二示例中分散地布置多个偏置电路167的情况下,期望以菊花链顺序连接。因此,可以减少布线的数目。

[0133]

应注意,上述实施方式是用于体现本技术的示例,并且实施方式中的事项和权利要求中用于指定本发明的事项具有对应关系。类似地,权利要求中用于指定本发明的事项与本技术的实施方式中分配有相同名称的事项具有对应关系。然而,本技术不限于实施方式,并且在不背离其主旨的情况下,可以通过对实施方式应用各种修改来体现。

[0134]

应注意,在本说明书中描述的效果仅是示例并且不受限制,并且可以存在另外的

效果。

[0135]

应注意,本技术还可具有以下配置。

[0136]

(1)一种驱动电路,包括:

[0137]

驱动信号输出电路,被配置为根据预定的触发信号输出驱动信号;

[0138]

升压开关,被配置为在所述驱动信号上升时,按照升序依次选择多个电压并且将所选择的电压提供给所述驱动信号输出电路;以及

[0139]

降压开关,被配置为在所述驱动信号下降时,按照降序依次选择多个电压并且将所选择的电压提供给所述驱动信号输出电路。

[0140]

(2)根据(1)所述的驱动电路,还包括:

[0141]

控制电路,被配置为基于所述触发信号,通过在所述升压开关和所述降压开关中生成选择信号来执行控制。

[0142]

(3)根据(1)或(2)所述的驱动电路,其中,

[0143]

在所述驱动信号上升时,所述升压开关选择第一电压直至达到所述第一电压以将所述第一电压提供给所述驱动信号输出电路,并且选择高于所述第一电压的第二电压直至达到所述第二电压以将所述第二电压提供给所述驱动信号输出电路;并且

[0144]

在所述驱动信号下降时,所述降压开关选择第三电压直至达到所述第三电压以将所述第三电压提供给所述驱动信号输出电路,并且选择低于所述第三电压的第四电压直至达到所述第四电压以将所述第四电压提供给所述驱动信号输出电路。

[0145]

(4)根据(3)所述的驱动电路,还包括:

[0146]

升压电路,升压电路,被配置为生成所述第二电压并且将所述第二电压提供给所述升压开关;以及

[0147]

降压电路,被配置为生成所述第四电压并且将所述第四电压提供给所述降压开关;其中,

[0148]

所述第一电压是电源电压;并且

[0149]

所述第三电压是接地电位。

[0150]

(5)根据(4)所述的驱动电路,还包括:

[0151]

电容器,被配置为连接在所述电源电压与所述接地电位之间。

[0152]

(6)根据(1)至(5)中任一项所述的驱动电路,还包括:

[0153]

电压控制偏置电路,被配置为控制以将在晶体管的耐受电压内的电压提供给包括在所述驱动信号输出电路中的所述晶体管。

[0154]

(7)根据(1)至(6)中任一项所述的驱动电路,还包括:

[0155]

电流控制偏置电路,被配置为控制流过包括在所述升压开关和所述降压开关中的晶体管的电流。

[0156]

(8)一种成像装置,包括:

[0157]

像素区域,在所述像素区域中布置有多个成像元件;以及

[0158]

多个驱动器电路,以每个所述驱动电路与多个所述成像元件相对应的方式包括:驱动信号输出电路,所述驱动信号输出电路被配置为根据预定的触发信号将驱动信号输出至每个所述成像元件;升压开关,被配置为在所述驱动信号上升时,按照升序依次选择多个电压以将多个所述电压提供给所述驱动信号输出电路;以及降压开关,被配置为在所述驱

动信号下降时,按照降序依次选择多个电压以将多个所述电压提供给所述驱动信号输出电路。

[0159]

(9)根据(8)所述的成像装置,针对多个所述驱动电路中的每预定数量的驱动电路,该成像装置还包括偏置电路,该偏置电路被配置为将在晶体管的耐受电压内的电压提供给包括在所述驱动信号输出电路中的所述晶体管,并且控制流过包括在所述升压开关和所述降压开关中的所述晶体管的电流。

[0160]

(10)根据(9)所述的成像装置,其中,每个所述偏置电路以菊花链连接。

[0161]

附图标记列表

[0162]

10 像素区域

[0163]

11 像素

[0164]

20 垂直驱动电路

[0165]

21 驱动电路

[0166]

30 水平驱动电路

[0167]

40 控制电路

[0168]

50 列信号处理电路

[0169]

60 输出电路

[0170]

101至104 与电路

[0171]

105至108 反相器

[0172]

110 a开关

[0173]

120 b开关

[0174]

130 c开关

[0175]

140 d开关

[0176]

150 耐压保护电路

[0177]

160 耐压保护偏置电路

[0178]

162 可变电阻器

[0179]

167 偏置电路

[0180]

170 转换速率控制偏置电路

[0181]

190 驱动信号输出电路

[0182]

210 升压电路

[0183]

310 步降电路

[0184]

420 电容器

[0185]

510 布线电阻

[0186]

520 寄生电容

[0187]

910 电源

[0188]

911、912、921、922 焊盘。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。