技术特征:

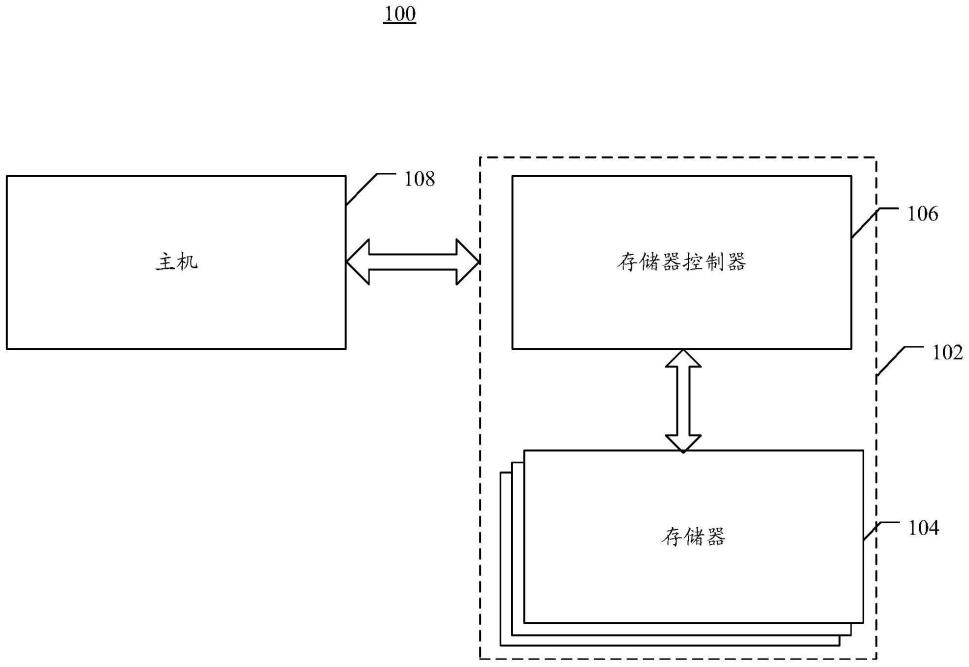

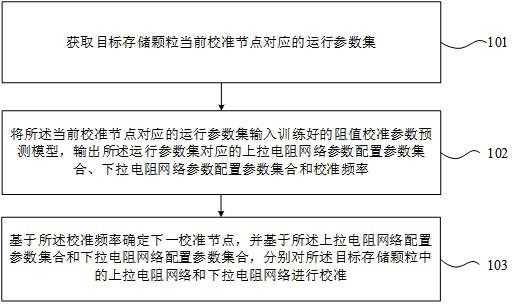

1.一种存储器的控制逻辑电路,其特征在于,包括:微处理器和控制总线cbus,所述微处理器通过所述cbus与所述存储器的外围电路中的设定电路连接;所述设定电路包含寄存器;其中;所述cbus包括用于传输所述微处理器发出的掩码控制信号的掩码控制线和用于传输数据的一组数据传输线;其中,在所述掩码控制线传输的掩码控制信号有效的情况下,所述数据传输线,用于传输掩码数据;所述掩码数据与所述控制数据共用作用以改变所述寄存器存储的原始数据中需要改变的数据位。2.根据权利要求1所述的控制逻辑电路,其特征在于,所述cbus还包括:时钟控制线,其中;所述时钟控制线,用于传输时钟信号;所述数据传输线,用于在所述掩码控制信号有效的情况下,基于所述时钟信号传输所述掩码数据。3.根据权利要求2所述的控制逻辑电路,其特征在于,所述数据传输线,还用于在所述掩码数据传输之前或之后,基于所述时钟信号的传输所述控制数据。4.根据权利要求1所述的控制逻辑电路,其特征在于,所述cbus还包括:一组地址传输线,其中;所述一组地址传输线,用于传输所述寄存器的地址信号;所述地址信号用于使所述掩码数据和所述控制数据被传输到所述寄存器。5.根据权利要求1所述的控制逻辑电路,其特征在于,所述掩码数据、所述控制数据、所述原始数据包含相同的比特位。6.根据权利要求1所述的控制逻辑电路,其特征在于,所述cbus为仅用于向所述寄存器写入数据的单向总线。7.根据权利要求1所述的控制逻辑电路,其特征在于,所述微处理器包括至少一个。8.一种存储器,其特征在于,包括:存储阵列和与所述存储阵列耦接且用于控制所述存储阵列的外围电路,其中;所述外围电路包括权利要求1至7所述的控制逻辑电路。9.一种存储系统,其特征在于,包括:一个或多个权利要求8所述的存储器和与所述存储器耦接的存储器控制器;所述存储器控制器,用于向所述存储器发送各种操作命令。10.根据权利要求9所述的存储系统,所述存储系统是固态硬盘ssd或存储卡。11.一种存储器的操作方法,其特征在于,应用于所述存储器包含控制逻辑电路;所述控制逻辑电路包括微处理器和控制总线cbus;所述微处理器通过所述cbus与所述存储器的外围电路中的设定电路连接;所述设定电路包含寄存器;所述操作方法包括:所述微处理器通过所述cbus的掩码控制线传输掩码控制信号;在所述掩码控制信号有效的情况下,所述微处理器控制所述cbus的数据传输线传输掩码数据;所述掩码数据与所述控制数据共用作用以改变所述寄存器存储的原始数据中需要改变的数据位。12.根据权利要求11所述的操作方法,其特征在于,所述操作方法还包括:将所述掩码数据与所述原始数据进行第一次逻辑运算,获得中间运算结果;将所述中间运算结果与所述控制数据进行第二次逻辑运算,获得目标运算结果;将所述目标运算结果按照原先的顺序存储于所述寄存器,以改变所述寄存器存储的原

始数据中需要改变的数据位。

技术总结

本发明实施例提供一种控制逻辑电路、存储器、存储系统及操作方法。其中,所述控制逻辑电路包括:微处理器和控制总线CBUS,所述微处理器通过所述CBUS与所述存储器的外围电路中的设定电路连接;所述设定电路包含寄存器;其中;所述CBUS包括用于传输所述微处理器发出的掩码控制信号的掩码控制线和用于传输数据的一组数据传输线;其中,在所述掩码控制线传输的掩码控制信号有效的情况下,所述数据传输线,用于传输掩码数据;所述掩码数据与所述控制数据共用作用以改变所述寄存器存储的原始数据中需要改变的数据位。中需要改变的数据位。中需要改变的数据位。

技术研发人员:石蕾 段竺琴 刘艳兰

受保护的技术使用者:长江存储科技有限责任公司

技术研发日:2022.07.20

技术公布日:2022/10/11

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。