集成结势垒肖特基二极管的平面型功率mosfet器件

技术领域

1.本技术涉及半导体制造技术领域,尤其涉及集成结势垒肖特基二极管的平面型功率mosfet器件。

背景技术:

2.碳化硅晶体中存在基晶面位错(bpd),在一定条件下,基晶面位错(bpd)可以转化为堆垛层错(sf)。当碳化硅功率mosfet器件中的体二极管导通时,在双极型运行下,电子-空穴的复合会使堆垛层错(sf)继续扩展,发生双极性退化。这一现象使得碳化硅功率mosfet的导通压电阻增大,阻断模式下的漏电流增大,体二极管的导通压降增大,从而降低器件的可靠性。

3.在实际的电路应用中,为了避免双极性退化,设计者一般使用外部反向并联肖特基二极管来抑制功率mosfet器件中的体二极管。然而,出于成本的考虑,我们可以将结势垒肖特基二极管嵌入到功率mosfet器件中的每个元胞单元,同时整个器件共用同一个的终端结构,这样一来,可以减小总芯片尺寸。

4.但是对于元胞内部集成结势垒肖特基二极管的碳化硅平面功率mosfet器件,结势垒肖特基元胞和mosfet元胞共同占用器件的有源区部分会存在冲突关系。因此,如何解决现有的结势垒肖特基元胞和mosfet元胞,在共同占用器件的有源区部分时存在冲突的问题亟待解决。

技术实现要素:

5.本技术实施例提供了集成结势垒肖特基二极管的平面型功率mosfet器件,用以解决现有的结势垒肖特基元胞和mosfet元胞,在共同占用器件的有源区部分时存在冲突的技术问题。

6.本技术实施例提供了集成结势垒肖特基二极管的平面型功率mosfet器件,其特征在于,器件包括:外延层,以及在外延层的第一侧表面分布的复合元胞;其中,外延层为n型区域;复合元胞包括:阱区、源极区域、第一高掺杂p型区域及结势垒肖特基区域;其中:阱区为p型区域,源极区域与肖特基区域为n型区域;第一高掺杂p型区域环绕结势垒肖特基区域;第一高掺杂p型区域与结势垒肖特基区域为同心正多边形或同心圆环结构;结势垒肖特基区域包含预设数量个第二高掺杂p型区域,以及在高掺杂p型区域之间形成的肖特基区域;在阱区环绕的区域形成结型场效应管jfet区域;阱区与外延层间形成第一pn结,阱区与源极区域间形成第二pn结,预设数量个第二高掺杂p型区域与外延层间形成第三pn结;jfet区域的宽度的取值范围与肖特基区域的宽度的取值范围均在相同的预设区间。

7.本技术实施例提供的集成结势垒肖特基二极管的平面型功率mosfet器件,通过对结势垒肖特基元胞和mosfet元胞融合的特殊设计,不仅解决了现有的结势垒肖特基元胞和mosfet元胞,在共同占用器件的有源区部分时存在冲突的问题,还保证了在较小的mosfet器件导通损耗的前提下,使得结势垒肖特基二极管具有较高的电流导通能力。

8.在本技术的一种实现方式中,阱区与第二高掺杂p型区域接触;阱区与其环绕的结型场效应管jfet区域为同心圆环结构或同心正多边形结构。

9.在本技术的一种实现方式中,器件还包括:欧姆接触金属;欧姆接触金属覆盖于第一高掺杂p型区域及部分源极区域表面;欧姆接触金属与第一高掺杂p型区域间形成第一欧姆接触;欧姆接触金属与源极区域间形成第二欧姆接触;第一欧姆接触与第二欧姆接触相互连接,以抑制mosfet器件内部的寄生双极晶体管效应。

10.在本技术的一种实现方式中,器件还包括:肖特基接触金属;肖特基接触金属覆盖于结势垒肖特基区域的表面;肖特基接触金属与肖特基区域间形成肖特基接触。

11.在本技术的一种实现方式中,器件还包括:绝缘栅极氧化层与栅极导电多晶硅;绝缘栅极氧化层覆盖于jfet区域与阱区上,绝缘栅极氧化层的边界位于源极区域上;栅极导电多晶硅覆盖于绝缘栅极氧化层上,栅极导电多晶硅的宽度小于或等于绝缘栅极氧化层的宽度。

12.在本技术的一种实现方式中,器件还包括:绝缘介质层;绝缘介质层覆盖于绝缘栅极氧化层与栅极导电多晶硅上。

13.在本技术的一种实现方式中,器件还包括:源极电极;源极电极与欧姆接触金属及肖特基接触金属接触;绝缘介质层将栅极导电多晶硅与源极金属分隔开。

14.在本技术的一种实现方式中,器件还包括:碳化硅衬底、漏极电极;碳化硅衬底的第一侧表面与外延层的第二侧表面接触;其中,碳化硅衬底为n型区域;漏极电极覆盖于碳化硅衬底的第二侧表面。

15.在本技术的一种实现方式中,碳化硅衬底的离子掺杂浓度大于外延层的离子掺杂浓度;jfet区域与肖特基区域的离子掺杂浓度均大于或等于外延层的离子掺杂浓度。

16.在本技术的一种实现方式中,预设区间为0.8um~5um,预设数量的范围为1~10个。

附图说明

17.此处所说明的附图用来提供对本技术的进一步理解,构成本技术的一部分,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

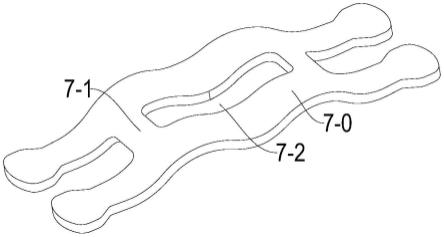

18.图1为本技术实施例提供的一种正八边形和正八边形复合元胞结构示意图;

19.图2为本技术实施例提供的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区截面图;

20.图3为本技术实施例提供的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区另一方向截面图;

21.图4为本技术实施例提供的一种圆形和正四边形复合元胞结构示意图。

22.附图标记说明:

23.碳化硅衬底101;外延层102;阱区103;源极区域104;第一高掺杂p型区域105;绝缘栅极氧化层106;栅极导电多晶硅107;绝缘介质层108;欧姆接触金属109;肖特基接触金属110;源极电极111;漏极电极112;jfet区域113;结势垒肖特基区域114;第一pn结115;第二pn结116;第二高掺杂p型区域117;第三pn结118。

具体实施方式

24.为使本技术的目的、技术方案和优点更加清楚,下面将结合本技术具体实施例及相应的附图对本技术技术方案进行清楚、完整地描述。显然,所描述的实施例仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

25.本技术实施例提供了集成结势垒肖特基二极管的平面型功率mosfet器件,用以解决现有的结势垒肖特基元胞和mosfet元胞,在共同占用器件的有源区部分时存在冲突的技术问题。

26.下面通过附图对本技术实施例提出的技术方案进行详细的说明。

27.图1为本技术实施例提供的一种正八边形元胞结构示意图。如图1所示,复合元胞包括:阱区103、源极区域104、第一高掺杂p型区域105及结势垒肖特基区域114。第一高掺杂p型区域105与结势垒肖特基区域114为同心正四边形结构;在阱区103环绕的区域形成结型场效应管jfet区域113,阱区103与其环绕的结型场效应管jfet区域113为同心正八边形结构。

28.可以理解的是,图1中提供的仅为众多示例中的一种复合元胞;第一高掺杂p型区域与结势垒肖特基区域也可以为同心圆环结构或其他同心正多边形结构,阱区与其环绕的结型场效应管jfet区域也可以为同心圆环结构或其他同心正多边形结构。

29.需要说明的是,平面型功率mosfet器件的电阻由以下几个部分构成:源极电阻、沟道电阻、jfet电阻、漂移层电阻、衬底电阻、接触电阻等。其中,沟道电阻和jfet电阻的占比较高,并且受到mosfet元胞结构参数的影响。影响mosfet比导通电阻的主要参数为总沟道宽度与jfet区域总面积,这两个参数分别对应影响上述的沟道电阻和jfet电阻。由于圆形和正多边形元胞设计的mosfet器件,可以实现较高的沟道宽度和结型场效应管jfet区域总面积,进而有较低的比导通电阻。因此,本技术实施例中的元胞形状以正多边形或圆形进行设计。

30.进一步地,第一高掺杂p型区域105和结势垒肖特基区域114形成的部分元胞区域,与阱区103和结型场效应管jfet区域113形成的部分元胞区域,在每行每列中呈现交替排列的分布形态。

31.图2为本技术实施例提供的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区截面图。图3为本技术实施例提供的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区另一方向截面图。需要说明的是,图1中的虚线aa’所对应的截面图即为图2所示的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区截面图,图1中的虚线bb’所对应的截面图即为图3所示的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区另一方向截面图。可以理解的是,图1中的虚线aa’为折线,经过点b’。

32.如图2所示,集成结势垒肖特基二极管的平面型功率mosfet器件包括外延层102;其中,外延层为n型区域。在外延层的第一侧表面分布有复合元胞。复合元胞包括:阱区103、源极区域104、第一高掺杂p型区域105及结势垒肖特基区域114。结势垒肖特基区域114包含预设数量个第二高掺杂p型区域,以及在高掺杂p型区域之间形成的肖特基区域。需要说明的是,预设数量的范围为1~10个。

33.进一步地,如图1所示,第一高掺杂p型区域105的下半部分与阱区103接触,源极区

域104环绕第一高掺杂p型区域105,第一高掺杂p型区域105环绕结势垒肖特基区域114。另外,可以理解的是,源极区域104位于阱区103内部;在图2所示的种集成结势垒肖特基二极管的平面型功率mosfet器件有源区截面图中,结势垒肖特基区域包含的第二高掺杂p型区域的预设数量为1。

34.需要说明的是,阱区103与第一高掺杂p型区域105均为p型区域、源极区域104为n型区域,结势垒肖特基区域中的第二高掺杂p型区域117为p型区域,结势垒肖特基区域中的肖特基区域为n型区域。阱区103与外延层间102间形成第一pn结115,阱区103与源极区域104间形成第二pn结116;结势垒肖特基区域114内的预设数量个第二高掺杂p型区域117与外延层102间形成第三pn结118。

35.在本技术的一个实施例中,阱区103的离子掺杂浓度范围为:5e15cm-3

~5e18cm-3

;源极区域104的离子掺杂浓度范围为:1e18cm-3

~1e22cm-3

;第一高掺杂p型区域105与第二高掺杂p型区域117的离子掺杂浓度范围为:1e18cm-3

~1e22cm-3

。

36.需要说明的是,由于jfet区域113的宽度n和离子注入浓度的设计,需要保证mosfet具有较小的导通压降,并且在阻断模式下,相邻的阱区间可以起到有效的电场屏蔽效应作用,确保器件的可靠性。同理,结势垒肖特基区域中的肖特基区域的宽度s和离子注入浓度的设计,需要保证肖特基二极管具有足够的电流导通能力,并且在阻断模式下,相邻的阱区间可以起到有效的电场屏蔽效应作用,确保器件的可靠性。因此,在本技术实施例中,jfet区域的宽度n的取值范围与肖特基区域的宽度s的取值范围均在预设区间内;jfet区域113与肖特基区域的离子掺杂浓度均大于或等于外延层102的离子掺杂浓度。这样设计可以使mosfet器件具有较小的导通压降,以及在阻断模式下,相邻的阱区间可以起到有效的电场屏蔽作用。

37.在本技术的一个实施例中,预设区间为0.8um~5um;jfet区域113与肖特基区域的离子掺杂浓度范围为:1e15cm-3

~5e17cm-3

。

38.在本技术的一个实施例中,集成结势垒肖特基二极管的平面型功率mosfet器件还包括:碳化硅衬底101与漏极电极112。

39.如图2所示,碳化硅衬底101的第一侧表面与外延层102的第二侧表面接触;其中,碳化硅衬底101为n型区域;漏极电极112覆盖于碳化硅衬底101的第二侧表面;碳化硅衬底101的离子掺杂浓度大于外延层102的离子掺杂浓度。

40.在本技术的一个实施例中,碳化硅衬底101的离子掺杂浓度范围为:1e18cm-3

~1e20cm-3

,外延层102的离子掺杂浓度范围为:1e14cm-3

~5e16cm-3

。

41.在本技术的一个实施例中,集成结势垒肖特基二极管的平面型功率mosfet器件还包括:欧姆接触金属109与肖特基接触金属110。

42.如图2所示,欧姆接触金属109覆盖于第一高掺杂p型区域105及部分源极区域104表面,欧姆接触金属109与第一高掺杂p型区域105间形成第一欧姆接触,另外,为了抑制mosfet器件内部的寄生双极晶体管效应,欧姆接触金属109还与源极区域104间形成第二欧姆接触;其中,形成的第一欧姆接触与第二欧姆接触相互连接。肖特基接触金属110覆盖于结势垒肖特基区域114的表面,与肖特基区域间形成肖特基接触。

43.在本技术的一个实施例中,集成结势垒肖特基二极管的平面型功率mosfet器件还包括:绝缘栅极氧化层106与栅极导电多晶硅107。

44.如图2所示,绝缘栅极氧化层106覆盖于jfet区域113与阱区104上,绝缘栅极氧化层106的边界位于源极区域104上;栅极导电多晶硅107覆盖于绝缘栅极氧化层106上,栅极导电多晶硅107的宽度小于或等于绝缘栅极氧化层106的宽度。

45.在本技术的一个实施例中,集成结势垒肖特基二极管的平面型功率mosfet器件还包括:绝缘介质层108。

46.如图2所示,绝缘介质层108覆盖于绝缘栅极氧化层106与栅极导电多晶硅107上。

47.在本技术的一个实施例中,集成结势垒肖特基二极管的平面型功率mosfet器件还包括:源极电极111。

48.如图2所示,源极电极111与欧姆接触金属109及肖特基接触金属110接触;另外,绝缘介质层108将栅极导电多晶硅107与源极金属111分隔开。

49.图4为本技术实施例提供的一种圆形复合元胞结构示意图。图4中的虚线aa’所对应的截面图即为图2所示的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区截面图;图4中的虚线bb’所对应的截面图即为图3所示的一种集成结势垒肖特基二极管的平面型功率mosfet器件有源区另一方向截面图。

50.本技术中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于装置实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

51.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、商品或者设备中还存在另外的相同要素。

52.以上所述仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。