1.本发明涉及一种半导体结构的制造方法,尤其涉及一种三维(3d)系统单芯片 (system-on-chip;soc)的制造方法及三维系统单芯片。

背景技术:

2.随着电子产业的蓬勃发展,电子产品逐渐进入多功能、高性能的研发方向,其中半导体 科技已广泛地应用于制造存储器、中央处理单元等芯片组。为了达成高集成度(integration)与 高速度等目的,半导体集成电路的尺寸持续地缩减,目前已发展出多种不同的材料与技术以 达成上述的集成度与速度要求。

3.一般来说,在集成电路(integrated circuit;ic)芯片中可设计并嵌入多个装置/元件(例如, 晶体管、二极管等),接着将该芯片置于封装件(例如,塑胶壳)中或用作裸芯片以置于电子装 置的印刷电路板(printed circuit board;pcb)上。除晶体管级的传统技术节点微缩以外,正越 来越多地利用三维(three-dimensional;3d)ic芯片堆叠以继续使用当前的半导体制造技术来创 建三维系统单芯片(3d soc)装置并为满足各种电子装置的性能、功率及频宽要求提供解决方 案。3d soc装置可包括不同技术节点的数个逻辑、存储器、类比或其它芯片,而如何将逻辑、 存储器、类比等芯片堆叠以构成3维系统单芯片,成为当前相关领域极需研究的目标。

技术实现要素:

4.本发明提供了一种3d soc的制造方法及3d soc,使3d soc可满足高集成度与速度要 求,而具有更佳的电气特性及效率。

5.本发明所提供的三维系统单芯片的制造方法包括:提供存储器晶圆结构,包括晶圆、第 一主动层及第一重布线层,第一主动层形成于晶圆,第一重布线层形成于第一主动层;设置 多个第一导电结构、核心晶粒结构、及多个输入/输出晶粒结构于第一重布线层,其中输入/ 输出晶粒结构设置于核心晶粒结构的周边,其中,每一核心晶粒结构及每一输入/输出晶粒结 构包括半导体基板、停止层结构、第二主动层、多个第二导电结构及第二重布线层,半导体 基板具有相对的主动面及背面,停止层结构形成于半导体基板内,将半导体基板分为基板第 一部分及基板第二部分,其中基板第一部分位于停止层结构及主动面之间,基板第二部分位 于停止层结构及背面之间,第二主动层形成于主动面,第二导电结构形成于基板第一部分以 连接第二主动层及停止层结构,第二重布线层形成于第二主动层,每一核心晶粒结构的第二 重布线层及每一输入/输出晶粒结构的第二重布线层接合于第一重布线层;进行背面研磨制 程,自半导体基板的背面进行研磨,以移除基板第二部分的一部分;进行介电填充制程,以 形成介电层包复核心晶粒结构、输入/输出晶粒结构、以及第一导电结构;进行薄化制程,移 除部分的介电层、剩余的基板第二部分及部分的停止层结构,以显露第一导电结构及第二导 电结构;形成第三重布线层于介电层上,且第三重布线层与显露的第一导电结构及第二导电 结构电性连接;形成多个焊球于第三重布线层;

以及进行切单。

6.本发明所提供的三维系统单芯片的制造方法包括:提供多个存储器晶粒,每一存储器晶 粒包括晶粒基板、第一主动层及第一重布线层,第一主动层形成于晶粒基板,第一重布线层 形成于第一主动层;提供soc晶圆结构,分隔成独立的核心晶粒区及多个输入/输出晶粒区, 输入/输出晶粒区设置于核心晶粒区的周边,soc晶圆结构包括半导体晶圆、停止层结构、第 二主动层、多个导电结构及第二重布线层,半导体晶圆具有相对的主动面及背面,停止层结 构形成于半导体晶圆内,将半导体晶圆分为晶圆第一部分及晶圆第二部分,其中晶圆第一部 分位于停止层结构及主动面之间,晶圆第二部分位于停止层结构及背面之间,第二主动层形 成于主动面,导电结构形成于晶圆第一部分以连接第二主动层及停止层结构,第二重布线层 形成于第二主动层;将每一存储器晶粒的第一重布线层接合至soc晶圆结构的核心晶粒区的 第二重布线层;进行介电填充制程,以形成介电层包覆存储器晶粒;进行背面研磨制程,自 半导体晶圆的背面进行研磨,以移除晶圆第二部分的一部分;进行薄化制程,移除剩余的晶 圆第二部分及部分的停止层结构,以显露导电结构;形成第三重布线层于残留的部分停止层 结构,且第三重布线层与显露的导电结构电性连接;形成多个焊球于第三重布线层;以及进 行切单。

7.本发明所提供的三维系统单芯片的制造方法包括:提供存储器晶圆结构,包括晶圆、第 一主动层及第一重布线层,第一主动层形成于晶圆,第一重布线层形成于第一主动层;提供 soc晶圆结构,分隔成独立的核心晶粒区、及多个输入/输出晶粒区,输入/输出晶粒区设置于 核心晶粒区的周边,soc晶圆结构包括半导体晶圆、停止层结构、第二主动层、多个导电结 构及第二重布线层,半导体晶圆具有相对的主动面及背面,停止层结构形成于半导体晶圆内, 将半导体晶圆分为晶圆第一部分及晶圆第二部分,其中晶圆第一部分位于停止层结构及主动 面之间,晶圆第二部分位于停止层结构及背面之间,第二主动层形成于主动面,导电结构形 成于晶圆第一部分以连接第二主动层及停止层结构,第二重布线层形成于第二主动层;将存 储器晶圆结构的第一重布线层接合至soc晶圆结构的第二重布线层;进行背面研磨制程,自 半导体晶圆的背面进行研磨,以移除晶圆第二部分的一部分;进行薄化制程,移除剩余的晶 圆第二部分及部分的停止层结构,以显露导电结构;形成第三重布线层于晶圆第一部分,且 第三重布线层与显露的导电结构电性连接;形成焊球于第三重布线层;以及进行切单。

8.在本发明的一实施例中,上述的停止层结构包括相互堆叠的第一停止层及第二停止层, 第一停止层的材料不同于第二停止层的材料,第二停止层介于第一停止层及第二主动层之间, 在进行薄化制程中,移除部分的停止层结构的步骤包括先移除第一停止层,再移除部分第二 停止层。

9.在本发明的一实施例中,上述的第一停止层为氮化硅层,该第二停止层为二氧化硅层。

10.在本发明的一实施例中,上述的氮化硅层及二氧化硅层的形成步骤包括先于半导体基板 (半导体晶圆)的第一深度进行氮离子注入制程,再于半导体基板(半导体晶圆)的第二深度进行 氧离子注入制程,且第二深度小于第一深度,接着进行高温处理制程,使氮离子注入的区域 形成氮化硅层,氧离子注入的区域形成二氧化硅层。

11.在本发明的一实施例中,上述的氮化硅层及二氧化硅层的移除方法选自化学机械

抛光及 等离子干式蚀刻其中的一种,其中氮化硅及二氧化硅的选择比介于10至20之间,二氧化硅 及硅的选择比约为5。

12.在本发明的一实施例中,上述的薄化制程包括:第一去除步骤,移除部分的介电层及剩 余的基板第二部分(晶圆第二部分);以及第二去除步骤,移除部分的停止层结构,以显露第 二导电结构(导电结构)。

13.在本发明的一实施例中,上述的第一去除步骤选自化学机械抛光、湿式蚀刻及等离子干 式蚀刻其中的一种,第二去除步骤选自化学机械抛光及等离子干式蚀刻其中的一种。

14.在本发明的一实施例中,上述的第二重布线层以混合键合技术接合于第一重布线层。

15.本发明所提供的三维系统单芯片包括存储器芯片结构、多个第一导电结构、核心晶粒、 多个输入/输出晶粒、介电层、第三重布线层及多个焊球。存储器芯片结构包括半导体基板、 第一主动层及第一重布线层,第一主动层形成于半导体基板,第一重布线层形成于第一主动 层;第一导电结构、核心晶粒及输入/输出晶粒设置于第一重布线层,其中输入/输出晶粒设置 于核心晶粒的周边,其中,核心晶粒及输入/输出晶粒包括基板、停止层结构、第二主动层、 多个第二导电结构及第二重布线层,第二主动层及停止层结构分别设置于基板的相对两侧, 第二导电结构形成于基板,每一第二导电结构的一端连接于第二主动层,每一第二导电结构 的另一端穿透且显露于停止层结构,第二重布线层形成于第二主动层,核心晶粒区的第二重 布线层及输入/输出晶粒区的第二重布线层接合于第一重布线层;介电层填充于核心晶粒、输 入/输出晶粒、以及第一导电结构之间,且显露停止层结构及第一导电结构的一端;第三重布 线层形成于介电层,且第三重布线层与显露的第一导电结构及显露的第二导电结构电性连接; 焊球形成于第三重布线层。

16.本发明所提供的三维系统单芯片包括多个存储器晶粒、介电层、soc芯片、第三重布线 层及焊球。每一存储器晶粒包括晶粒基板、第一主动层及第一重布线层,第一主动层形成于 晶粒基板,第一重布线层形成于第一主动层;介电层包覆存储器晶粒,且显露每一存储器晶 粒的第一重布线层;soc芯片分隔成独立的核心晶粒及多个输入/输出晶粒,输入/输出晶粒设 置于核心晶粒的周边,soc芯片包括基板、停止层结构、第二主动层、多个导电结构及第二 重布线层,第二主动层及停止层结构分别设置于基板相对两侧,导电结构形成于基板,每一 导电结构的一端连接于第二主动层,每一导电结构的另一端穿透且显露于停止层结构,第二 重布线层形成于第二主动层,每一存储器晶粒的第一重布线层接合至核心晶粒的第二重布线 层;第三重布线层形成于停止层结构,且第三重布线层与显露的导电结构电性连接;焊球形 成于第三重布线层。

17.本发明所提供的三维系统单芯片包括存储器芯片结构、soc芯片、第三重布线层及焊球。 存储器芯片结构包括半导体基板、第一主动层及第一重布线层,第一主动层形成于半导体基 板,第一重布线层形成于第一主动层;soc芯片分隔成独立的核心晶粒及多个输入/输出晶粒, 输入/输出晶粒设置于核心晶粒的周边,soc芯片包括基板、停止层结构、第二主动层、多个 导电结构及第二重布线层,第二主动层及停止层结构分别设置于基板的相对两侧,导电结构 形成于基板,每一导电结构的一端连接于第二主动层,每一导电结构的另一端穿透且显露于 停止层结构,第二重布线层形成于第二主动层,每一存储器晶粒的第

一重布线层接合至核心 晶粒的第二重布线层;第三重布线层形成于停止层结构,且第三重布线层与显露的导电结构 电性连接;焊球形成于第三重布线层。

18.本发明三维系统单芯片中,存储器芯片可被接合至由介电层所包覆的核心晶粒及多个输 入/输出晶粒,或者soc芯片可被接合至由介电层所包覆多个存储器晶粒,或者存储器芯片及 soc芯片相互接合。其中核心晶粒、输入/输出晶粒、或者是soc芯片,借由其中停止层结构 的设置,皆可薄化而具有非常薄的厚度,如此使得三维系统单芯片的整体厚度大幅减少,可 满足高集成度与速度要求,而具有更佳的电气特性及效率。

19.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依 照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易 懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

20.图1a至图1i所示是本发明第一实施例三维系统单芯片的制造方法的剖面示意图。

21.图2是本发明第一实施例三维系统单芯片的剖面结构示意图。

22.图3是本发明实施例三维系统单芯片的仰视示意图。

23.图4a至图4h所示是本发明第二实施例三维系统单芯片的制造方法的剖面示意图。

24.图5是本发明第二实施例三维系统单芯片的剖面结构示意图。

25.图6是本发明第二实施例三维系统单芯片的仰视示意图。

26.图7a至图7e是所示本发明第三实施例三维系统单芯片的制造方法的剖面示意图。

27.图8是本发明第三实施例三维系统单芯片的剖面结构示意图。

具体实施方式

28.图1a至图1i所示是本发明第一实施例三维系统单芯片的制造方法的剖面示意图。如图 1a所示,提供存储器晶圆结构10,包括晶圆12、第一主动层14及第一重布线层16,第一 主动层14形成于晶圆12上,第一重布线层16形成于第一主动层14上。于一实施例中,晶 圆12例如为硅晶圆、磊晶硅晶圆、硅锗晶圆、碳化硅晶圆;第一主动层14上例如形成有晶 体管元件等存储器的基本元件;第一重布线层16上例如形成有金属布线、金属柱(via)及微 凸块。

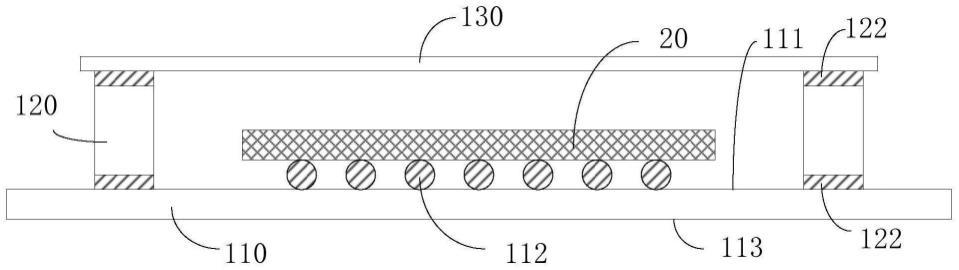

29.如图1b所示,设置多个第一导电结构18于第一重布线层16上,第一导电结构18例如 为导电柱;如图1c所示,设置核心晶粒结构20及多个输入/输出晶粒结构22于第一重布线 层16,其中输入/输出晶粒结构22设置于核心晶粒结构20的周边,第一导电结构18介于输 入/输出晶粒结构22及核心晶粒结构20之间。每一核心晶粒结构20及每一输入/输出晶粒结 构22的结构及配置大致相同,两者的差异主要在于核心晶粒结构20及输入/输出晶粒结构22 中主动层内的不同电气元件配置,因此底下以相同的元件符号标示核心晶粒结构20及输入/ 输出晶粒结构22中对应或相同的结构。

30.请继续参阅图1c所示,核心晶粒结构20及输入/输出晶粒结构22包括半导体基板24、 停止层结构26、第二主动层28、多个第二导电结构30及第二重布线层32,半导体基板24 具有相对的主动面241及背面242,停止层结构26形成于半导体基板24内,将半导体基板 24分为基板第一部分243及基板第二部分244,其中,将停止层结构26至主动面241之间的 半

导体基板24称为基板第一部分243,将停止层结构26至背面242之间的半导体基板24称 为基板第二部分244,因此基板第一部分243位于停止层结构26及主动面241之间,基板第 二部分244位于停止层结构26及背面242之间。又第二主动层28形成于主动面241,于一 实施例中,第二主动层28上例如形成有金属氧化物半导体(mos)等电气元件。多个第二导电 结构30形成于基板第一部分243以连接第二主动层28及停止层结构26,于一实施例中,第 二导电结构30例如为导电柱。第二重布线层32形成于第二主动层28,第二重布线层32上 例如形成有金属布线、金属柱(via)及微凸块。如图1c所示,于一实施例中,核心晶粒结构 20的第二重布线层32及输入/输出晶粒结构22的第二重布线层32以混合键合技术接合于第 一重布线层16。

31.于一实施例中,停止层结构26包括相互堆叠的第一停止层261及第二停止层262,第一 停止层261的材料不同于第二停止层262的材料,第二停止层262介于第一停止层261及第 二主动层28之间,其中第一停止层261例如为氮化硅(si3n4)层,第二停止层262例如为二氧 化硅(sio2)层。停止层结构26的制造包括进行离子注入制程及高温处理制程,其中,离子注 入制程包括先在半导体基板24的距离主动面241的第一深度d1进行氮离子注入制程,再于 半导体基板24的距离主动面241的第二深度d2进行氧离子注入制程,氧离子注入区的第二 深度d2较氮离子注入区的第一深度d1小,亦即氧离子注入区较为靠近主动面241。之后进 行高温处理,在氮离子注入区形成氮化硅层(即第一停止层261),在氧离子注入区形成二氧化 硅层(即第二停止层262),其中,第二停止层262较为邻近主动面241,第一停止层261较为 邻近背面242。

32.如图1d所示,进行背面研磨(grind)制程,自半导体基板24的背面242进行研磨,以移 除基板第二部分244的一部分,如图1d所示,残留厚度极薄的基板第二部分244'。

33.如图1e所示,进行介电填充制程,以形成介电层34包覆核心晶粒结构20、输入/输出晶 粒结构22、以及第一导电结构18。接着,进行薄化制程,移除部分的介电层34、剩余的基 板第二部分244'及部分的停止层结构26,以显露第一导电结构18及第二导电结构30。于一 实施例中,薄化制程包括第一去除步骤及第二去除步骤,第一去除步骤用以去除残留的基板 第二部分244'以及部分的介电层34,如图1f所示,以显露出停止层结构26,例如为显露第 一停止层261,第一去除步骤例如为选自化学机械抛光、湿式蚀刻及等离子干式蚀刻其中一 种制程,于一实施例中,基板第二部分244'的材料为硅,第一停止层261的材料为氮化硅, 当第一去除步骤选用化学机械抛光制程时,硅及氮化硅的选择比例如为20,亦即si/si3n4为 20。

34.接续上述说明,第二去除步骤用以移除部分的停止层结构26,亦即依序移除第一停止层 261及部分第二停止层262,如图1g所示,以显露第一导电结构18及第二导电结构30,第 二去除步骤例如为选自化学机械抛光及等离子干式蚀刻其中一种制程。于一实施例中,第一 停止层261例如为氮化硅(si3n4)层,第二停止层262例如为二氧化硅(sio2)层,在第二去除步 骤中,先以化学机械抛光制程移除氮化硅层(第一停止层261),以显露二氧化硅层(第二停止 层262),其中氮化硅及二氧化硅的选择比例如介于10至20之间,亦即si3n4/sio2介于10至 20;再以另一化学机械抛光制程移除部分二氧化硅层(第二停止层262),以残留极薄的二氧化 硅层(第二停止层262')且显露第一导电结构18及第二导电结构30,其中二氧化硅及硅的选择 比约为5,亦即sio2/si为5。如此使得核心晶粒结构20(标示于图

1e)及输入/输出晶粒结构 22(标示于图1e)皆被薄化,此薄化后的核心晶粒结构20及输入/输出晶粒结构22例如分别称 为核心晶粒20a及输入/输出晶粒22a。

35.具体而言,核心晶粒20a及输入/输出晶粒22a包括基板(即基板第一部分243)、停止层 结构26的残留的第二停止层262'、第二主动层28、第二导电结构30及第二重布线层32,第 二主动层28及第二停止层262'分别设置于基板(即基板第一部分243)的相对两侧,第二导电 结构30形成于基板(即基板第一部分243),第二导电结构30的一端连接于第二主动层28, 第二导电结构30的另一端穿透且显露于第二停止层262',第二重布线层32形成于第二主动 层28。

36.如图1h所示,形成第三重布线层36于介电层34及部分残留且极薄的第二停止层262' 上,第三重布线层36并与显露的第一导电结构18及第二导电结构30电性连接,其中第三重 布线层36与第二停止层262'之间具有较佳的粘着性,因此第三重布线层36不易剥离。如图 1i所示,于第三重布线层36上形成多个焊球38,于一实施例中,焊球38借由第三重布线层 36以分别与例如第一导电结构18及第二导电结构30电性连接;之后,并于进行晶圆针测(chipprobing,cp),以进行电性功能上的测试(test)后,进行切单(die saw),以完成三维系统单 芯片。

37.图2是本发明第一实施例三维系统单芯片的剖面结构示意图,在图2中,并进一步绘示 了将三维系统单芯片40设置于电路板42或软板上,以借由焊球38与电路板42或软板进行 电性连接。如图2所示,三维系统单芯片40包括存储器芯片结构10a、多个第一导电结构 18、核心晶粒20a、多个输入/输出晶粒22a、介电层34、第三重布线层36及多个焊球38。 其中存储器芯片结构10a为上述存储器晶圆结构10(标示于图1a)进行切单后的型态,于一实 施例中,存储器芯片结构10a包括半导体基板44、第一主动层14及第一重布线层16,第一 主动层14形成于半导体基板44,第一重布线层16形成于第一主动层14。第一导电结构18、 核心晶粒20a、输入/输出晶粒22a设置于第一重布线层16,其中输入/输出晶粒22a设置于 核心晶粒20a的周边,第一导电结构18介于输入/输出晶粒22a及核心晶粒20a之间。核心 晶粒20a及输入/输出晶粒22a的结构已叙述于上,于此不再赘述。核心晶粒结构20a及输 入/输出晶粒22a的第二重布线层32接合于第一重布线层16;介电层34填充于核心晶粒20a、 输入/输出晶粒22a、以及第一导电结构18之间,且显露停止层结构26的残留第二停止层262' 及第二导电结构30的一端;第三重布线层36形成于介电层34及残留第二停止层262',且第 三重布线层36与显露的第一导电结构18及显露的第二导电结构30电性连接;多个焊球38 形成于第三重布线层36。

38.图3是本发明一实施例三维系统单芯片的仰视示意图,亦即由焊球侧观看,如图3所示, 多个焊球38排列于第三重布线层36上,图3中并以虚线标示核心晶粒20a及输入/输出晶粒 22a的位置配置,其中输入/输出晶粒22a位于核心晶粒20a的周边。于一实施例中,多个 焊球38可包括信号焊球381及电源/接地焊球382,其中部分的电源/接地焊球382可供提供 核心晶粒20a及输入/输出晶粒22a电源或接地,部分的电源/接地焊球382亦可供经由第三 重布线层36及第一导电结构18提供存储器芯片结构10a电源或接地,又部分的信号焊球381 可供作为输入/输出晶粒22a的信号传出入媒介,其中,输入/输出晶粒22a的信号可例如来 自核心晶粒20a及/或电路板42,又核心晶粒20a与存储器芯片结构10a之间具有例如三级 缓存(l3 cache)的存取机制。

39.图4a至图4h所示是本发明第二实施例三维系统单芯片的制造方法的剖面示意图。如图 4a所示,提供soc晶圆结构50,分隔成独立的核心晶粒区501及多个输入/输出晶粒区502, 输入/输出晶粒区502设置于核心晶粒区501的周边,soc晶圆结构50包括半导体晶圆52、 停止层结构54、第二主动层56、多个导电结构58及第二重布线层60。半导体晶圆52具有 相对的主动面521及背面522,停止层结构54形成于半导体晶圆52内,将半导体晶圆52分 为晶圆第一部分523及晶圆第二部分524,其中晶圆第一部分523位于停止层结构54及主动 面521之间,晶圆第二部分524位于停止层结构54及背面522之间。于一实施例中,停止层 结构54包括相互堆叠的第一停止层541及第二停止层542,第一停止层541的材料不同于第 二停止层542的材料,第二停止层542介于第一停止层541及主动面521之间,其中第一停 止层541例如为氮化硅(si3n4)层,第二停止层542例如为二氧化硅(sio2)层。停止层结构54 的制造与第一实施例所揭示的停止层结构26的制造流程相同或相近,于此不再赘述。

40.接续上述说明,第二主动层56形成于半导体晶圆52的主动面521;导电结构58形成于 晶圆第一部分523以连接第二主动层56及停止层结构54,于一实施例中,导电结构58例如 为导电柱;又第二重布线层60形成于第二主动层56,第二重布线层60上例如形成有金属布 线、金属柱(via)及微凸块。

41.如图4b所示,提供多个存储器晶粒62,图4b中仅绘示三个存储器晶粒62,惟不限于此。每一存储器晶粒62包括晶粒基板64、第一主动层66及第一重布线层68。第一主动层66形成于晶粒基板64,第一主动层66上例如形成有晶体管元件等存储器的基本元件。第一重布线层68形成于第一主动层66,第一重布线层68上例如形成有金属布线、金属柱(via)及微凸块。如图4b所示,多个存储器晶粒62倒置,且每一存储器晶粒62的第一重布线层68接合至soc晶圆结构50的核心晶粒区501的第二重布线层60,于一实施例中,第一重布线层68以混合键合技术接合于第二重布线层60。

42.如图4c所示,进行介电填充制程,以形成介电层70包覆存储器晶粒62,于一实施例中, 介电层70设置于soc晶圆结构50上且填充于多个存储器晶粒62之间,介电层70的顶面与 存储器晶粒62的晶粒基板64平齐。

43.之后,进行背面研磨制程,自半导体晶圆52的背面522进行研磨,以移除晶圆第二部分 524的一部分,如图4d所示,残留厚度极薄的晶圆第二部分524'。接着进行薄化制程,移除 剩余的晶圆第二部分524'及部分的停止层结构54,以显露导电结构58。于一实施例中,薄化 制程包括第一去除步骤及第二去除步骤,第一去除步骤用以去除残留的晶圆第二部分524', 如图4e所示,以显露出停止层结构54,例如为显露第一停止层541;第二去除步骤用以移除 部分的停止层结构54,亦即依序移除第一停止层541及部分第二停止层542,如图4f所示, 以显露导电结构58且残留极薄的第二停止层542'。第一去除步骤及第二去除步骤所可选择的 制程及方法已揭示于第一实施例中,于此不再赘述。借由薄化制程使得soc晶圆结构50(标 示于图4a)被薄化,形成薄化soc晶圆结构50'。

44.如图4g所示,形成第三重布线层72于部分残留且极薄的第二停止层542'上,第三重布 线层72并与显露的导电结构58电性连接,其中第三重布线层72与第二停止层542'之间具有 较佳的粘着性,因此第三重布线层72不易与薄化soc晶圆结构50'剥离。如图4h所示,于 第三重布线层72上形成多个焊球74,于一实施例中,焊球74借由第三重布线层72以分别 与例如导电结构58电性连接;之后,并于进行晶圆针测,以进行电性功能上的测试后,

进行 切单,以完成三维系统单芯片。

45.图5是本发明第二实施例三维系统单芯片的剖面结构示意图,在图5中,并进一步绘示 了将三维系统单芯片80设置于电路板42或软板上,以借由焊球74与电路板42或软板进行 电性连接。如图5所示,三维系统单芯片80包括多个存储器晶粒62、介电层70、soc芯片 50a、第三重布线层72及多个焊球74。其中每一存储器晶粒62的结构已揭示于图4b的叙述 中,于此不再赘述;介电层70填充于存储器晶粒62之间;soc芯片50a为上述薄化soc晶 圆结构50'(标示于图4f)进行切单后的型态,soc芯片50a分隔成独立的核心晶粒501a及多 个输入/输出晶粒502a,输入/输出晶粒502a设置于核心晶粒501a的周边,soc芯片50a 包括基板52a(即晶圆第一部分523经切单后)、停止层结构54的残留第二停止层542'、第二 主动层56、多个导电结构58及第二重布线层60,第二主动层56及残留第二停止层542'分别 设置于基板52a的相对两侧,导电结构58形成于基板52a,每一导电结构58的一端连接于 第二主动层56,每一导电结构58的另一端穿透且显露于残留第二停止层542'。多个被介电 层70所包覆的存储器晶粒62的第一重布线层68接合至核心晶粒502a的第二重布线层60; 第三重布线层72形成于残留第二停止层542',且第三重布线层72与显露的导电结构58电性 连接;多个焊球74形成于第三重布线层72。

46.图6是本发明第二实施例三维系统单芯片的仰视示意图,亦即由焊球74侧观看,如图6 所示,多个焊球74排列于第三重布线层72上,图6中以长虚线标示核心晶粒501a及输入/ 输出晶粒502a的位置配置,其中输入/输出晶粒502a位于核心晶粒501a的周边;图6中并 以点状虚线标示存储器晶粒62的配置位置,如图所示,存储器晶粒62主要对应核心晶粒501a 设置,图中虽绘示了6个存储器晶粒62,惟不限于此。

47.接续上述说明,于一实施例中,多个焊球74可包括信号焊球741及电源/接地焊球742, 其中电源/接地焊球742可供提供核心晶粒501a、输入/输出晶粒502a及存储器晶粒62电源 或接地;又部分的信号焊球741可供作为输入/输出晶粒502a的信号传出入媒介,其中,输 入/输出晶粒502a的信号可例如来自核心晶粒501a及/或电路板42,又核心晶粒501a与存 储器晶粒62之间具有例如三级缓存(l3 cache)的存取机制。

48.图7a至图7e是所示本发明第三实施例三维系统单芯片的制造方法的剖面示意图,如图 7a所示,提供存储器晶圆结构10及提供soc晶圆结构50。存储器晶圆结构10包括晶圆12、 第一主动层14及第一重布线层16,第一主动层14形成于晶圆12上,第一重布线层16形成 于第一主动层14上,存储器晶圆结构10的进一步特征已揭示于第一实施例中,于此不再赘 述。soc晶圆结构50分隔成独立核心晶粒区501及多个输入/输出晶粒区502,输入/输出晶 粒区502设置于核心晶粒区501的周边,soc晶圆结构50包括半导体晶圆52、停止层结构 54、第二主动层56、多个导电结构58及第二重布线层60,soc晶圆结构50的结构及配置已 揭示于第二实施例中,于此不再赘述。

49.如图7b所示,将存储器晶圆结构10的第一重布线层16接合至soc晶圆结构50的第二 重布线层60;之后对soc晶圆结构50依序进行背面研磨制程及薄化制程,如图7c所示,以 显露导电结构58的一端且残留极薄的第二停止层542',其中背面研磨制程及薄化制程已揭示 于第二实施例中,于此不再赘述。

50.如图7d所示,形成第三重布线层72于部分残留且极薄的第二停止层542'上,第三重布 线层72与显露的导电结构58电性连接;接着,如图7e所示,于第三重布线层72上形成

多 个焊球74,于一实施例中,焊球74借由第三重布线层72以分别与例如导电结构58电性连 接;之后,并于进行晶圆针测,以进行电性功能上的测试后,进行切单,以完成三维系统单 芯片。

51.图8是本发明第三实施例三维系统单芯片的剖面结构示意图,在图8中,并进一步绘示 了将三维系统单芯片90设置于电路板42或软板上,以借由焊球74与电路板42或软板进行 电性连接。如图8所示,三维系统单芯片90包括存储器芯片结构10a、soc芯片50a、第三 重布线层72及多个焊球74。其中存储器芯片结构10a为存储器晶圆结构10(标示于图7a) 进行切单后的型态,soc芯片50a为薄化soc晶圆结构50'(标示于图7c)进行切单后的型态。 存储器芯片结构10a的第一重布线层16与soc芯片50a的第二重布线层60以面对面的方 式接合在一起,于一实施例中,第一重布线层16以混合键合技术接合于第二重布线层60。 第三重布线层72形成于残留第二停止层542',且第三重布线层72与显露的导电结构58电性 连接;多个焊球74形成于第三重布线层72。

52.根据上述,在本发明一实施例中,三维系统单芯片包括存储器芯片以及被介电层所包覆 的核心晶粒及多个输入/输出晶粒,其中输入/输出晶粒位于核心晶粒周边,且存储器芯片与核 心晶粒接合;在本发明一实施例中,三维系统单芯片包括soc芯片以及被介电层所包覆多个 存储器晶粒,soc芯片包括独立的核心晶粒及多个位于核心晶粒周边的输入/输出晶粒,且核 心晶粒与多个存储器晶粒接合;在本发明一实施例中,三维系统单芯片包括存储器芯片与soc 芯片,soc芯片包括独立的核心晶粒及多个位于核心晶粒周边的输入/输出晶粒,且核心晶粒 与存储器芯片接合。在本发明实施例三维系统单芯片中,无论是核心晶粒、输入/输出晶粒, 或者是soc芯片,借由其中停止层结构的设置,皆可薄化而具有非常薄的厚度,例如核心晶 粒、输入/输出晶粒,或者是soc芯片的整体厚度不大于12微米,如此使得三维系统单芯片 的整体厚度大幅减少,可满足高集成度与速度要求,而具有更佳的电气特性及效率。

53.以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本 发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱 离本发明技术方案范围内,当可利用上述揭示的方法及技术内容作出些许的更动或修饰为等 同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上 实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。