一种COB灯带基板的制作方法

- 国知局

- 2024-06-21 10:29:03

本技术涉及cob灯带,具体涉及一种cob灯带基板。

背景技术:

1、cob灯是"chip-on-board灯"的缩写,中文意为"芯片贴片灯"。它是一种led(lightemitting diode,发光二极管)照明技术,其中多个led芯片直接封装在一个小型电路板(通常是陶瓷或金属基板)的表面上,而不是使用传统的led封装。这些led芯片非常紧密地排列在一起,几乎形成了一个连续的光源,因此cob灯通常具有均匀的光线分布和高亮度。

2、现有技术中:

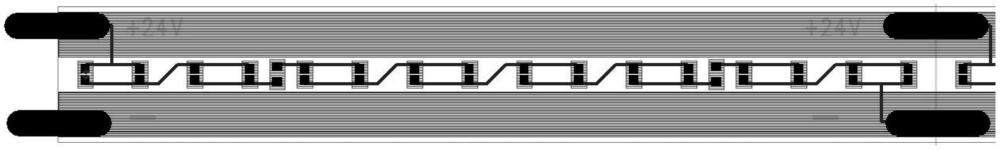

3、1.cob灯带的基板尺寸:cob灯带的基板长度为长卷,整卷基板宽度为118.92mm,经过分切后,每单条的宽度为7.928mm,15条单条基板通过组合拼板的方式形成整卷。

4、2.基板线路:在一般线路图中,芯片的固晶焊盘位置位于上下导线的中间部位。

5、3.芯片固晶焊盘间距:芯片的固晶焊盘正负极之间的间距为0.15mm。

6、基于现有技术的上述特征,带来了一些缺陷:

7、1.cob灯带的基板尺寸导致固晶、拉胶、分板切割生产效率低。

8、2.芯片固晶焊盘位置横穿于上下导线中间部位,因cob灯带fpc基板为柔性线路板,在生产过程中、运输过程中、客户端安装使用过程中会产生一定外力,会导致cob灯带产生一定弯曲,导致芯片电极容易脱落产生死灯,先前这种线路设计存在主要缺陷为外力集中在芯片位置,容易产生死灯。

9、3.线路芯片固晶位焊盘正负极间距为0.15mm,而小尺寸芯片间距(gap)为0.13mm,会导致芯片电极与fpc焊盘接触面积小,使芯片电极面上锡少,产生芯片推力不足,导致产生空洞及虚焊问题,产生死灯不良。

10、发明人通过分析发现:

11、1.参阅图1和图2,导致生产固晶、拉胶、分板切割工站生产效率低,产生效率低具体原因:

12、①15条组合拼板在固晶站,固晶机治具盖板按15条设计,固定完每个单元(包含4小节15条基板)后进行拉料和进料动作,即会产生设备一定的非生产时间,相比较(4小节16条基板)降低了生产效率和产能;

13、②15条组合拼板在点胶站,点胶机的出胶针头按15个头配置,使15条基板连续性拉胶,相比较16条基板连续性拉胶降低了生产效率和产能;

14、③15条组合拼板在分板工站,刀模按15条设计进行分板相比较16拼产能和效率偏低;

15、④15条组合拼板在包装点亮测试站:探针是按15个设计,一次只能点亮15条,相比较16拼产能和效率偏低;

16、2.原有基板芯片的固晶焊盘连接于上下导线中间部位,由此会产生一定致命缺陷和隐患:

17、①芯片的固晶焊盘连接于上下导线中间部位,会产生致命缺陷:cob灯带在使用或安装过程中会产生外力,会导致基板产生一定的弯曲或弯折,导致芯片受外力产生电极脱落死灯;

18、②原有基板芯片的固晶焊盘上下导线较粗(0.22~0.25mm),cob灯带在弯曲过程中会先将外力传至正、负极主线上,再由主线将外力传至芯片的固晶焊盘上下导线上,导线越粗,外力传至越大,从而破坏芯片的力度也越大,使芯片电极脱落而产生死灯;

19、③参阅图3,原有基板线路,其导线较粗,固晶焊盘位置连接于上下导线中间部位。

20、3.原有基板芯片的固晶焊盘正负极间距为0.13~0.15mm,芯片gap间距为0.13mm,会产生一定致命缺陷和隐患:

21、①芯片推力不足:固晶焊盘正负极间距大于芯片gap间距时,会产生芯片电极与基板之间的接触面积变小,从而使芯片电极上锡面积缩小,降低了芯片推力值,容易产生死灯;

22、②芯片容易偏位:固晶焊盘正负极间距大于芯片gap间距时,因为芯片电极搭在基板上的面积缩小,导致点锡后芯片电极上锡少,在回流焊高温时锡膏处于瞬间沸腾状态,锡膏会拉动芯片往一端移动,从而会产生芯片偏位,导致芯片推力不足,容易产生死灯

23、③容易产生假焊:固晶焊盘正负极间距大于芯片gap间距时,不仅会产生芯片电极上锡少及芯片偏位,还会导致芯片推力不足,产生假焊而死灯;

24、④参阅图4,原有基板芯片的固晶焊盘正负极间距为0.13~0.15mm。

25、综合可知,存在上述技术问题。

26、生产效率低下问题:基板尺寸较大,分切和组合拼板过程导致生产效率下降,主要影响了固晶、拉胶、分板切割工站的产能和效率。

27、弯曲导致的死灯问题:基板上的芯片固晶焊盘连接于上下导线的中间部位,使得cob灯带在使用、安装或运输过程中容易发生弯曲,从而导致芯片电极脱落和死灯问题,这是一个严重的可靠性问题。

28、固晶焊盘间距和gap间距问题:芯片的固晶焊盘正负极间距大于芯片gap间距,导致了多个问题,包括芯片推力不足、芯片偏位、假焊等问题,最终也导致死灯的发生。

技术实现思路

1、为了解决现有cob灯带产生的外力使基板变形导致芯片脱落死灯的技术问题,本实用新型提供了一种cob灯带基板。

2、为达到上述目的,本实用新型的技术方案是这样实现的:

3、一种cob灯带基板,基板上设置有用于焊接芯片的焊盘,并设置有与芯焊电连接的导电线路,导线布置在焊盘顶部和底部。

4、通过将导线从芯片焊盘的顶部和底部进行布线,而不是直接横穿焊盘中心位,有效地分散了外力对于芯片的影响,有助于降低外力对芯片的集中作用,减少了芯片因外力而产生弯曲、位移或破坏的风险,提高了芯片的可靠性和寿命。

5、由于外力不再直接横穿焊盘中心位,芯片焊盘的布线设计有助于防止芯片的不必要位移或偏移,保持焊盘与芯片之间的稳定连接,减少了芯片因位移而导致的接触问题。

6、外力的分散释放和减少了对芯片的直接压力有助于提高基板和芯片的耐久性。这意味着cob灯带在长时间使用和不断受到外力影响的情况下,仍能保持稳定的性能。

7、进一步地,导线的宽度范围为0.16~0.18mm。

8、较细的导线可以更好地适应外部应力,包括振动和冲击,有助于维持芯片的机械稳定性,降低了断裂的风险;尽管导线宽度缩小,但不影响过电流和性能,这意味着芯片仍然可以正常工作,同时获得了更好的机械稳定性。

9、进一步地,焊盘正负极的间距为0.1~0.13mm。

10、较小的焊盘间距意味着芯片电极更紧密地连接到基板上,从而增强了芯片的推力,有助于确保芯片在各种条件下都能保持稳定的电连接,减少了死灯的风险;较小的间距使芯片更容易准确定位并固定在焊盘上,减少了在回流焊过程中芯片偏离焊盘的可能性,有助于确保芯片被精确地定位在其设计位置上,防止因偏位而导致的不良现象;较小的焊盘间距也有助于确保焊盘上锡均匀,减少了在回流焊过程中出现空洞或虚焊的问题,提高了焊接的可靠性,避免了假焊问题。

11、进一步地,基板的宽度为124mm,由16条组合拼板形成,单条基板宽度为7.75mm。

12、提升固晶、拉胶、分板切割生产效率及产能,由于新基板的宽度更宽,每次生产过程中可以同时处理更多的基板,这导致了固晶、拉胶、分板切割等生产工序的效率提高。

13、由于每个基板更窄,可以更好地适应生产线上的工序,提高了整体的产能。这意味着可以在相同的时间内生产更多的cob灯带基板。

14、与标准规格更匹配,有助于最大程度地优化原材料的利用率,减少了浪费。

15、通过提高生产效率和产能,以及优化材料利用率,可以降低生产过程中的制造成本。

16、实施本实用新型带来的有益效果是:

17、导线从芯片焊盘上面(顶部)和下面(底部)进行走线(即布线),而不是导线从芯片焊盘中心位直接横穿布线,避开了芯片上外力的有效释放和外力对芯片的破坏。另外,芯片的导线宽度由之有0.22~0.25mm缩小至0.16~0.18mm,在不影响过电流和性能情况下,还减少、减弱了外力对芯片本身的破坏;芯片的焊盘正负极间距由0.13~0.15mm优化更新为0.1~0.13mm间距,增强了芯片推力,避免了芯片偏位、假焊等不良现象,提升了产品稳定性。

18、通过上述措施,提高了成品良率,改善了原有基板成品死灯不良偏高的问题,提升了产品稳定性;基板线路的可靠性试验,如冷热冲击,高温老化,常温老化,高温高湿,扭力测试,摔打测试,缠绕测试等测试结果均比原有基板性能更好更加稳定。

本文地址:https://www.jishuxx.com/zhuanli/20240618/19985.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表