一种高密度多模态神经微电极阵列及其制备与集成方法

- 国知局

- 2024-07-27 12:37:53

1.本发明属于mems生物传感器技术领域,具体涉及一种用于神经信号检测的高密度多模态神经微电极阵列的制备与集成方法,该芯片是通过mems微加工和微组装技术在soi衬底上实现神经微电极阵列的制备与集成。背景技术:2.大脑的功能,如感知,运动控制,学习和记忆,产生于分布在多个大脑区域的神经元集体的协同激活过程。如今,在理解单个神经细胞的反应特性方面虽然已经取得了重大进展,但对复杂神经环路之间的相互作用机制仍然知之甚少。理解这些相互作用的一个基本障碍是很难同时测量行为动物大脑中大量分布神经元的活动。电生理记录一直是监测大脑的黄金标准,这是因为它直接测量神经元的电活动,具有极高的时间分辨率,使其足以捕捉到最快的神经元动作电位细节。目前,电生理记录神经微电极的主要瓶颈是小侵入性与大空间探测范围、高空间分辨率之间的矛盾。因此,通过新型的微纳加工技术实现高密度、小体积、阵列化的神经微电极制备,是脑机接口器件研究中需要解决的首要关键科学问题。3.霍华德休斯医学研究所的james j.jun等人在论文“fully integrated silicon probes for high‑density recording ofneural activity”中基于cmos多路复用开关电路,设计、制造和测试了一种名为“神经像素”的新型硅探针。每个探针有384个记录通道,可编程寻址960个tin记录电极点。通过将两个“神经像素”探针植入到小鼠的五个脑区中,他们同时记录到了超过700个独立神经元的动作电位信号。然而,采用以上方法制备的高密度神经微电极都不具备光刺激和流体给药功能,这使其功能性和长期植入的稳定性较差。为此,美国密西根大学的e.yoon教授在论文“monolithically integrated mu leds on silicon neural probes for high‑resolution optogenetic studies in behavinganimals”中将12个微led和32个记录电极点单片集成在4个硅基微探针上,同时实现了分辨率小于1微米的光刺激和电生理记录。e.yoon团队在论文“3d multi‑functional neural probe array for mapping functional connectivities in a 3d neuron chip”中进一步将16个记录通道、1个微流体通道以及1个光波导集成在4个硅探针上。该方法制备的多功能神经微电极能够同时实现光/电刺激、微流体给药以及神经电记录的功能。通过对上述关于神经微电极的研究现状进行分析不难发现,目前大部分的高密度密西根微电极(单根100通道以上)都没有集成光刺激通道和微流体通道,而集成了光刺激通道或微流体通道的密西根微电极的电极点密度往往偏低。这主要是因为目前大部分高密度密西根微电极的制备工艺与光波导或者微流体通道的制备工艺兼容性较差导致的。技术实现要素:4.本发明的目的在于针对现有技术中的缺陷,利用mems微加工技术实现具有电记录、光刺激和流体给药功能的新型高密度多模态神经微电极阵列的制备与集成。5.本发明提供的一种高密度多模态神经微电极阵列,包括高密度硅探针和微电极基部。高密度硅探针上分布有记录电极点、光波导出射端、微流体通道、顶层金属导线和底层金属导线。微流体通道共有多条;底层金属导线设置在微流体通道的底部。顶层金属导线设置在相邻的两条微流体通道之间。所述的顶层金属导线和底层金属导线通过单步工艺实现沉积,并通过微流体通道内凹的结构实现自动绝缘。微电极基部上设置有微流体通道入口、光波导耦合端和金属焊盘。各记录电极点与对应的金属焊盘通过顶层金属导线或底层金属导线连接。6.作为优选,微流体通道利用图形化的氧化硅作为硬掩模,在硅衬底上先后进行各向异性深硅刻蚀和各向同性深硅刻蚀得到的。微流体通道的出口位于高密度硅探针尖端的记录电极点处,并从高密度硅探针的尖端延伸到微电极基部的微流体通道入口。在微电极基部上,沿着远离高密度硅探针的方向,微流体通道的宽度逐渐变宽。7.作为优选,所述微流体通道的直径在1‑5微米;顶层金属导线和底层金属导线的宽度为2‑10微米;光波导的直径为5‑10微米;高密度硅探针的长度为5‑20毫米,宽度为100‑500微米,厚度为15‑100微米。单根高密度硅探针上记录电极点的数量为50‑200个,微流体通道的数量为49‑199个,光波导的数量为5‑20个。8.作为优选,微流体通道的内表面上利用pecvd上保形沉积有一层氧化硅,该层氧化硅在微流体通道的上开口密封后形成微流体通道与金属导线之间的绝缘层。9.作为优选,高密度硅探针上利用su‑8的光刻图形化技术形成光波导阵列结构,通过梯度折射率透镜与外部ld/led光源耦合实现光刺激。10.作为优选,所述的微电极基部上还设置有梯度折射率透镜、激光二极管和硅衬底。所述的梯度折射率透镜设置在硅衬底上。光波导耦合端与激光二极管通过梯度折射率透镜光耦合。11.作为优选,该高密度多模态神经微电极阵列还包括软管。所述的软管通过密封胶与微流体通道入口连通。12.作为优选,所述底层金属导线与金属焊盘的连接处存在台阶。该台阶处电镀有一层金纳米颗粒,实现台阶处的电学连接。13.作为优选,柔性排线与各金属焊盘通过各向异性导电胶实现电学和机械连接。14.该高密度多模态神经微电极阵列的制备过程如下:15.(1)利用图形化的氧化硅作为硬掩模,采用各向异性深硅刻蚀技术在soi硅片上形成矩形的沟道。16.(2)对深硅刻蚀的工艺参数进行调整,利用各向同性干法刻蚀技术形成管状沟道。17.(3)使用等离子体增强化学气相沉积系统在soi硅片上沉积一层氧化硅作为绝缘层。18.(4)利用电子束蒸发系统在氧化硅表面沉积一层cr/au作为导电层。由于电子束蒸发系统沉积的金属台阶覆盖特性较差,内凹沟道的存在使得cr/au自动图形化为线条结构,并能够彼此绝缘。随后,使用普通光刻和离子束刻蚀工艺将电极图形区域外的金属刻蚀掉。19.(5)使用pecvd在硅片上沉积一层厚氧化硅作为上绝缘层,通过绝缘层的保形沉积技术将沟道的上开口闭合,形成微流体通道。20.(6)使用光刻和反应离子刻蚀将电极点和焊盘上方的氧化硅清除,形成导电窗口。再次使用反应离子刻蚀和深硅刻蚀将微电极阵列正面轮廓线上的氧化硅和硅去除。然后,利用su‑8的光刻图形化技术在微电极阵列的探针上形成光波导阵列结构。最后,使用双面对准光刻和反应离子刻蚀以及深硅刻蚀将微电极阵列背面轮廓线上的氧化硅和硅去除实现释放。21.该高密度多模态神经微电极阵列的集成方法如下:22.(1)采用各向异性导电胶热压或超声焊线的方式将ld芯片键合到硅衬底上,实现固定和电气连接。23.(2)将梯度折射率透镜放入深硅刻蚀形成的沟槽内与光波导阵列结构耦合。24.(3)将键合好的ld芯片与微电极阵列放置在一个pcb电路板上进行对准后固定,实现ld与光波导的耦合。25.(4)采用acf来实现微电极阵列与柔性排线在平面内的热压键合。26.(5)将软管通过密封胶水固定到高密度硅探针与微电极基部的连接处。微电极基部(2)上逐渐发散的微流体通道的开口变大,无法在保形沉积过程中实现闭合而保留开口;该开口与软管连通,实现微流体的注入功能。27.作为优选,所述集成方法的步骤(4)中,利用微加工工艺在焊盘处形成凸起。通过在焊盘上贴附一层acf导电胶,并将柔性排线的焊盘与微电极的焊盘对齐后施加预设的温度和压力,实现焊盘在法向的导通。28.本发明具有的有益效果是:29.1、本发明结合各向异性深硅刻蚀和各向同性深硅刻蚀技术在导线之间实现微流体通道的制备,通过微流体给药实现对胶质反应的抑制,从而提高神经微电极阵列记录和刺激的长期稳定性。30.2、本发明利用深硅刻蚀技术在记录导线之间刻蚀出内凹的沟道,通过在沟道内部进行“零线间距”布线将记录通道的数量提高一倍,即在单根探针上集成50‑200个记录通道,为目前主流多模态探针的十倍以上。此外,本发明利用pecvd在沟道内表面保形沉积一定厚度的氧化硅,将沟道的上开口密封后可以形成微流体通道和金属导线之间的绝缘层,这样就可以同时实现微流体通道的多功能集成以及记录通道密度的提高。31.3、本发明使用梯度折射率透镜实现ld与光波导之间的光耦合,通过降低ld与光波导之间的耦合损失,从而提高光刺激的可靠性,并实现了微光波导的多功能集成。附图说明32.图1为本发明中高密度多模态神经微电极阵列的整体结构示意图;33.图2为本发明中高密度神经微电极阵列的制备工艺流程图;34.图3为本发明中高密度多模态神经微电极阵列的集成示意图。具体实施方式35.以下结合附图对本发明作进一步说明。36.如图1所示,一种高密度多模态神经微电极阵列,包括高密度硅探针1和微电极基部2。高密度硅探针1的表面分布有多个记录电极点1‑1、光波导出射端1‑2、微流体通道1‑3、顶层金属导线1‑4和底层金属导线1‑5。并排设置的多条微流体通道1‑3为管状沟槽。各微流体通道1‑3的底部均设置有底层金属导线1‑5。任意两个相邻的微流体通道1‑3之间均设置有顶层金属导线1‑4。微流体通道1‑3能够进行微流体给药;同时,微流体通道1‑3将底层金属导线1‑5与顶层金属导线1‑4隔开。从而实现“零线间距”布线,在不改变线宽的情况下将布线密度提高一倍。37.微电极基部2上设置有微流体通道入口2‑1、光波导耦合端2‑2、金属焊盘2‑3、梯度折射率透镜2‑5、激光二极管2‑6和硅衬底2‑7。多个记录电极点1‑1与多个金属焊盘2‑3一一对应。高密度硅探针1上设置有多条光波导。各光波导将光波导出射端1‑2与光波导耦合端2‑2连接。各记录电极点1‑1通过对应的一条顶层金属导线1‑4或底层金属导线1‑5与对应的金属焊盘2‑3电连接。各微流体通道1‑3从高密度硅探针1延伸至微电极基部2上。并且,在微电极基部2上,沿着远离高密度硅探针1的方向,微流体通道的宽度逐渐变宽,这导致其上部的开口无法被氧化硅密封,因此可以直接与微流体通道入口相连接。38.如图3所示,由于顶层金属导线1‑4和底层金属导线1‑5不在一个平面,这导致底层金属导线1‑5与对应的金属焊盘2‑3之间存在台阶。为了避免台阶处的金属断路,采用电镀的方法在台阶处形成一层厚的金纳米颗粒2‑4,从而实现台阶处的电学连接。光波导耦合端2‑2通过梯度折射率透镜2‑5与激光二极管2‑6实现光耦合。光波导耦合端2‑2所在硅衬底2‑7与激光二极管2‑6所在pcb位于同一个对准平台3上。软管4通过密封胶与微流体通道入口2‑1连通,实现流体注入。柔性排线6通过各向异性导电胶5与各金属焊盘2‑3实现电学和机械连接。39.实施例140.如图2所示,一种高密度多模态神经微电极阵列的具体制备步骤如下:41.(1)首先,如图2中的a和a'部分所示,使用pecvd系统在soi衬底上沉积1微米厚的氧化硅,并利用光刻和反应离子刻蚀(rie)技术将氧化硅图形化为2微米线宽和2微米线间距的线条。利用图形化的氧化硅作为硬掩模,采用各向异性深硅刻蚀技术在soi硅片的顶层硅上形成并排设置的多条宽度和间距均为2微米的矩形沟道。42.(2)接着,如图2中的b和b'部分所示,对深硅刻蚀的工艺参数进行调整,利用各项同性深硅刻蚀技术将矩形沟道刻蚀为直径为2‑3微米的管状沟道(截面为优圆弧)。43.(3)然后,如图2中的c和c'部分所示,使用等离子体增强化学气相沉积系统(pecvd)在soi衬底上沉积一层200纳米厚度的氧化硅,作为金属导线的绝缘层。44.(4)接着,如图2中的d和d'部分所示,利用电子束蒸发系统在绝缘层的表面沉积一层cr/au(20/200nm)作为导电层。由于电子束蒸发系统沉积的金属台阶覆盖特性较差,内凹的管状沟道的存在使得cr/au自动图形化为线条结构,并能够彼此绝缘。随后,使用普通光刻和离子束刻蚀工艺将电极图形区域外的金属刻蚀掉。45.(5)然后,如图2中的e和e'部分所示,使用pecvd在硅片上沉积一层1微米厚的氧化硅作为上绝缘层,通过绝缘层的保形沉积技术将管状沟道的上开口闭合,从而实现微流体通道的制备。46.(6)接着,如图2中的f和f'部分所示,使用光刻和反应离子刻蚀将电极点和焊盘位置上方的氧化硅清除,形成导电窗口。再次使用反应离子刻蚀和深硅刻蚀将微电极正面轮廓线上的氧化硅和硅去除。然后,利用su‑8的光刻图形化技术在微电极的探针上形成光波导阵列结构。最后,使用双面对准光刻和反应离子刻蚀以及深硅刻蚀将微电极背面轮廓线上的氧化硅和硅去除,实现释放。47.如图3所示,一种高密度多模态神经微电极阵列的具体集成步骤如下:48.(1)采用各向异性导电胶(acf)热压和超声焊线的方式将一个ld芯片键合到soi衬底上实现固定和电气连接。49.(2)接着,将一个梯度折射率透镜放入深硅刻蚀形成的沟槽内与su‑8光波导阵列结构耦合。50.(3)随后,将键合好的ld芯片与微电极放置在一个pcb电路板上进行对准后固定,从而实现ld与光波导的高效耦合。51.(4)完成光电集成后,采用acf来实现微电极与柔性排线在平面内的热压键合。为提高键合成功率,需要利用微加工工艺在微电极的焊盘处形成一个凸起。通过在焊盘上贴附一层acf导电胶,并将柔性排线的焊盘与微电极的焊盘对齐后施加一定的温度和压力可以实现焊盘在法向的导通。52.(5)为实现微流体给药功能,将一个聚合物软管通过密封胶水固定到探针与基部的连接处。由于该处的管状沟道从密排逐渐发散开,这会导致基部区域的沟道开口变大,从而无法在保形沉积过程中实现闭合。因此,将软管的一端与该处的开口连通即可实现微流体的注入功能。53.实施例254.一种高密度多模态神经微电极阵列的具体制备步骤如下:55.(1)首先,使用pecvd系统在soi衬底上沉积1微米厚的氮化硅,并利用光刻和反应离子刻蚀(rie)技术将氧化硅图形化为线宽和间距均为2微米的多条线条。利用图形化的氮化硅作为硬掩模,采用各向异性深硅刻蚀技术在soi硅片的顶层硅上形成宽度为2微米的矩形沟道。56.(2)接着,对深硅刻蚀的工艺参数进行调整,利用各项同性深硅刻蚀技术将矩形的沟道刻蚀为直径为2‑3微米的管状沟道。57.(3)然后,使用等离子体增强化学气相沉积系统(pecvd)在硅片上沉积一层200纳米厚度的氮化硅作为金属导线的绝缘层。58.(4)接着,利用电子束蒸发系统在氧化硅表面沉积一层cr/au(20/200nm)作为导电层。由于电子束蒸发系统沉积的金属台阶覆盖特性较差,内凹沟道的存在使得cr/au自动图形化为线条结构,并能够彼此绝缘。随后,使用普通光刻和离子束刻蚀工艺将电极图形区域外的金属刻蚀掉。59.(5)然后,使用pecvd在硅片上沉积一层1微米厚的氧化硅作为上绝缘层,通过绝缘层的保形沉积技术将沟道的上开口闭合,从而实现微流体通道的制备。60.(6)接着,使用pecvd在氧化硅上先后沉积一层4微米厚的氮化硅和1微米厚的氧化硅分别作为光波导的芯层和包层。接着,使用光刻和反应离子刻蚀将芯层和包层图形化为光波导结构。然后,再次利用光刻和反应离子刻蚀将电极点和焊盘上方的绝缘层清除。最后,使用双面对准光刻、反应离子刻蚀以及深硅刻蚀将微电极背面轮廓线上的氧化硅和硅去除实现微电极的释放。61.一种高密度多模态神经微电极阵列的具体集成步骤如下:62.(1)拟采用贴片机将一个ld芯片键合到硅衬底上实现固定和电气连接。63.(2)接着,将一个梯度折射率透镜放入深硅刻蚀形成的沟槽内与氧化硅/氮化硅/氧化硅光波导耦合。64.(3)随后,将键合好的ld与微电极放置在一个pcb电路板上进行对准后固定,从而实现ld与光波导的高效耦合。65.(4)完成光电集成后,拟采用acf来实现微电极与柔性排线在平面内的热压键合。为提高键合成功率,需要利用微加工工艺在微电极的焊盘处形成一个凸起。通过在焊盘上贴附一层acf导电胶,并将软排线的焊盘与微电极的焊盘对齐后施加一定的温度和压力可以实现焊盘在法向的导通。66.(5)为实现微流体给药功能,拟将一个聚合物软管通过密封胶水固定到探针与基部的连接处。由于该处的沟道从密排逐渐发散开,这会导致基部区域的沟道开口变大,从而无法在保形沉积过程中实现闭合。因此,将软管的一端与该处的开口连通即可实现微流体的注入功能。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122808.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

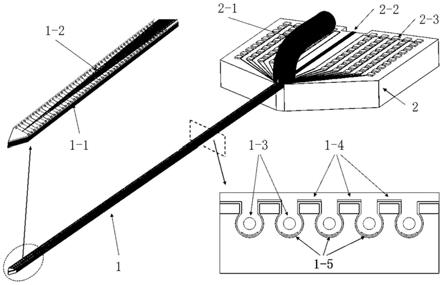

返回列表