一种机载电子时钟测试设备的制作方法

- 国知局

- 2024-07-30 09:41:08

1.本实用新型涉及一种机上测试系统,具体是一种机载电子时钟测试设备。背景技术:2.机载电子时钟是安装在飞机驾驶舱内,用于给飞行员提供utc时间,并通过arinc429 通信向机载系统提供utc时间,由于原厂技术封锁,对项目的技术参数需要测定,需要分析项目的工作原理,自行制造实验设备,对其进行参数的测定具有部件维修周期长、测试繁琐等问题,而这些问题导致了航空公司飞机的延误、服务质量的下降,直接影响到航空公司的经济效益。技术实现要素:3.本实用新型的目的在于提供一种机载电子时钟测试设备,以解决上述背景技术中提出的问题。4.为实现上述目的,本实用新型提供如下技术方案:5.一种机载电子时钟测试设备,包括待测电子时钟,所述待测电子时钟连接电源模块,所述待测电子时钟通过数据通讯模块连接数据采集模块和控制模块,所述数据采集模块连接电脑终端。6.作为本实用新型进一步的方案:所述电源模块采用直流电源,所述直流电源的型号采用的是dh1718e-5。7.作为本实用新型再进一步的方案:所述电源模块包括变压器tr1,所述变压器tr1连接交流电220v和接地端,所述变压器tr1的输出1端连接二极管d28和二极管d26,所述二极管d26的另一端连接二极管d29、电容c25、电容c27、芯片u7的1端和芯片u10的 1端,所述二极管d29的另一端连接二极管d27和变压器tr1的3输出端,所述二极管d27 的另一端连接二极管d28的另一端,所述电容c25的另一端连接电容c26、电容c27的另一端、电容c28、芯片u7的2引脚、芯片u8的1引脚、芯片u10的2引脚、电容c29、电容c30、电容c33、电容c34、二极管d32、电容c31、电容c32、二极管d30、二极管d31、所述变压器的2输出端和接地端,所述芯片u7的3引脚连接电容c29的另一端、电容c31的另一端、二极管d30的另一端和12v直流电源端输出端,所述芯片u10的3引脚连接电容c33的另一端、电容c34的另一端、二极管d32的另一端和5v直流电源端输出端,所述二极管d28的另一端连接芯片u8的2引脚、电容c26的另一端和电容c28的另一端,所述芯片u8的3引脚连接电容c30的另一端、电容c32的另一端、二极管d31的另一端和-12v直流电源端输出。8.作为本实用新型再进一步的方案:所述通讯模块包括芯片u2,所述芯片u2的1引脚和3引脚连接电容c1,所述芯片u2的4引脚和5引脚连接电容c2,所述芯片u2的10引脚连接输出模块output的3引脚和二极管rxd,所述二极管rxd的另一端连接电阻r3,所述芯片u2的9引脚连接输出模块output的2引脚和二极管txd,所述二极管txd的另一端连接电阻r2,所述电阻r2和电阻r3的另一端连接电源vcc端,所述芯片u2的16引脚连接电容c3、电容c5、电容c6、电阻r1、电源vcc端和芯片j13,所述电容c3的另一端连接芯片u2的2引脚,所述电容c5的另一端接地,所述电容c6的另一端接地,所述电阻r1的另一端连接二极管pwr,所述二极管pwr的另一端接地,所述芯片j13的2引脚和3引脚接地,所述芯片u2的6引脚连接电容c4,所述电容c4的另一端连接芯片u2的 15引脚和接地端,所述芯片u2的7引脚连接模块j8的2引脚,所述芯片u2的8引脚连接模块j8的3引脚,所述模块j8的5引脚接地。9.作为本实用新型再进一步的方案:所述控制模块包括三极管q1、三极管q2、三极管 q3、三极管q4、三极管q5、三极管q6、开关k1和开关k3,所述三极管q1的集电极连接二极管d1和继电器1,所述二极管d1的另一端连接继电器1的另一端、28v输出引脚、继电器2、二极管d2、继电器3、二极管d4、开关k2、二极管d3和继电器4,所述继电器2的另一端连接二极管d2的另一端和三极管q2的集电极,所述三极管q2的基极连接电阻r2,所述电阻r2的另一端连接电阻r1和s1输出引脚,所述电阻r1的另一端连接三极管q1的基极,所述三极管q1的发射极接地,所述三极管q2的发射极接地,所述二极管d4的另一端连接继电器3的另一端和三极管q4的集电极,所述三极管q4的发射极接地,所述三极管q4的基极连接电阻r4,所述电阻r4的另一端连接s4输出引脚,所述开关k2的另一端连接开关k4和y输出引脚,所述开关k4的另一端连接v输出引脚,所述二极管d3的另一端连接继电器4和三极管q6的集电极,所述三极管q6的发射极接地,所述三极管q6的基极连接电阻r6,所述电阻r6的另一端连接s2输出引脚,所述开关k1 的一端连接5v直流引脚,所述开关k1的另一端连接k引脚和l引脚,所述三极管q3的基极连接电阻r3,所述电阻r3的另一端连接s5引脚,所述三极管q1的发射极接地,所述三极管q3的集电极连接p引脚,所述开关k3连接a引脚和c引脚。10.作为本实用新型再进一步的方案:所述数据采集模块包括芯片u6、芯片u7、芯片u8、芯片u5和芯片u4,所述芯片u6采用的型号是ncu123lxxanx,所述芯片u4的型号是 lt16147,所述芯片u5的型号是mc14043bd,所述芯片u8的型号是adm3251e,所述芯片 u7的型号是max232acse。11.与现有技术相比,本实用新型的有益效果是:本技术通过采用通讯模块实现上位机和信号数据的相互通讯,本技术通过采用控制模块和数据采集模块实现利用上位机发送控制信号到达控制模块实现信号的控制,能够对部件进行维修,减短维修的时间和维修的费用,保证航空公司的经济效益。附图说明12.图1为机载电子时钟测试设备的测试系统示意图。13.图2为机载电子时钟测试设备中设备的示意图。14.图3为机载电子时钟测试设备中控制面板示意图。15.图4为机载电子时钟测试设备中电源模块电路图。16.图5为机载电子时钟测试设备中通讯模块电路图。17.图6为机载电子时钟测试设备中控制模块电路图。18.图7为机载电子时钟测试设备中数据采集模块电路图。19.图8为机载电子时钟测试设备中输出电源模块电路图。20.图9为机载电子时钟测试设备中数据输入模块电路图。21.图10为机载电子时钟测试设备中数据输出模块一电路图。转ttl模块来完成,由原来的rs232±15v电平转换为上位机ttl5v电平,上位机与rs232 信号数据的相互通讯;34.所述通讯模块包括芯片u2,所述芯片u2的1引脚和3引脚连接电容c1,所述芯片u2 的4引脚和5引脚连接电容c2,所述芯片u2的10引脚连接输出模块output的3引脚和二极管rxd,所述二极管rxd的另一端连接电阻r3,所述芯片u2的9引脚连接输出模块 output的2引脚和二极管txd,所述二极管txd的另一端连接电阻r2,所述电阻r2和电阻r3的另一端连接电源vcc端,所述芯片u2的16引脚连接电容c3、电容c5、电容c6、电阻r1、电源vcc端和芯片j13,所述电容c3的另一端连接芯片u2的2引脚,所述电容 c5的另一端接地,所述电容c6的另一端接地,所述电阻r1的另一端连接二极管pwr,所述二极管pwr的另一端接地,所述芯片j13的2引脚和3引脚接地,所述芯片u2的6引脚连接电容c4,所述电容c4的另一端连接芯片u2的15引脚和接地端,所述芯片u2的7 引脚连接模块j8的2引脚,所述芯片u2的8引脚连接模块j8的3引脚,所述模块j8的 5引脚接地。35.作为本技术的进一步实施例,请参阅图1、图2、图3和图6,通过atmega16微控制器的数字信号接口通过继电器充分控制离散电源信号的接通与断开。如s1链路控制,当 s1信号为高电平时,使q1输出低电平,k1导通,从而使k,l接通5vac.当s1为低电平时, q1无电平输出,k1断开,从而使k,l断开5vac。其余链路控制功能类似;36.所述控制模块包括三极管q1、三极管q2、三极管q3、三极管q4、三极管q5、三极管 q6、开关k1和开关k3,所述三极管q1的集电极连接二极管d1和继电器1,所述二极管 d1的另一端连接继电器1的另一端、28v输出引脚、继电器2、二极管d2、继电器3、二极管d4、开关k2、二极管d3和继电器4,所述继电器2的另一端连接二极管d2的另一端和三极管q2的集电极,所述三极管q2的基极连接电阻r2,所述电阻r2的另一端连接电阻r1和s1输出引脚,所述电阻r1的另一端连接三极管q1的基极,所述三极管q1的发射极接地,所述三极管q2的发射极接地,所述二极管d4的另一端连接继电器3的另一端和三极管q4的集电极,所述三极管q4的发射极接地,所述三极管q4的基极连接电阻r4,所述电阻r4的另一端连接s4输出引脚,所述开关k2的另一端连接开关k4和y输出引脚,所述开关k4的另一端连接v输出引脚,所述二极管d3的另一端连接继电器4和三极管q6 的集电极,所述三极管q6的发射极接地,所述三极管q6的基极连接电阻r6,所述电阻 r6的另一端连接s2输出引脚,所述开关k1的一端连接5v直流引脚,所述开关k1的另一端连接k引脚和l引脚,所述三极管q3的基极连接电阻r3,所述电阻r3的另一端连接 s5引脚,所述三极管q1的发射极接地,所述三极管q3的集电极连接p引脚,所述开关 k3连接a引脚和c引脚。37.作为本技术的进一步实施例,请参阅图1、图2和图7,所述数据采集模块包括芯片 u6、芯片u7、芯片u8、芯片u5和芯片u4,所述芯片u6采用的型号是ncu123lxxanx,所述芯片u4的型号是lt16147,所述芯片u5的型号是mc14043bd,所述芯片u8的型号是 adm3251e,所述芯片u7的型号是max232acse。38.作为本技术的进一步实施例,请参阅图1、图2、图7和图8,所述数据采集模块包括数据收发器,其中数据收发器包括输出电源模块、数据输入模块、数据输出模块、数据处理模块和232连接模块,所述单片机模块包括8个移位寄存器74hc595;39.p1连接器是输入和输出信号的端口,此模块分别提供了两组输入ch1/2(in)和两组输出ch1/2(out)通道。u1芯片为四通道电压比较芯片,将输入的ch1/2(in)的信号从模拟信号转换成二进制的数字信号,其中一路接入u3芯片,u3芯片为双通道或门芯片,将两路数字信号进行或运算,从而得到每个通道的时钟信号。另一路接入u5芯片,u5芯片为四通道的rs锁存器,其根据r,s脚的输入信号得到一组新的二进制代码,这个就是转化后的各通道输入的二进制数据。此二进制数据输入u6(32位微处理器),配合烧录进u6芯片中的软件算法,u8(rs232收发器)芯片和u7(rs232转换)芯片,将输入二进制数据转换成rs232数据输出,配合上位机程序翻译成32位的arinc429数据。反之,上位机程序发送rs232数据,由u8,u7,u6芯片将其转换成二进制数据,传输给u2放大器,q1-q4 构成推挽电路将模拟信号输出ch1/2(out),d6,d7为双向钳位保护二极管。此外u4为电源芯片,主要功能是将电源模块提供的5vdc电压转换成±12vdc电压,供给通讯模块各芯片使用。40.所述输出电源模块包括芯片u4和封装模块p3,主要为429收发器产生±12v电源,输入5v电源后通过lt1617变压为±12v电源,即所述芯片u4的4引脚连接5v电源端、电容c7、芯片u4的5引脚和电感l1,所述电容c7的另一端连接接地端、芯片u4的2引脚、二极管d5、电阻r20和电容c9,所述电感l1的另一端连接电容c2、电容c4和芯片 u4的1引脚,所述电容c2的另一端连接二极管d2和二极管d1,所述二极管d2的另一端连接电容c1和接地端,所述二极管d1的另一端连接电容c1的另一端和二极管d20,所述二极管d20的另一端连接12v输出端,所述电容c4的另一端连接二极管d5的另一端和二极管d3,所述二极管d3的另一端连接电阻r11、电容c5、电容c9的另一端和二极管d21,所述二极管d21的另一端连接-12v输出端,所述电阻r11的另一端连接芯片u4的3引脚、电阻r20的另一端和电容c5的另一端,所述模块p3封装上述电源模块部件,所述模块p3 的4引脚接地,所述模块p3的3引脚连接外接5v电源,所述模块p3的2引脚输出-12v,所述模块p3的1引脚输出12v。41.请参阅图1、图2、图7和图9,收发器数据输入模块芯片u1是四通道比较器芯片,其可以将输入的ch1/2(in)的信号从模拟信号转换成数字信号(二进制),然后其中一路信号输入芯片u3,u3芯片为双通道或门芯片,其功能是将两路输入信号进行或运算,进而得到此通道的时钟信号。另一路信号接入芯片u5,u5芯片是四通道rs锁存器,其功能是根据r,s脚的输入信号转换得到一组二进制数字代码,这个二进制代码就是转化后的各个通道输入的二进制数据。数据输入模块包括芯片u5,所述芯片u5的2引脚连接电阻r28,所述电阻r28的另一端连接信号端ch1 data,所述芯片u5的9引脚连接电阻r30,所述电阻r30的另一端连接信号端ch2 data,所述芯片u5的16引脚连接5v电源端,所述芯片u5的8引脚接地,所述芯片u5的5引脚连接电阻r24,所述电阻r24的另一端连接5v 电源端,所述芯片u5的3引脚连接或非门u3a的2引脚、二极管d4、电阻r18、电阻r23 和电阻r29,所述二极管d4包括对称设置的两个二极管且所述两个二极管的中间接地,所述二极管d4的另一端连接或非门u3a的1引脚、芯片u4的4引脚、电阻r1、电阻r5和电阻r14,所述或非门u3a的7引脚连接电阻r15,所述电阻r15的另一端连接电容c8和信号ch1_cloc1,所述电阻r29的另一端连接集成运算放大器u1b的7引脚和电阻r26,所述集成运算放大器u1b的1引脚连接电阻r23的另一端,所述集成运算放大器u1b的12 引脚连接-12v电源端,所述集成运算放大器u1b的3引脚连接12v电源端,所述集成运算放大器u1b的的6引脚连接电阻r22和电阻r27,所述电阻r26的另一端连接电阻r25、电阻r21、电容c6和电阻r7,所述电阻r25的另一端连接ch1 in b端,所述电阻r21的另一端连接接地端和电阻r6,所述电阻r6的另一端连接电阻r3、电阻r22的另一端、电容c6的另一端和电阻r4,所述电阻r3的另一端连接ch1 in a端,所述电阻r14的另一端连接电阻r18的另一端、5v电源端、电阻r17的另一端和电阻r13,所述电阻r13的另一端连接电阻r7的另一端、集成运算放大器u1a的4引脚,所述集成运算放大器u1a的5 引脚连接电阻r4的另一端和电阻r1的另一端,所述集成运算放大器u1a的12引脚连接-12v电源端,所述集成运算放大器u1a的3引脚连接12v电源端,所述集成运算放大器 u1a的2引脚连接电阻r5的另一端;42.芯片u5的7引脚连接或非门u3b的6引脚、电阻r50、电阻r55、电阻r47和二极管 d8,所述二极管d8包括两个对称设置的二极管,所述两个对称设置的二极管连接端接地,所述芯片u5的6引脚连接或非门u3b的5引脚、二极管d8的另一端、电阻r39、电阻r34 和电阻r44,所述r44的另一端连接电阻r47的另一端、5v电源端、电阻r43和电阻r46,所述或非门u3b的3引脚连接电阻r45,所述电阻r45的另一端连接电容c14和ch2_clock,所述电容c14的另一端接地,所述电阻r55的另一端连接集成运算放大器u1d的11引脚和电阻r52,所述集成运算放大器u1d的12引脚连接-12v,所述集成运算放大器u1d的3 引脚连接12v,所述集成运算放大器u1d的13引脚连接电阻r50的另一端,所述集成运算放大器u1d的10引脚连接电阻r49和电阻r46的另一端,所述电阻r52的另一端连接电阻r41、电容c13、电阻r48和电阻r51,所述电阻r51的另一端连接ch2 in b,所述电阻r48的另一端连接接地端和电阻r40,所述电阻r40的另一端连接电阻r37、电阻r38、电容c13的另一端和电阻r49的另一端,所述电阻r37的另一端了解ch2 in a,所述带之怒r38的另一端连接电阻r34的另一端和集成运算放大器u1c的9引脚,所述集成运算放大器u1c的12引脚连接-12v,所述集成运算放大器u1c的3引脚连接12v,所述集成运算放大器u1c的14引脚连接电阻r39的另一端,所述集成运算放大器u1c的8引脚连接电阻r41的另一端和电阻r43的另一端。43.请参阅图1、图2、图7、图10和图11,收发器数据输出模块是向下位机发送串口232 数据,将由u8,u7,u6芯片将串口数据转换成二进制数据,再传输给u2放大器,并由q1-q4 构成的推挽电路将模拟信号输出ch1/2(out),电路中的d6,d7为双向钳位保护二极管,所述数据输出模块包括集成运算放大器u2a、集成运算放大器u2b、集成运算放大器u2c和集成运算放大器u2d,44.所述集成运算放大器u2a的3引脚连接电阻r8、电容c3和电阻r10,所述电阻r8的另一端和所述电容c3的另一端接地,所述电阻r10的另一端连接chia端和电阻r31,所述集成运算放大器u2a的2引脚连接电阻r16、电阻r19和电容c10,所述电阻r16的另一端连接chib端和电阻r33,所述集成运算放大器u2a的11引脚连接-12v,所述集成运算放大器u2a的4引脚连接12v,所述集成运算放大器u2a的1引脚连接电阻r12,所述电阻r12的另一端连接三极管q1,所述三极管q1包括npn三极管和pnp三极管,所述npn 三极管的发射极和pnp三极管的发射极连接,所述所述电阻r12的另一端连接npn三极管的基极和pnp三极管的基极,所述npn三极管的集电极连接电阻r2和三极管q2,所述电阻r2的另一端连接12v,所述pnp三极管的集电极连接三极管q2和电阻r42,所述电阻 r42另一端连接-12v,所述npn三极管的发射极和pnp三极管的发射极连接在电阻r19的另一端、电容c10的另一端、二极管d12和电阻r9,所述二极管d12的另一端连接二极管 d13,所述二极管d13的另一端接地,所述电阻r9的另一端连接二极管d6和ch1 out a 端,所述二极管d6的另一端接地;45.所述集成运算放大器u2b的6引脚连接电阻r31的另一端、电容c11和电阻r27,所述集成运算放大器u2b的5引脚连接电阻r33的另一端、电容c12和电阻r36,所述电阻 r36的另一端和电容c12的另一端接地,所述集成运算放大器u2b的4引脚连接12v,所述集成运算放大器u2b的11引脚连接-12v,所述集成运算放大器u2b的7引脚连接电阻 r32,所述电阻r32的另一端连接三极管q2,所述三极管q2包括npn三极管和pnp三极管,所述npn三极管的发射极和pnp三极管的发射极连接,所述npn三极管的基极和pnp三极管的基极连接电阻r32的另一端,所述npn三极管的集电极连接三极管q1的npn三极管的集电极,所述pnp三极管的集电极连接三极管q1的pnp三极管的集电极,所述三极管 q2的npn三极管的发射极和pnp三极管的发射极连接电容c11的另一端、电阻r27的另一端、二极管d14和电阻r35,所述二极管d14的另一端连接二极管d15,所述二极管d15 的另一端接地,所述电阻r35的另一端连接二极管d7和ch1 out b端,所述二极管d7的另一端接地;46.所述集成运算放大器u2c的10引脚连接电阻r57、电容c15和电阻r59,所述电阻r57 的另一端和电容c15的另一端接地,所述电阻r59的另一端连接ch2a端和电阻r68,所述集成运算放大器u2c的9引脚连接电阻r62、电阻r65和电容c16,所述电阻r62的另一端连接电阻r71,所述集成运算放大器u2c的11引脚连接-12v,所述集成运算放大器u2c 的4引脚连接12v,所述集成运算发达器u2c的8引脚连接电阻r60,所述电阻r60的另一端连接三极管q3,所述三极管q3包括npn三极管和pnp三极管,所述npn三极管的发射极和pnp三极管的发射极连接,所述电阻r60的另一端连接npn三极管的基极和pnp三极管的基极,所述npn三极管的发射极连接电阻r53和三极管q4,所述电阻r53的另一端连接12v,所述pnp三极管的集电极连接电阻r76和三极管q4,所述电阻r76的另一端连接-12v,所述npn三极管的发射极和pnp三极管的发射极连接电阻r65的另一端、电容c16 的另一端、二极管d16的另一端和电阻r58,所述二极管d16的另一端连接二极管d17,所述二极管d17的另一端接地,所述电阻r58的另一端连接ch2 out a端和二极管d10,所述二极管d10的另一端接地;47.所述集成运算放大器u2d的13引脚连接电阻r68的另一端、电容c17和电阻r67,所述集成运算放大器u2d的12引脚连接电阻r71的另一端、电容c19和电阻r73,所述电阻 r73和电容c19的另一端接地,所述集成运算放大器u2d的4引脚连接12v,所述集成运算放大器u2d的11引脚连接-12v,所述集成运算放大器u2d的14引脚连接电阻r69,所述电阻r69的另一端连接三极管q4,所述三极管q4包括npn三极管和pnp三极管,所述 npn三极管的发射极和pnp三极管的发射极连接,所述电阻r69的另一端连接npn三极管的基极和pnp三极管的基极,所述三极管q4的pnp三极管集电极连接三极管q3的pnp集电极和电阻r76,所述三极管q4的npn三极管集电极连接三极管q3的npn三极管集电极,所述三极管q4的npn三极管的发射极和pnp三极管的发射极连接电容c17的另一端、电阻r67、二极管d18和电阻r72,所述二极管d18的另一端连接二极管d19,所述二极管 d19的另一端接地,所述电阻r72的另一端连接ch2 out b和二极管d11,所述二极管d11 的另一端接地。48.请参阅图1、图2、图7和图11,收发器数据数据处理模块是二进制数输入u6(微处理器),然后配合u6芯片预烧录的软件算法,再经过u8(串口232收发)芯片和u7(串口232转换)芯片,将输入的二进制数据最后转换成rs232数据输出,输出的串口数据由上位机程序翻译成arinc429数据。所述数据处理模块包括芯片u6,所述芯片u6的28引脚连接电阻r63,所述芯片u6的25引脚连接电阻r61,所述电阻r63的另一端和电阻r61 的另一端连接ch2b端,所述芯片u6的20引脚连接电阻r70,所述芯片u6的17引脚连接电阻r74,所述电阻r70的另一端和电阻r74的另一端连接ch1b端,所述芯片u6的14引脚连接电容c22,所述电容c22的另一端连接芯片u6的12引脚、电容c23和接地端,所述电容c23的另一端连接芯片u6的10引脚,所述芯片u6的11引脚和所述芯片u6的13 引脚连接5v电源端,所述芯片u6的3引脚输出为ch1_clock端,所述芯片u6的4引脚输出为ch1_data端,所述芯片u6的6引脚输出为rs232_rx端,所述芯片u6的7引脚输出为rs232_tx端,所述芯片u6的46引脚连接电容c21、电阻r75和reset端,所述电容 c21的另一端接地,所述电阻r75的另一端连接5v电源端,所述芯片u6的45引脚连接晶振y1和电容c20,所述电容c20的另一端连接接地端、电容c18,所述电容c18的另一端连接晶振y1的另一端和芯片u6的44引脚,所述芯片u6的41引脚为ch2 data端,所述芯片u6的38引脚为ch2 clock端,所述芯片u6的37引脚连接5v电源端,所述芯片u6 的36引脚连接电阻r56和模块p2的3引脚,所述模块p2的1引脚连接二极管d9,所述二极管d9的另一端连接5v电源端,所述电阻r56的另一端连接5v电源端,所述模块p2 的2引脚连接电阻r54和芯片u6的35引脚,所述模块p2的4引脚为reset端,所述模块p2的5引脚接地,模块j1的1引脚连接二极管d22和模块p6的1引脚,所述二极管 d22的另一端连接5v电源端,所述模块j1的2引脚连接电阻r64,所述电阻r64的另一端连接模块p6的2引脚,所述模块j1的3引脚连接电阻r66,所述电阻r66的另一端连接模块p6的3引脚,所述模块j1的5引脚连接接地端和模块j6的5引脚。49.请参阅图1、图2、图7和图13,收发器232连接模块连接到电脑串口经过u8(串口 232收发)芯片和u7(串口232转换)芯片,将输入的二进制数据最后转换成rs232数据输出,输出的串口数据由上位机程序翻译成arinc429数据。所述232连接模块包括芯片 u8和芯片u7,所述芯片u8的2引脚连接芯片u8的3引脚、电源5v端和电容c29,所述电容c29的另一端连接接地端、rs232_rx端、rs232_tx端、芯片u8的10引脚、芯片u8 的4引脚、芯片u8的5引脚、芯片u8的6引脚和芯片u8的7引脚,所述芯片u8的20 引脚连接电容c30和电容c31,所述电容c30的另一端连接gndiso端,所述电容c31的另一端连接芯片u8的19引脚,所述芯片u8的18引脚连接电容c32,所述电容c32的另一端连接芯片u8的17引脚,所述芯片u8的16引脚连接模块p5的1引脚,所述模块p5的 3引脚连接gndiso端,所述芯片u8的15引脚连接模块p5的2引脚,所述芯片u8的14 引脚连接电容c33,所述电容c33的另一端连接芯片u8的13引脚,所述芯片u8的12引脚连接电容c34,所述电容c34的另一端连接芯片u8的11引脚和gndiso端;所述芯片 u7的2引脚连接电容c24,所述电容c24的另一端连接芯片u7的16引脚、5v电源端和电容c28,所述电容c28的另一端接地,芯片u7的14引脚连接模块p4的1你叫,所述芯片 u7的13引脚连接模块p4的2引脚,所述模块p4的3引脚接地,所述芯片u7的6引脚连接电容c27,所述电容c27的另一端连接接地端和芯片u7的15引脚,所述芯片u7的12 引脚连接rs232_rx引脚,所述芯片u7的11引脚连接rs232_tx引脚,所述芯片u7的5 引脚连接电容c26,所述电容c26的另一端连接芯片u7的4引脚,所述芯片u7的26引脚连接电容c25,所述电容c25的另一端连接芯片u7的1引脚。50.本实用新型的工作原理是:数据通过数据采集模块与通讯模块进行数据的采集和传输,其中利用上位机实时显示相应的数据,并判断数据是否正常,同时上位机通过通讯模块对数据结果进行捕捉和判断,发送控制信号到控制模块,实现信号的控制,从而实现对检测到的错误部件进行维修,减短维修的时间和维修的费用,保证航空公司的经济效益。51.对于本领域技术人员而言,显然本实用新型不限于上述示范性实施例的细节,而且在不背离本实用新型的精神或基本特征的情况下,能够以其他的具体形式实现本实用新型。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本实用新型的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本实用新型内。不应将权利要求中的任何附图标记视为限制所涉及的权利要求。52.此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150488.html

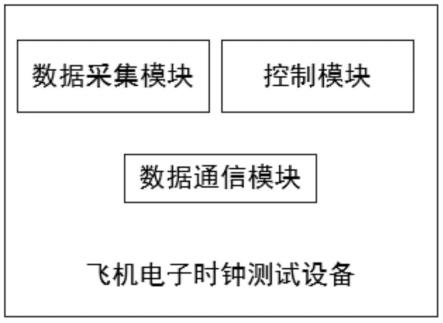

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表