一种可程控幅度和调制比的IRIG-BAC码产生电路的制作方法

- 国知局

- 2024-07-30 09:49:46

一种可程控幅度和调制比的irig-bac码产生电路技术领域1.本实用新型属于电子技术领域,具体为一种可程控幅度和调制比的irig-b ac码产生电路。背景技术:2.为达到irig-b码与时间信号输入、输出的精确同步,现有方案大多采用标准的irig-b码编码,从工程的角度出发,普遍使用现场可编程门阵列(fpga)来实现irig-b(dc))码编码和解码的设计方案和体系结构,设计中会涉及到几个不同的时钟频率,fpga对时钟的同步性具有灵活性、效率高、且功耗低。抗干扰性好的特点。结果表明,fpga 能够确保为从设备提供同源的时钟基准,使时钟与信号的延迟控制在 200ns以内,从而得到了irig-b(dc)码与时间精确同步的效果。3.然而,在实际的应用中,根据距离b码发生器的远近及不同时间精度的要求,b码在实际传输中采用了两种码型ac码(交流码)和dc 码(直流码)。当传输距离比较远时采用ac码,当传输距离近时则采用 dc码。ac码产生较dc码要复杂,大多在dc码基础上,增加辅助电路实现。在irigb dc码产生中,大多采用fpga和微处理器技术,将 gnss接收机的年月日时分秒时间信息和对应的秒脉冲信号,传递给 fpga单元,由fpga单元实现irigb dc码的编码控制,再由irigb dc 码,控制da转换器输出波形的幅度和频率,实现irigb dc码到ac 码的变换,由于其正弦波的真值表是预先产生与烧写,这种架构产生的ac码的幅度和调制比不能实现程控,调制比和幅度均不能实时改变,不能满足作为检验测试设备的要求。4.现有技术中,虽然具有转换成irigb ac码的功能;但是,要求 da转换器工作频率高、相应特性好,必然造成成本增加;不能实现 irigb ac码的输出幅度和输出调制比实时改变,可以程控的功能。技术实现要素:5.本实用新型的目的在于提供一种可程控幅度和调制比的irig-b ac码产生电路,以解决背景技术中提出的现有技术中,虽然具有转换成irigb ac码的功能;但是,要求da转换器工作频率高、相应特性好,必然造成成本增加;不能实现irigb ac码的输出幅度和输出调制比实时改变,可以程控的功能的问题。6.为解决上述技术问题,本实用新型所采用的技术方案是:7.一种可程控幅度和调制比的irig-b ac码产生电路,包括cpu处理单元、电平转换单元、正弦波产生单元、调制比控制单元、幅度控制单元以放大驱动单元;其中,cpu处理单元分别与电平转换单元、调制比控制单元和幅度控制单元连接;正弦波产生单元、调制比控制单元、幅度控制单元以放大驱动单元依次连接;8.电平转换单元还与外部的上位计算机连接,电平转换单元用于接收微处理发出的串口信号v1,并将接收到的串口信号v1经过转换为电平信号v4后输送到cpu处理单元,cpu处理单元用于将接收到的电平信号v4进行解码,并将解码得到的幅度和调制比设定转换为相应的幅度模拟控制电压v7和调制比模拟控制电压v9,并分别传输给调制比控制单元和幅度控制单元;9.正弦波产生单元还与外部的fpga单元连接;正弦波产生单元用于接收外部fpga单元传输的方波信号v2和v3;并产生正弦波信号v6,将产生的正弦波信号v6传递给调制比控制单元;调制比控制单元用于将接收到的正弦波信号转换为完成调制比控制的irig-b ac码信号 v8,并传递给幅度控制单元;幅度控制单元用于将接收到的irig-b ac 码信号转换为完成幅度控制的irig-b ac码信号v10,并传输给放大驱动单元,放大驱动单元用于输出完成幅度和调制比控制以放大驱动后的irig-b ac交流码输出信号v11。10.根据上述技术方案,方波信号v2为占空比1:1的1khz方波信号 v2,方波信号v3为占空比1:1的100khz方波信号。11.根据上述技术方案,正弦波产生单元包括滤波器u10;12.滤波器u10的1号引脚与电容c37的一端连接,电容c37的另一端接地;滤波器u10的1号引脚与电容c37的公共端与外部的fpga 连接,用于接收信号v3;13.滤波器u10的2号引脚与电容c36连接;滤波器u10的2号引脚与电容c36的公共端与电容c35的一端连接,电容c35的与电容c36 的公共端接地;滤波器u10的3号引脚与电容c41的一端连接;电容 c41的另一端与调制比控制单元连接;在滤波器u10的3号引脚与电容c41的公共端与电容c42的一端连接,电容c42的另一端分别与滤波器u10的4号引脚和电阻r24的一端连接;电阻r24的另一端分别与电阻r29、电容c44以及电阻r25的一端连接;其中,电阻r29的另一端与电容c43的一端连接,电容c43的另一端与滤波器u10的5 号引脚连接;14.电容c44的另一端接地;电阻r25的另一端与在滤波器u10的3 号引脚与电容c41的公共端连接;滤波器u10的6号引脚接地;滤波器u10的7号引脚与电容c34的一端连接,滤波器u10的7号引脚与电容c34的公共端与电容c33连接,电容c33与电容c34的公共端接地;滤波器u10的8号引脚与电容c40的一端连接,电容c40的另一端与外部的fpga连接,用于接收信号v2。15.根据上述技术方案,调制比控制单元包括高速开关u11、乘法器 u8;16.高速开关u11的5号引脚与5v电源连接,高速开关u11的6号引脚输入irig-b dc码信号v5,信号v5用于控制高速开关u11的电压输出;高速开关u11的7号引脚与15电源的负极连接;高速开关u11 的8号引脚与电阻r30的一端连接,电阻r30的另一端与5v电源连接;高速开关u11的8号引脚与电阻r30的公共端与电阻r32的一端连接,电阻r32的领一端接地;17.高速开关u11的1号引脚用于输出电压,高速开关u11的1号引脚还与乘法器u8的6号引脚连接;高速开关u11的2号引脚与cpu 处理单元连接,用于接收信号v7;高速开关u11的3号引脚接地;高速开关u11的4号引脚与15v电源的正极连接;18.乘法器u8的7号引脚接地;乘法器u8的2号引脚分别与电阻r27 和电阻r28的一端连接,电阻r27的另一端接地,电阻r28的另一端与电位器r25连接;19.乘法器u8的10号引脚分别与电容c46和电容c45的一端连接,电容c46和电容c45的公共端接地;乘法器u8的12号引脚接地;乘法器u8的14号引脚与幅度控制单元连接,用于输出信号v8;乘法器 u8的16号引脚分别与电容c39和电容c38的一端连接,电容c39和电容c38的公共端接地。20.根据上述技术方案,幅度控制单元包括乘法器u7;21.乘法器u7的1号引脚用于接收信号v8,乘法器u7的2号引脚接地,乘法器u7的6号引脚用于接收信号v9,乘法器u7的7号引脚接地;22.乘法器u7的10号引脚分别与电容c42与电容c43的一端连接,电容c42与电容c43的公共端接地;乘法器u7的12号引脚接地,乘法器u7的13号引脚接地;乘法器u7的14号引脚与放大驱动单元连接;用于输出信号v10;乘法器u7的16号引脚分别与电容c40和电容c41连接,电容c40和电容c41的公共端接地。23.根据上述技术方案,放大驱动单元包括运算放大器u9、变压器 t1;24.运算放大器u9的3号引脚用于接收信号v10,运算放大器u9的2 号引脚分别与电阻r27和电阻r22的一端连接;电阻r27的另一端接地,电阻r22的另一端与运算放大器u9的6号引脚连接;运算放大器 u9的4号引脚与15v电源的负极连接,运算放大器u9的7号引脚与 15v电源的正极连接;运算放大器u9的6号引脚还与电阻r16的一端连接;25.电阻r16的另一端与变压器t1的1号引脚连接,变压器t1的3 号引脚接地,变压器t1的6号引脚分别与电阻r17和电阻r21的一端连接,电阻r17的另一端输出信号v11;电阻r21的另一端分别与变压器t1的4号引脚以及电阻r23的一端连接;电阻r23的另一端与二极管fv1的一端连接,且电阻r23的另一端输出信号v11,二极管fv1 的另一端与电阻r17的连接。26.根据上述技术方案,电平转换单元包括芯片u1;27.芯片u1的1号引脚与电容c6的一端连接,电容c6的另一端与芯片u1的3号引脚连接;芯片u1的4号引脚与电容c9的一端连接,电容c9的另一端与芯片u1的7号引脚连接;芯片u1的7号引脚、8号引脚以及15号引脚均与外部的上位计算机连接,用于接收信号v1;芯片u1的16号引脚分别与电容c7和电容c11的一端连接,芯片u1 的16号引脚与电容c7和电容c11的公共端与3.3v电源连接,电容 c7的另一端与芯片u1的2号引脚连接;电容c11的另一端分别与电容c10和芯片u1的15号引脚连接,电容c11与电容c10和芯片u1 的15号引脚的公共端接地;28.芯片u1的9号引脚、10号引脚以及10号引脚均用于输出信号v4。29.根据上述技术方案,cpu处理单元包括芯片u4;30.芯片u4的1号引脚与3.3v电源连接;芯片u4的5号引脚分别与振荡器y2以及电容c23连接,振荡器y2的另一端分别与电容c24和芯片u4的6号引脚连接;电容c23的另一端与电容c24的另一端连接,电容c23与电容c24的公共端接地;31.芯片u4的7号引脚分别与电容c18和电阻r2的一端连接,电容 c18的另一端接地,电阻r2的另一端与3.3v电源连接;32.芯片u4的12号引脚接地;芯片u4的13号引脚分别与电阻r10 和电容c25的一端连接,电阻r10的另一端分别与电容c29和芯片u4 的19号引脚连接;电容c25的另一端分别与电容c29以及芯片u4的 18号引脚连接;33.电阻r10、电容c29和芯片u4的19号引脚的公共端与3.3v电源连接;电容c25、电容c29和芯片u4的18号引脚的公共端接地;34.芯片u4的20号引脚与高速开关u11的2号引脚连接;芯片u4 的21号引脚与乘法器u7的6号引脚连接;芯片u4的29号引脚与芯片u1的10号引脚连接,芯片u4的30号引脚与芯片u1的9号引脚连接;35.芯片u4的31号引脚与电容c30的一端连接,电容c30的另一端与芯片u4的32号引脚连接;芯片u4的31号引脚与电容c30的公共端接地;电容c30的与芯片u4的32号引脚的公共端与3.3v电源连接;36.芯片u4的64号引脚分别与3.3v电源和电容c19的一端连接;电容c19的另一端与芯片u4的63号引脚连接;电容c19与芯片u4的 63号引脚的公共端接地;37.芯片u4的48号引脚分别与3.3v电源以及电容c28的一端连接,电容c28的另一端与芯片u4的47号引脚连接,电容c28与u4的47 号引脚的公共端接地。38.与现有技术相比,本实用新型具有以下有益效果:39.本实用新型具有实现电路简单可靠,控制精细度高;可以通过程序进行调控;幅度和调制比均可控制的优点。附图说明40.图1为本实用新型流程图;41.图2为本实用新型正弦波产生单元电路图;42.图3为本实用新型调制比控制单元电路图;43.图4为本实用新型幅度控制单元电路图;44.图5为本实用新型放大驱动单元电路图;45.图6为本实用新型电平转换单元电路图;46.图7为本实用新型cpu处理单元电路图。具体实施方式47.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。48.实施例一49.如图1所示,一种可程控幅度和调制比的irig-b ac码产生电路,包括cpu处理单元、电平转换单元、正弦波产生单元、调制比控制单元、幅度控制单元以放大驱动单元;其中,cpu处理单元分别与电平转换单元、调制比控制单元和幅度控制单元连接;正弦波产生单元、调制比控制单元、幅度控制单元以放大驱动单元依次连接;50.电平转换单元还与外部的上位计算机连接,电平转换单元用于接收微处理发出的串口信号v1,并将接收到的串口信号v1经过转换为电平信号v4后输送到cpu处理单元,cpu处理单元用于将接收到的电平信号v4进行解码,并将解码得到的幅度和调制比设定转换为相应的幅度模拟控制电压v7和调制比模拟控制电压v9,并分别传输给调制比控制单元和幅度控制单元;51.正弦波产生单元还与外部的fpga单元连接;正弦波产生单元用于接收外部fpga单元传输的方波信号v2和v3;并产生正弦波信号v6,将产生的正弦波信号v6传递给调制比控制单元;调制比控制单元用于将接收到的正弦波信号转换为完成调制比控制的irig-b ac码信号 v8,并传递给幅度控制单元;幅度控制单元用于将接收到的irig-b ac 码信号转换为完成幅度控制的irig-b ac码信号v10,并传输给放大驱动单元,放大驱动单元用于输出完成幅度和调制比控制以放大驱动后的irig-b ac交流码输出信号v11。52.进一步的,方波信号v2为占空比1:1的1khz方波信号v2,方波信号v3为占空比1:1的100khz方波信号。53.本实用新型具有实现电路简单可靠,控制精细度高;可以通过程序进行调控;幅度和调制比均可控制的优点。54.实施例二55.本实施例为实施例一的进一步细化。如图2所示,正弦波产生单元包括滤波器u10;56.滤波器u10的1号引脚与电容c37的一端连接,电容c37的另一端接地;滤波器u10的1号引脚与电容c37的公共端与外部的fpga 连接,用于接收信号v3;57.滤波器u10的2号引脚与电容c36连接;滤波器u10的2号引脚与电容c36的公共端与电容c35的一端连接,电容c35的与电容c36 的公共端接地;滤波器u10的3号引脚与电容c41的一端连接;电容 c41的另一端与调制比控制单元连接;在滤波器u10的3号引脚与电容c41的公共端与电容c42的一端连接,电容c42的另一端分别与滤波器u10的4号引脚和电阻r24的一端连接;电阻r24的另一端分别与电阻r29、电容c44以及电阻r25的一端连接;其中,电阻r29的另一端与电容c43的一端连接,电容c43的另一端与滤波器u10的5 号引脚连接;58.电容c44的另一端接地;电阻r25的另一端与在滤波器u10的3 号引脚与电容c41的公共端连接;滤波器u10的6号引脚接地;滤波器u10的7号引脚与电容c34的一端连接,滤波器u10的7号引脚与电容c34的公共端与电容c33连接,电容c33与电容c34的公共端接地;滤波器u10的8号引脚与电容c40的一端连接,电容c40的另一端与外部的fpga连接,用于接收信号v2。59.滤波器u10采用先有装置,例如max292滤波器电路。60.电容c33、电容c34、电容c35、电容c36是+5v电源和-5v电源供电的滤波和退耦电容,用以消除电源干扰。61.电容c40是信号的隔直电容,将1khz方波信号v2传输到滤波器 u10的8号引脚的in端;62.电容c37是滤波器u10工作时钟信号100khz信号v3的滤波电容,滤除传输线上干扰;63.电容c43是滤波器u10内部8阶梯形滤波器输出耦合电容,将梯形滤波器输出信号耦合到滤波器u10内部独立运算放大器的输入端;64.电阻r29、电阻r24、电阻r25,电容c42、电容c44与滤波器u10 内部独立运算放大器,组成2阶巴特沃斯低通滤波器,该滤波器输出即为1khz正弦波,经过电容c41耦合至调制比控制单元。65.实施例三66.本实施例为实施例二的进一步细化。如图3所示,调制比控制单元包括高速开关u11、乘法器u8;67.高速开关u11的5号引脚与5v电源连接,高速开关u11的6号引脚输入irig-b dc码信号v5,信号v5用于控制高速开关u11的电压输出;高速开关u11的7号引脚与15电源的负极连接;高速开关u11 的8号引脚与电阻r30的一端连接,电阻r30的另一端与5v电源连接;高速开关u11的8号引脚与电阻r30的公共端与电阻r32的一端连接,电阻r32的领一端接地;68.高速开关u11的1号引脚用于输出电压,高速开关u11的1号引脚还与乘法器u8的6号引脚连接;高速开关u11的2号引脚与cpu 处理单元连接,用于接收信号v7;高速开关u11的3号引脚接地;高速开关u11的4号引脚与15v电源的正极连接;69.乘法器u8的7号引脚接地;乘法器u8的2号引脚分别与电阻r27 和电阻r28的一端连接,电阻r27的另一端接地,电阻r28的另一端与电位器r25连接;70.乘法器u8的10号引脚分别与电容c46和电容c45的一端连接,电容c46和电容c45的公共端接地;乘法器u8的12号引脚接地;乘法器u8的14号引脚与幅度控制单元连接,用于输出信号v8;乘法器 u8的16号引脚分别与电容c39和电容c38的一端连接,电容c39和电容c38的公共端接地。71.进一步的,高速开关u11以及乘法器u8均采用现有装置,例如高速开关u11采用max319高速开关电路,乘法器u8采用mpy634ku乘法器。72.irig-b dc码信号v5输入到高速开关max319的6号引脚,控制其高速开关u11的1号引脚的输出电压vsw;在irig-b dc码信号v5 信号高电平时,等于固定电压3.0v,irig-b dc码信号v5信号高电平时,等于将d/a转换单元输出的信号v7输入到乘法器u8的6号引脚;73.电容c38、电容c39、电容c45、电容c46构成电源的滤波电路,滤除电源干扰噪声;74.电位器r25和电阻r28、电阻r27构成偏置电压调整电路,其输出电压vadj输入到乘法器u8的2号引脚内,用来调整1khz正弦波信号的相位;75.1khz正弦波信号v6输入到乘法器u8的1号引脚内;76.乘法器u8输出信号v8是经过调制比控制输出信号。77.实施例四78.本实施例为实施例二的进一步细化。如图4所示,幅度控制单元包括乘法器u7;79.乘法器u7的1号引脚用于接收信号v8,乘法器u7的2号引脚接地,乘法器u7的6号引脚用于接收信号v9,乘法器u7的7号引脚接地;80.乘法器u7的10号引脚分别与电容c42与电容c43的一端连接,电容c42与电容c43的公共端接地;乘法器u7的12号引脚接地,乘法器u7的13号引脚接地;乘法器u7的14号引脚与放大驱动单元连接;用于输出信号v10;乘法器u7的16号引脚分别与电容c40和电容c41连接,电容c40和电容c41的公共端接地。81.进一步的,乘法器u7采用先有装置,例如mpy634ku乘法器。82.电容c40、电容c41、电容c42、电容c43构成电源的滤波电路,滤除电源干扰噪声;83.调制比控制单元输出信号的v8输入到乘法器u7的1号引脚内;84.cpu处理单元输出的信号v9输入到乘法器u7的6号引脚内;85.乘法器u7的14号引脚输出信号v10,是信号v8和信号v9的乘积,实现了irig-b ac码输出幅度受cpu处理单元输出的控制。86.实施例五87.本实施例为实施例二的进一步细化。如图5所示,放大驱动单元包括运算放大器u9、变压器t1;88.运算放大器u9的3号引脚用于接收信号v10,运算放大器u9的2 号引脚分别与电阻r27和电阻r22的一端连接;电阻r27的另一端接地,电阻r22的另一端与运算放大器u9的6号引脚连接;运算放大器 u9的4号引脚与15v电源的负极连接,运算放大器u9的7号引脚与 15v电源的正极连接;运算放大器u9的6号引脚还与电阻r16的一端连接;89.电阻r16的另一端与变压器t1的1号引脚连接,变压器t1的3 号引脚接地,变压器t1的6号引脚分别与电阻r17和电阻r21的一端连接,电阻r17的另一端输出信号v11;电阻r21的另一端分别与变压器t1的4号引脚以及电阻r23的一端连接;电阻r23的另一端与二极管fv1的一端连接,且电阻r23的另一端输出信号v11,二极管fv1 的另一端与电阻r17的连接。90.进一步的,运算放大器u9采用现有装置,例如,lm7321运算放大器。91.经过幅度控制和对比度控制的irig-b ac码信号v10输入运算放大器u9,改变电阻r20、电阻r27可以改变运算放大器u9的增益,电阻r16是运算放大器u9输出阻抗匹配电阻;92.变压器t1,实现阻抗匹配、信号隔离与变换,电阻r17、电阻r23 是外部传输电路阻抗匹配电阻;电阻r21是外部断开时的能量吸收电阻;二极管fv1是输出保护,抑制外部电路的浪涌对内部电路的影响。93.信号(11)+和(11)-是电路最终平衡输出信号。94.实施例六95.本实施例为实施例二的进一步细化。如图6所示,电平转换单元包括芯片u1;96.芯片u1的1号引脚与电容c6的一端连接,电容c6的另一端与芯片u1的3号引脚连接;芯片u1的4号引脚与电容c9的一端连接,电容c9的另一端与芯片u1的7号引脚连接;芯片u1的7号引脚、8号引脚以及15号引脚均与外部的上位计算机连接,用于接收信号v1;芯片u1的16号引脚分别与电容c7和电容c11的一端连接,芯片u1 的16号引脚与电容c7和电容c11的公共端与3.3v电源连接,电容 c7的另一端与芯片u1的2号引脚连接;电容c11的另一端分别与电容c10和芯片u1的15号引脚连接,电容c11与电容c10和芯片u1 的15号引脚的公共端接地;97.芯片u1的9号引脚、10号引脚以及10号引脚均用于输出信号v4。98.进一步的,芯片u1采用现有装置,例如max3232电平转换电路。99.电容c6、电容c9是芯片内部自举电源振荡电容;电容c7、电容 c10是内部自举电源的滤波电容;电容c11是芯片电源退耦电容。100.上位计算机传送控制命令的rs232接口信号v1,与芯片u1的7、 8、15还引脚连接;经过芯片u1转换成ttl电平信号v4,输入到cpu 处理单元。101.实施例七102.本实施例为实施例二的进一步细化。如图7所示,cpu处理单元包括芯片u4;103.芯片u4的1号引脚与3.3v电源连接;芯片u4的5号引脚分别与振荡器y2以及电容c23连接,振荡器y2的另一端分别与电容c24和芯片u4的6号引脚连接;电容c23的另一端与电容c24的另一端连接,电容c23与电容c24的公共端接地;104.芯片u4的7号引脚分别与电容c18和电阻r2的一端连接,电容 c18的另一端接地,电阻r2的另一端与3.3v电源连接;105.芯片u4的12号引脚接地;芯片u4的13号引脚分别与电阻r10 和电容c25的一端连接,电阻r10的另一端分别与电容c29和芯片u4 的19号引脚连接;电容c25的另一端分别与电容c29以及芯片u4的 18号引脚连接;106.电阻r10、电容c29和芯片u4的19号引脚的公共端与3.3v电源连接;电容c25、电容c29和芯片u4的18号引脚的公共端接地;107.芯片u4的20号引脚与高速开关u11的2号引脚连接;芯片u4 的21号引脚与乘法器u7的6号引脚连接;芯片u4的29号引脚与芯片u1的10号引脚连接,芯片u4的30号引脚与芯片u1的9号引脚连接;108.芯片u4的31号引脚与电容c30的一端连接,电容c30的另一端与芯片u4的32号引脚连接;芯片u4的31号引脚与电容c30的公共端接地;电容c30的与芯片u4的32号引脚的公共端与3.3v电源连接;109.芯片u4的64号引脚分别与3.3v电源和电容c19的一端连接;电容c19的另一端与芯片u4的63号引脚连接;电容c19与芯片u4的 63号引脚的公共端接地;110.芯片u4的48号引脚分别与3.3v电源以及电容c28的一端连接,电容c28的另一端与芯片u4的47号引脚连接,电容c28与u4的47 号引脚的公共端接地。111.进一步的,芯片u4采用现有装置,例如stm32f103rct6微处理器。112.电容c18、电阻r2构成了芯片u4的上电复位电路;113.电容c19、电容c28、电容c30、电容c29是芯片u4的电源退耦电容;114.振荡器y2是石英晶体振荡器,是芯片u4主时钟产生器,电容c23、电容c24是石英晶体振荡电容。115.电阻r10和电容c25构成rc滤波电路,对3.3v数字电源滤波后,作为芯片u4的模拟电源;116.cpu通过串口3接受上位机的调制比和幅度设置命令,分别将设置值转换成对应的电压,通过信号v7、信号v9输出。117.本实用新型的工作原理为:118.外部输入与irig-b dc码同步的100khz信号v3、1khz信号v2 占空比1:1的方波信号,两路信号,由1khz正弦波产生单元内部的滤波器电路,生成1khz正弦波信号v6。119.外部输入信号v5:irig-b dc码;控制调制比控制单元内部高速高速开关u11,在irig-b dc码低电平时,高速开关u11的输出等于 cpu处理单元输出的信号v7,信号v7电压输出范围是0.5v~1.5v;在irig-b dc码高电平时,高速开关u11的输出等于固定电压3.0v。120.调制比控制单元内部的乘法器u8,将高速开关u11的输出和1khz 正弦波信号v6相乘,正弦波信号v6的幅度ain受高速开关u11输出的调制,调制比控制单元输出信号v8,只要改变信号v7的数值v7就可以实现调制比控制,由于cpu是12位da转换器,在0.5v~1.5v范围内可以实现调制比千分之一步进分辨率。121.aout=3.0*ain(irig-b dc=1);122.aout=v7*ain(irig-b dc=0);123.幅度控制单元内部的乘法器u7,将调制比控制单元的输出信号 v8和cpu处理单元输出的信号v9相乘,信号v9电压输出范围是 0.2v~3.0v信号v9幅度aadj;124.aout=aadj*3.0*ain(irig-b dc=1);125.aout=aadj*v7*ain(irig-b dc=0);126.幅度控制单元输出信号v10,只要改变信号v9的数值aadj就可以实现幅度控制。127.幅度控制单元输出信号v10通过放大驱动单元实现irig-b ac码输出。128.需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。129.最后应说明的是:以上所述仅为本实用新型的优选实施例而已,并不用于限制本实用新型,尽管参照前述实施例对本实用新型进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240730/151045.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

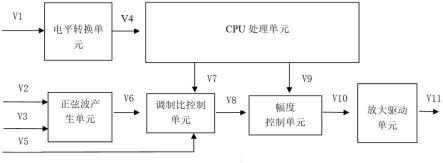

一种节拍提示器的制作方法

下一篇

返回列表