一种嵌套式延时锁定环电路及游标型时间数字转换器

- 国知局

- 2024-07-30 10:08:00

本发明涉及时间数字转换器,更具体的,涉及一种嵌套式延时锁定环电路及游标型时间数字转换器。

背景技术:

1、基于游标环形延时链的时间数字转换器(time-to-digital converter,tdc)是游标型时间数字转换器的一种架构,具备高分辨率和大量程的优点,同时所占面积较小,是实现高动态范围tdc的重要架构。该tdc广泛应用于自动驾驶的脉冲式激光雷达系统,辅助激光雷达系统准确探测和分辨以车辆为中心上百米范围内的物体。

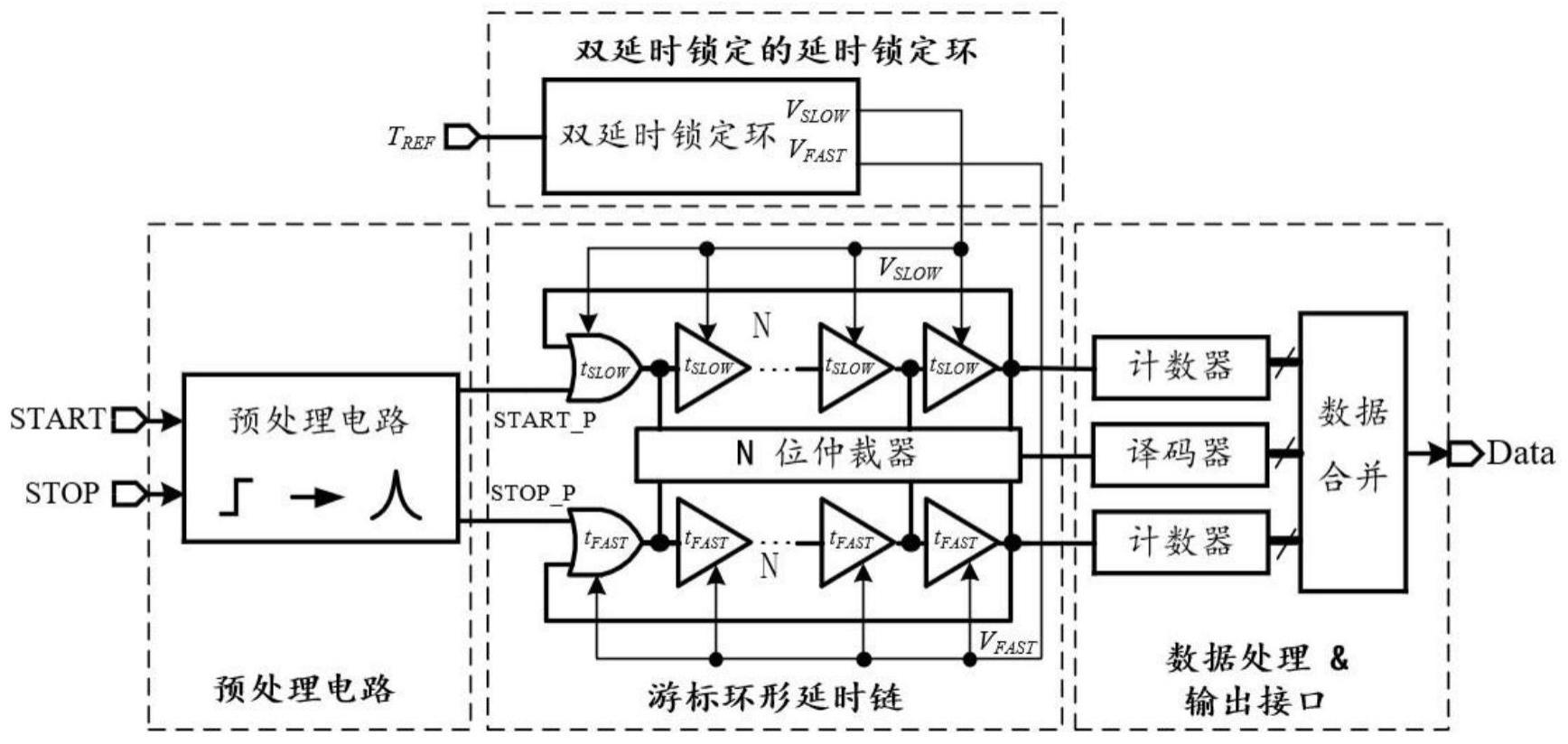

2、如图1所示,基于游标环形延时链的tdc架构包括:预处理电路检测代表激光脉冲发射与接收时刻的电信号(start/stop)的上升沿,并将其整形为窄脉冲信号;游标环形延时链量化start/stop脉冲的时间差;数据处理模块包括计数器、译码器、分段数据合并电路和串行输出接口电路,生成最终的量化飞行时间;双延时锁定的延时锁定环(也称双延时锁定环)为游标环形延时链电路提供两个延时控制电压。

3、基于游标环形延时链的tdc的基本原理是使代表发射与接收时刻的两个脉冲信号分别在慢、快环形延时链中传播,并以慢、快延时单元的延时之差为时间分辨率进行追赶,最终通过仲裁器识别两个脉冲信号的追赶时刻。激光脉冲的飞行时间将由慢、快环形延时链的计数值及脉冲信号在两个链中的追赶时刻共同决定。

4、游标环形延时链tdc单次测量的飞行时间可表示为

5、t=a1·(btslow)+a2·[b(tslow-vfast)]+a3·(tslow-tfast)

6、其中,tslow、tfast分别为慢、快延时单元的延时;a1为慢延时链的计数值;a2为快延时链的计数值;a3为仲裁器输出的脉冲信号在两个链中的追赶时刻;b为环形延时链上延时单元级数(快、慢延时链延时单元的级数一样)。

7、理想情况下,基于游标环形延时链的tdc的分辨率为两环形延时链延时单元的延时之差,不受工艺最小门延时的限制。然而,延时单元易受工艺、电源电压、温度(process,voltage,temperature,pvt)影响。因此需要采用延时锁定环(delay-locked loop,dll)来对延时单元进行闭环控制,避免延时单元的延时随pvt偏移。基于游标环形延时链的tdc需要两个控制快、慢延时链的电压。

8、如图2所示,经典方案的双延时锁定环采用m级延时链的dll和n级延时链的dll构成,产生的快、慢延时分别为此时,tdc的分辨率为该结构生成的tslow:tslow-tfast不成二次幂关系,导致tdc分段量化之后需要采用乘法、除法和求和等运算电路将各段的分辨率的归一化,进行数据合并,这增加了实现的复杂度,并且占用较大面积。

9、如图3所示,有研究团队提出了主从式延时锁定环来替代传统方案,将主dll延时链上相邻两个节点连接作为从dll的参考时钟。主dll控制慢延时为从dll控制tp(x)+tslow·n=tp(x+1)+tfast·n,可得tdc分辨率通过设定n为二次幂,可实现tslow:tslow-tfast成二次幂关系,对这三段量化的数据进行合并时不需要采用乘法、除法和求和运算,而是只需将量化值锁存到寄存器中,降低了数据处理复杂度。然而,出于成本考虑,片外高质量参考时钟tref使用较低频率(低于百兆赫兹)的晶振产生。为了实现10ps以下的分辨率,主从式dll每条延时链延时个数至少需要几十个,这一定程度造成功耗与面积的消耗,并且较长的延时链难以匹配各延时单元。dll锁定只能确保延时链的总延时为参考时钟周期,但难以保证各延时单元延时均一,导致tdc量化偏差。

技术实现思路

1、本发明为了解决以上现有技术存在的不足与缺陷问题,提供了一种嵌套式延时锁定环电路及游标型时间数字转换器。

2、为实现上述本发明目的,采用的技术方案如下:

3、一种嵌套式延时锁定环电路,包括m级压控延时链、第一n级压控延时链、第二n级压控延时链、第一鉴相器、第二鉴相器、第三鉴相器、第一电荷泵、第二电荷泵、第三电荷泵、第一环路滤波电容、第二环路滤波电容,第三环路滤波电容、m选1选择器;

4、其中,所述的m级压控延时链的输入端用于输入片外低频时钟,所述的第一鉴相器的第一输入端与m级压控延时链的输出端电性连接;所述的第一鉴相器的第二输入端用于输入片外低频时钟;

5、所述的第一鉴相器的输出端与第一电荷泵的输入端电性连接;所述的第一电荷泵的输出端输出第一压控电压;同时所述的第一电荷泵的输出端还分别与m级压控延时链中的各个延时单元、第一环路滤波电容的一端电性连接;所述的第一环路滤波电容的另一端接地;

6、所述的m选1选择器的选择端分别与m级压控延时链中的各个延时单元的输出端电性连接;所述的m选1选择器的控制端用于输入控制字k;所述的m选1选择器的输出端与第二鉴相器的第一输入端电性连接;

7、所述的第一n级压控延时链的输入端用于输入片外低频时钟,第一n级压控延时链的输出端与第二鉴相器的第二输入端电性连接;

8、所述的第二鉴相器的输出端与第二电荷泵的输出端电性连接;所述的第二电荷泵的输出端用于输出第二压控电压;同时所述的第二电荷泵的输出端还分别与第一n级压控延时链中的各个延时单元、第二环路滤波电容的一端电性连接;所述的第二环路滤波电容的另一端接地;

9、所述的第三鉴相器的第一输入端与第一n级压控延时链中第n-1个延迟单元的输出端电性连接;

10、所述的第二n级压控延时链的输入端用于输入片外低频时钟,第二n级压控延时链的输出端与第三鉴相器的第二输入端电性连接;

11、所述的第三鉴相器的输出端与第三电荷泵的输入端电性连接;所述的第三电荷泵的输出端输出第三压控电压;同时所述的第三电荷泵的输出端还分别与第二n级压控延时链中的各个延时单元、第三环路滤波电容的一端电性连接;所述的第三环路滤波电容的另一端接地。

12、优选地,所述的m级压控延时链、第一鉴相器、第一电荷泵、第一环路滤波电容组成第一级延时锁定环;

13、所述的第一n级压控延时链、第二鉴相器、第二电荷泵、第二环路滤波电容组成第二级延时锁定环;

14、所述的第二n级压控延时链、第三鉴相器、第三电荷泵、第三环路滤波电容组成第三级延时锁定环。

15、进一步地,在所第三级延时锁定环之后还可嵌套有一个第四级延时锁定环。

16、再进一步地,所述的第四级延时锁定环包括1个第三n级压控延时链、第四鉴相器、第四电荷泵、第四环路滤波电容;

17、在第二n级压控延时链的输出端新增一个第一延时单元;且第三电荷泵的输出与第一延时单元电性连接;

18、所述的第三n级压控延时链的输入端用于输入片外低频时钟;所述第三n级压控延时链的输出端与第四鉴相器的第一输入端电性连接;

19、所述的第四鉴相器的第二输入端与第一延时单元的输出端电性连接;

20、所述的第四鉴相器的输出端与第四电荷泵的输入端电性连接;所述的第四电荷泵的输出端输出第四压控电压;同时所述的第四电荷泵的输出端还分别与第三n级压控延时链中的各个延时单元、第四环路滤波电容的一端电性连接;所述的第四环路滤波电容的另一端接地。

21、再进一步地,所述的第一级延时锁定环实现片外低频时钟tref在m级压控延时链中的传播,通过第一鉴相器比较经过m级压控延时链传播的时钟信号的相位与原始参考时钟信号的相位,输出第一相位差;

22、所述的第一电荷泵根据第一鉴相器输出的第一相位差产生相应电流,对第一环路滤波电容进行充电或放电,以调整m级压控延时链的压控电压值,控制m级压控延时链的单位延时;经过m级压控延时链传播的时钟信号的相位发生改变直到与原始参考时钟的相位对齐;相位对齐后,第一级延时锁定环锁定,此时m级压控延时链的单位延时为

23、再进一步地,所述的第二级延时锁定环实现片外低频时钟tref在第一n级压控延时链中的传播,通过第二鉴相器比较经过第一n级压控延时链传播的时钟信号的相位与所述的m选1选择器输出信号的相位,输出第二相位差;

24、所述的第二电荷泵根据所述的第二相位差产生相应电流,对第二环路滤波电容进行充电或放电,以调整第一n级压控延时链的压控电压值,控制第一n级压控延时链的单位延时;

25、经过第一n级压控延时链传播的时钟信号的相位发生改变直到与m选1选择器输出信号的相位对齐;相位对齐后,第二级延时锁定环锁定,此时第一n级压控延时链的单位延时为将第一n级压控延时链的第二压控电压vslow作用于时间数字转换器的慢链延时单元,则慢延时为

26、再进一步地,所述的第三级延时锁定环实现片外低频时钟tref在第二n级压控延时链中的传播,通过第三鉴相器比较经过第二n级压控延时链传播的时钟信号的第n个延时单元的相位与第一n级压控延时链中第n-1个延时单元的相位,输出第三相位差;

27、第三电荷泵根据第三相位差产生相应电流,对第三环路滤波电容进行充电或放电,以调整第二n级压控延时链的压控电压值,控制第二n级压控延时链的单位延时;

28、经过第二n级压控延时链传播的时钟信号的第n个延时单元的相位发生改变直到与第一n级压控延时链中第n-1个延时单元的相位对齐;相位对齐后,第三级延时锁定环锁定,此时第二n级压控延时链的单位延时为将第二n级压控延时链的第三压控电压vfast可作用于时间数字转换器的快链延时单元,则快延时为

29、再进一步地,所述的第四级延时锁定环实现片外低频时钟tref在第三n级压控延时链中的传播,通过第四鉴相器比较经过第三n级压控延时链传播的时钟信号的相位与第一延时单元输出信号的相位,输出第四相位差;

30、所述的第四电荷泵根据第四相位差产生相应电流,对第四环路滤波电容进行充电或放电,以调整第三n级压控延时链的压控电压值,控制第三n级压控延时链的单位延时;

31、经过第三n级压控延时链传播的时钟信号的相位发生改变直到与第一延时单元输出信号的相位对齐;相位对齐后,第四级延时锁定环锁定,此时第三n级压控延时链的单位延时为将第三n级压控延时链的第四压控电压vfast2可作用于时间数字转换器的快链延时单元,则快延时为

32、一种游标型时间数字转换器,包括如所述的嵌套式延时锁定环电路、预处理电路、游标环形延时链、数据处理及输出接口;

33、所述的预处理电路用于检测激光脉冲发射与接收时刻的电信号脉冲的上升沿,并将其整形为窄脉冲信号;

34、所述的游标环形延时链量化电信号脉冲的时间差;

35、所述的嵌套式延时锁定环电路为游标环形延时链电路提供两个压控电压;

36、所述的数据处理模块将游标环形延时链电路输出的电信号脉冲生成最终的量化飞行时间。

37、优选地,所述的游标环形延时链电路包括慢链延时单元、快链延时单元;

38、所述的第一n级压控延时链的第二压控电压vslow作用于游标环形延时链电路的慢链延时单元,和所述的第二n级压控延时链的第三压控电压vfast作用于游标环形延时链电路的快链延时单元;

39、或者所述的第一n级压控延时链的第二压控电压vslow作用于游标环形延时链电路的慢链延时单元,和所述的第三n级压控延时链的第四压控电压vfast2作用于游标环形延时链电路的快链延时单元,则快延时为

40、本发明的有益效果如下:

41、本发明采用多级嵌套式延时锁定环,不仅能够抑制延时单元的延时随pvt偏移,并且能够高效地实现延时成特定比例关系的快慢延时单元,在进行数据合并时无需进行多余的运算,从而降低数据处理的复杂度和功耗。

42、此外,本发明在较低频率晶振时钟信号输入下,无需大量延时单元个数,即可实现10ps以下级别的时间分辨率。

43、本发明在游标型时间数字转换器引入嵌套式延时锁定环,在实现快慢延时比例关系可控和高分辨率的同时,明显降低所需延时单元的级数,并降低了游标型时间数字转换器分段量化后数据合并的复杂度,通过调节外部控制字可配置tdc的分辨率。

本文地址:https://www.jishuxx.com/zhuanli/20240730/151756.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表