一种基于SerDes的TDC实现装置

- 国知局

- 2024-07-30 10:08:28

本发明属于时间间隔测量领域,具体涉及一种基于serdes的tdc实现装置。

背景技术:

1、在现代科学和工业的诸多工作场景中,经常需要对两个或多个物理事件之间的时间间隔进行精确的测量。例如锁相环中测量环路和参考时钟之间的差异以避免时钟漂移,或是测量发射和接收之间的时间,以发现关于信号所反射的物体或信号所经过的环境信息,此外,在核物理、量子实验、医疗成像等领域中也有广泛的应用。

2、目前,数字转换器(time-to-digital convertor,tdc)被大量用来实现时间间隔的测量,其部署方式有专用tdc芯片、基于现场可编程逻辑门阵列(field programmablegate array,fpga)的tdc电路等,其中以基于fpga的tdc实现最为主流,也能更好适应各类不同应用场景。现有基于fpga的tdc主要通过数据延时链或时钟多路移相来实现高精度测量,数据延时链的方式对fpga内部布局布线要求极高,数据通过各类延迟单元的延迟时间不够稳定,影响tdc的线性度,同时延迟链的长度有线,导致测量范围较小,无法适用于大时间间隔测量。时钟多路相移的方式是在fpga外部,通过时钟管理和时钟相移模块,对采样时钟进行多路相移,将相移后的多个时钟对数据进行采样,从而等效的提高了采样率,进而提高了测量精度,通常能达到纳秒级。此方法测量范围较大,但在fpga外部增加了复杂的时钟模块,成本较高。

技术实现思路

1、本发明的目的在于:提供一种基于serdes的tdc实现其装置,以解决目前tdc结构复杂、测量精度与测量范围无法兼顾导致应用范围窄的问题。

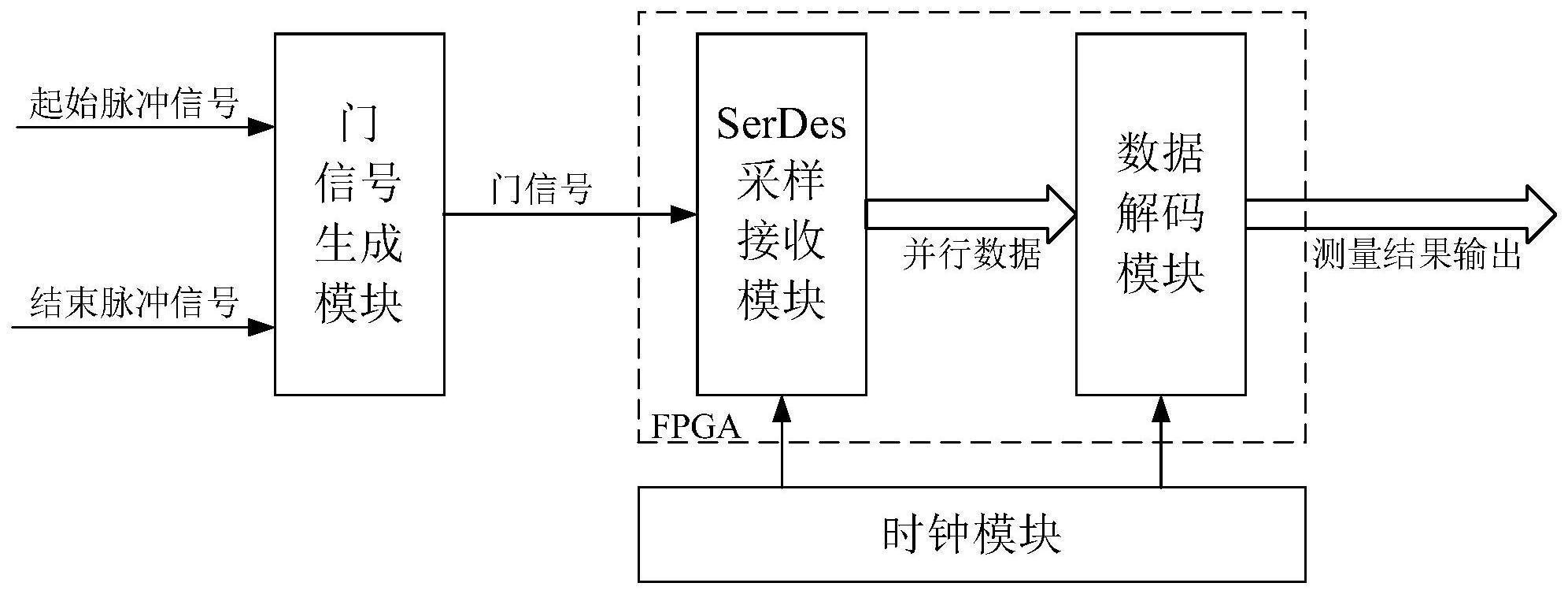

2、一种基于serdes的tdc实现装置,包括:时钟模块、门信号生成模块、serdes采样接收模块和数据解码模块;

3、所述的时钟模块分别为serdes采样接收模块和数据解码模块提供同步的参考时钟信号;所述门信号生成模块接收时间起始和时间结束信号,将两个信号包含的时间间隔信息转化为具有与被测时间间隔相同门宽度的门信号,输出到serdes采样接收模块;

4、所述的serdes采样接收模块包括锁相环模块与接收器,锁相环连接时钟模块,用于接收参考时钟信号并对其进行倍频分频处理,得到工作时钟信号发送至接收器;接收器连接门信号生成模块,用于对门信号进行采样,根据接收的工作时钟信号将采样的门信号由高速串行数据转换为低速并行数据发送至数据解码模块;

5、所述的数据解码模块连接serdes采样接收模块,以时钟模块提供的参考时钟为依据,对接收的serdes输出的低速并行数据进行运算解码,得到门信号的持续时间,从而完成时间间隔的测量。

6、进一步的,所述的门信号生成模块由起始脉冲信号接收电路、结束脉冲信号接收电路和门信号合成电路组成;起始脉冲信号接收电路接收时间起始信号,结束脉冲信号接收电路接收时间结束信号,门信号合成模块根据门信号宽度对时间起始信号和时间结束信号进行合成得到门信号输出;时间起始信号为电路检测起始脉冲信号的上升沿,时间结束信号为电路检测结束脉冲信号的上升沿,门信号的宽度为起始脉冲信号与结束脉冲信号上升沿之间的时间间隔;门信号可视为高速的串行数据。

7、进一步的,所述数据解码模块的解码方法为:

8、s1、对接收的低速并行数据中的“0”和“1”进行识别和计数,当识别的低速并行数据中开始出现“1”时,对数据中的“1”进行计数;当识别的低速并行数据中出现“0”时,停止计数并输出计数值;计数值表示接收的低速并行数据中“1”的个数,一个“1”表示门信号持续了一个serdes采样时钟周期;

9、s2、根据s1得到的计数值和时钟模块提供的参考时钟信号计算出输入时间间隔δt,完成时间间隔的测量。

10、本发明提供的一种基于serdes的tdc实现装置,是基于fpga内部serdes资源可达到超高数据率的特点,其工作时钟可达到数十吉赫兹,实现了皮秒级的时间分辨率,又因为serdes采样输出为较低速的fpga可实时处理的并行数据,配合对存储深度不敏感的数据解码模块,使时间间隔测量范围提升至秒级。此外,得益于serdes采样接收模块中的高性能锁相环和移位寄存器统一的标准延时特点,使得基于serdes的tdc拥有更好的线性性能,同时省去了时钟多路相移方法中的复杂时钟电路,简化了fpga外围电路设计,降低了fpga所需io口数量和系统复杂度,进而拓宽了其应用范围。

11、与现有技术相比,本发明具有结构简单,成本较低,线性性能较好等特点,实现高精度的同时拥有较大测量范围,且能够大幅度简化tdc的部署要求,有助于扩大tdc的应用范围。

技术特征:1.一种基于serdes的tdc实现方法装置,包括:时钟模块、门信号生成模块、serdes采样接收模块和数据解码模块,其特征在于:

2.根据权利要求1所述的一种基于serdes的tdc实现方法装置,其特征在于:所述的门信号生成模块由起始脉冲信号接收电路、结束脉冲信号接收电路和门信号合成电路组成;起始脉冲信号接收电路接收时间起始信号,结束脉冲信号接收电路接收时间结束信号,门信号合成模块根据门信号宽度对时间起始信号和时间结束信号进行合成得到门信号输出;时间起始信号为电路检测起始脉冲信号的上升沿,时间结束信号为电路检测结束脉冲信号的上升沿,门信号的宽度为起始脉冲信号与结束脉冲信号上升沿之间的时间间隔;门信号可视为高速的串行数据。

3.根据权利要求1~2任一项所述的一种基于serdes的tdc实现方法装置,其特征在于:所述数据解码模块的解码方法为:

技术总结本发明属于时间间隔测量领域,具体为一种基于SerDes的TDC实现装置,包括时钟模块、门信号生成模块、SerDes采样接收模块和数据解码模块。该装置基于FPGA内部SerDes资源可达到超高数据率、以及SerDes采样输出为较低速的FPGA可实时处理的并行数据这一特点,通过SerDes采样模块配合数据解码模块,使时间间隔测量范围提升至秒级。此外,利用SerDes采样接收模块中的高性能锁相环和移位寄存器统一的标准延时特点,使该TDC实现装置拥有更好的线性性能,同时省去了时钟多路相移方法中的复杂时钟电路,简化了FPGA外围电路设计、降低了FPGA所需IO口数量和系统复杂度,进而拓宽了其应用范围。技术研发人员:孔德轩,付在明,刘航麟,党浩烊受保护的技术使用者:电子科技大学技术研发日:技术公布日:2024/1/13本文地址:https://www.jishuxx.com/zhuanli/20240730/151810.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表