一种无失配高精度的多通道时间数字转换器

- 国知局

- 2024-07-30 10:14:19

本发明属于数字集成电路设计领域,具体涉及一种无失配高精度的多通道时间数字转换器。

背景技术:

1、时间数字转换器(tdc)是一种将时间信号量化为数字信号的器件,可以用来计算输入信号之间的相位差、周期等参数,被广泛应用于自动化测试设备(ate)、飞行时间测量、正电子成像技术、激光、雷达、示波器等技术领域。

2、常用的数字时间转换器的方法有多相位时钟测量法、抽头延迟链(tdl)法、游标法和脉冲收缩法等。抽头延迟链法结构简单,适用范围广,被广泛使用。一般的基于抽头延迟链法的tdc有三个基本单元:由延迟单元级联成的细计数器、按时钟周期计数的粗计数器和抽头采样及转换电路。在一般的tdl-tdc中,由于待测信号到达延迟链入口处的延迟与到粗计数器的路径延迟并不一致,当待测信号在时钟上升沿附近到来时,可能会出现粗细计数结果失配。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种无失配高精度的多通道时间数字转换器,通过改良粗细计数器的计数触发逻辑以解决粗细计数结果失配的问题。

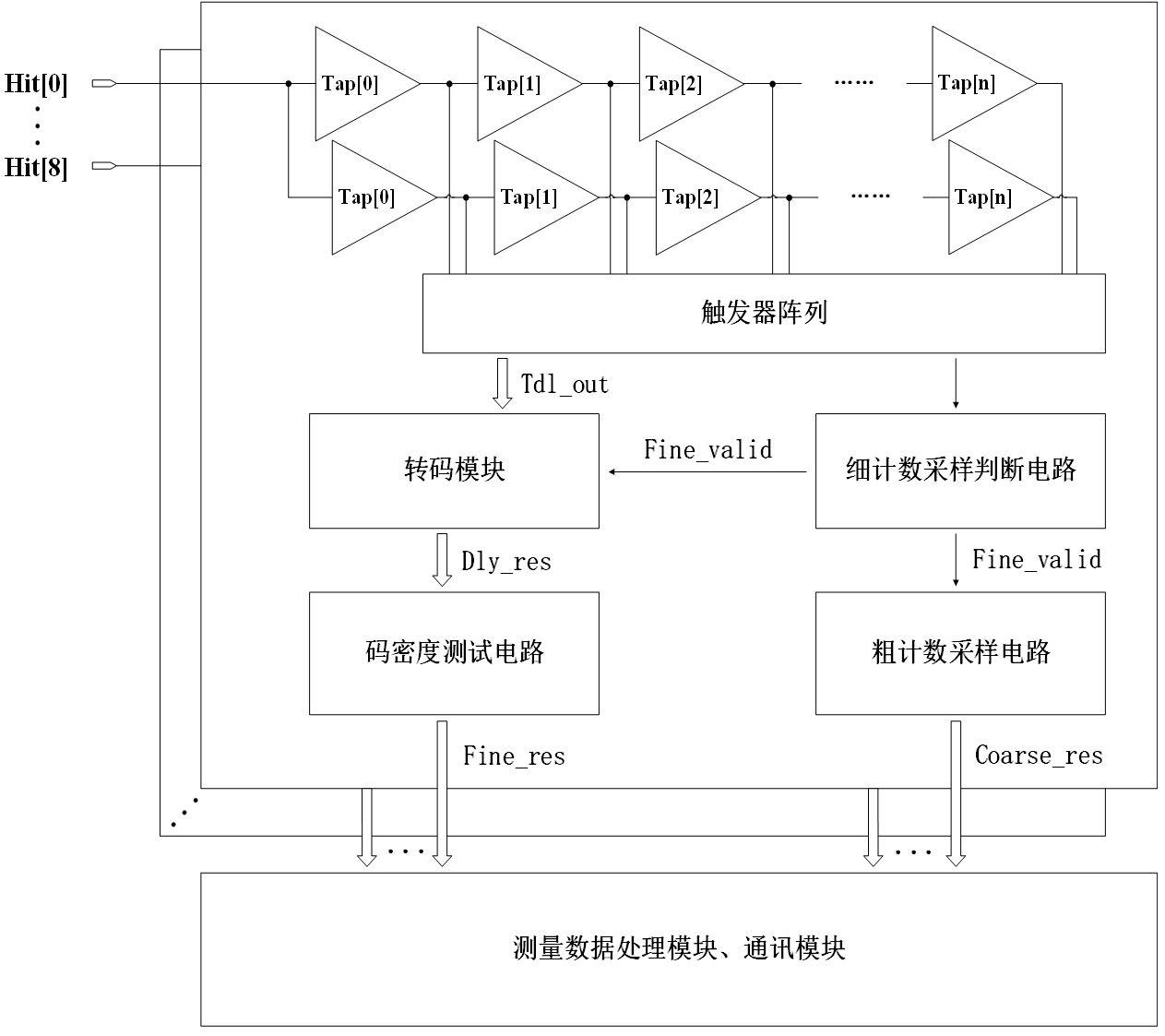

2、一种无失配高精度的多通道时间数字转换器,包括独立时间信号测量通道、粗计数器、测量数据处理模块、数据通讯模块;所述的独立时间信号测量通道具有多条,每条通道均包含抽头延迟链(tdl)、细计数采样判断电路、转码模块、粗计数采样电路、码密度测试电路;

3、所述的独立时间测量通道用于将连续的时间信号量化为数字信号,其可测范围超过系统时钟周期,可以与粗计数器共同构成一个两步式时间数字转换器,实现宽范围的高精度时间信号测量;

4、所述的转码模块用于将tdl中采样结果由温度计码转为二进制码;

5、所述的粗计数器用于按照系统时钟计数,每周期结果加一,粗计数结果接入前述独立时间信号测量通道中的粗计数采样电路;

6、所述的码密度测试电路用于对各独立测量通道在测量前进行码密度测试,以得到各通道每个抽头对应的延迟时间并将其建立为对应的查找表。在测量时间信号时,将所测得的tdl结果查表转换为对应细计数结果;

7、所述的测量数据处理模块位于每一条独立测量通道中,用于保存和计算每次的测量数据,并受控向数据通讯模块提供测量数据;

8、所述的数据通讯模块用于将码密度测试后得到的各抽头对应延迟时间、延迟链对齐操作后得到的各链基准延迟时间和对随机时间信号的测量结果发送到上位机。

9、所述的抽头延迟链由两条相同的延迟单元级联组合而成,分别为第一延迟单元级联链和第二延迟单元级联链,该两条级联链在物理布局上紧密排列,除最后一个延迟单元外的每个延迟单元输出分别接到下一个延迟单元的输入和一个最近的d触发器的数据输入端,最后一个延迟单元输出仅接到最近的d触发器的数据输入端;

10、所述的第一延迟单元级联链的每个延迟单元输出接入的d触发器组成第一触发器阵列,所述的第二延迟单元级联链的每个延迟单元输出接入的d触发器组成第二触发器阵列;

11、所述的第一触发器阵列和第二触发器阵列的每个触发器的输出接入到另一个最近的d触发器输入端,所述的第一触发器阵列的每个触发器输出接入的d触发器组成第三触发器阵列,所述的第二触发器阵列的每个触发器输出接入的d触发器组成第四触发器阵列;

12、所述的第一至第四触发器阵列的第8个触发器的输出被接入细计数采样判断电路。

13、所述的第一至第四触发器阵列的第8个触发器的输出被接入判断电路;其中,当第一触发器阵列的第8个触发器输出为高且第三触发器的第8个触发器输出为低,或者第二触发器阵列的第8个触发器输出为高且第四触发器的第8个触发器输出为低时,细计数采样有效信号fine_samp_valid置为高电平,表示采样有效。

14、所述的粗计数器,当时间数字转换器系统进入测量状态时,即开始按照系统时钟计数,每周期结果加一,计数值接入每条测量通道的粗计数采样电路中;当细计数采样有效信号fine_samp_valid跳变为高电平时,将该周期的粗计数值采样,并与细计数结果一同保存。

15、所述的测量数据处理模块,多条通道在多通道对齐环节保存每次各链的测量结果并计算,得到各链从信号源到延时链入口的路径延时差。

16、所述的无失配高精度的多通道时间数字转换器,无失配高精度的多通道时间数字转换,包括以下步骤:

17、步骤1、搭建无失配高精度的多通道时间数字转换器的电路;

18、步骤2、通过码密度测试的方法获得各链各抽头对应的延迟时间并存在ram中;

19、步骤3、通过同时向各链发送相同的上升沿脉冲hit_align_n并记录各链记录的结果,进行计算得到信号源到各测量通道的路径延迟差,并以此数据为基准校正后续所有测量结果;

20、步骤4、向测量通道发送上升沿脉冲信号hit_meas_n,触发细计数采样有效信号fine_samp_valid,将抽头延迟链上采样所得的结果输入码密度测试得到的结果查找表,输出对应的延迟时间,最后将查找表输出的延迟时间作为细计数结果与细计数采样有效信号置高时保存下的粗计数结果一并保存;

21、步骤5、将粗细计数结果发送到上位机,计算各通道记录下的各上升沿脉冲的上升沿位置可以得到需要测量的各种参数。

22、本发明的有益效果在于:

23、粗细计数触发中先检测细计数是否触发,只有细计数触发有效才保存粗计数值,有效避免粗细计数器失配。一般的tdl-tdc使用一条通道同时记录脉冲信号的上升沿和下降沿以计算脉冲宽度,本发明中由于一条通道只记录一次,故需要两条以上的通道配合测量待测信号的上升沿等的位置,进一步计算为各种待测参数,本发明中使用了多通道对齐操作以消除待测信号源到各通道路径延时差的影响,保证了多通道测量的高精度。

技术特征:1.一种无失配高精度的多通道时间数字转换器,其特征在于:包括独立时间信号测量通道、粗计数器、测量数据处理模块、数据通讯模块;所述的独立时间信号测量通道具有多条,每条通道均包含抽头延迟链(tdl)、细计数采样判断电路、转码模块、粗计数采样电路、码密度测试电路;

2.根据权利要求1所述的无失配高精度的多通道时间数字转换器,其特征在于:所述的抽头延迟链由两条相同的延迟单元级联组合而成,分别为第一延迟单元级联链和第二延迟单元级联链,该两条级联链在物理布局上紧密排列,除最后一个延迟单元外的每个延迟单元输出分别接到下一个延迟单元的输入和一个最近的d触发器的数据输入端,最后一个延迟单元输出仅接到最近的d触发器的数据输入端;

3.根据权利要求2所述的无失配高精度的多通道时间数字转换器,其特征在于:所述的第一至第四触发器阵列的第8个触发器的输出被接入判断电路;其中,当第一触发器阵列的第8个触发器输出为高且第三触发器的第8个触发器输出为低,或者第二触发器阵列的第8个触发器输出为高且第四触发器的第8个触发器输出为低时,细计数采样有效信号fine_samp_valid置为高电平,表示采样有效。

4.根据权利要求1所述的无失配高精度的多通道时间数字转换器,其特征在于:所述的粗计数器,当时间数字转换器系统进入测量状态时,即开始按照系统时钟计数,每周期结果加一,计数值接入每条测量通道的粗计数采样电路中;当细计数采样有效信号fine_samp_valid跳变为高电平时,将该周期的粗计数值采样,并与细计数结果一同保存。

5.根据权利要求1所述的无失配高精度的多通道时间数字转换器,其特征在于:所述的测量数据处理模块,多条通道在多通道对齐环节保存每次各链的测量结果并计算,得到各链从信号源到延时链入口的路径延时差。

6.根据权利要求1所述的无失配高精度的多通道时间数字转换器,其特征在于:无失配高精度的多通道时间数字转换,包括以下步骤:

技术总结本发明公开了一种无失配高精度的多通道时间数字转换器,包括独立时间信号测量通道、粗计数器、测量数据处理模块、数据通讯模块;所述的独立时间信号测量通道具有多条,每条通道均包含抽头延迟链(TDL)、细计数采样判断电路、转码模块、粗计数采样电路、码密度测试电路;所述的独立时间测量通道用于将连续的时间信号量化为数字信号,可测范围超过系统时钟周期,与粗计数器共同构成一个两步式时间数字转换器,实现宽范围的高精度时间信号测量。本发明结构简单,在保持高精度多通道测量能力的同时确保无失配。技术研发人员:梅雪笑,陈江华,郎晨晨,韩雁受保护的技术使用者:浙江大学技术研发日:技术公布日:2024/1/14本文地址:https://www.jishuxx.com/zhuanli/20240730/151980.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表