用于时间数字转换器的抽头延时线及其编码系统

- 国知局

- 2024-07-30 10:21:29

本发明涉及用于时间数字转换器的抽头延时线及其编码系统,属于时间数字转换器。

背景技术:

1、time-to-digital转换器(tdc)是一种时间间隔测量设备,可以测量与时间相关的间隔。随着核科学以及医学等领域的发展,对时间测量的要求日益上升,这促使时间-数字转换器(tdc)的设计技术得到了迅速发展。目前tdc的使用已经扩展到各种应用中,如正电子发射断层扫描(pet)、光探测和测距(lidar)、三维成像、时间间隔分析器、示波器、高能物理和空间探索等等。

2、tdc可以在特定应用集成电路(asic)或现场可编程门阵列(fpga)中实现。基于asic的tdc,其延迟线的基本延迟单元通常由组合逻辑门构成,其传播延迟由延迟锁定环(dlls)补偿,并可在工艺、电压和温度(pvt)变化期间稳定下来。基于asic的tdc的差分非线性(dnl)、积分非线性(inl)和环境变化阻力都很好,但对于小批量生产来说,成本特别高,需要专门设计实现,这增加了设计迭代周期,并降低了tdc在各种仪器配置中使用的灵活性。现场可编程门阵列(fpga)目前已经成为强大的数字处理平台,由于它具有高集成度、短开发周期和通用性强的特点,使得在fpga中实现高性能的tdc具有非常大的吸引力。

3、游标延迟线(vdl)和抽头延迟线(tdl)是数字tdc的主要架构。基于tdl的tdc具有更简单的结构,并且相比基于vdl的tdc具有更快的转换率,因此在最近的研究中更受欢迎。抽头延迟线通过在fpga的预设逻辑资源中级联进位逻辑(carry logic)来构建长运载链,用于时间插值。使要测量的信号沿着tdl传播,由系统时钟锁定的tdl状态为精细的时间戳,同时,由系统时钟锁定的粗略计数器的输出是粗时间戳。在时间插值机制下,tdc的测量精度主要由tdl中固有单元延迟的颗粒度和均匀性决定。由于fpga结构的缘故,从一个延时单元到下一个延时单元的延迟时间不是恒定的,而是变化很大,这种现象被称为不均匀的bin宽度,结果是导致了高dnl。由于工艺不一致和时钟偏移的影响,tdl采样出来的数据也并不是完美的温度计码,这种效应被称为气泡。它可以降低精度,并使编码器设计复杂化。

4、近年来,为克服tdc测量分辨率的限制,出现了两种解决方案:一种是wave union(波形联合)方法,也称为多边缘编码;另一种是使用多个tdl。wave union方法通过向tdl发射一系列的信号过渡边缘,记录一个命中信号的多个时间戳。这种多重测量相当于将tdl中的物理单元细分为多个小块,从而可以获得较高的时间精度。使用多个tdl的方法将多个传统tdl合并在一起,形成新的tdl,延时单元比原始传统tdl的物理延迟元素小得多。然后通过物理单元重新排序的方法提高tdl延时单元的均匀性,这样经过重新排序后的tdl就可以达到更高的时间精度。

5、但wave union方法仍然受到非温度计码现象的影响,导致时间测量精度降低,而使用多个tdl的方法,需要在实现tdl之前进行大量的数据测试,并且在tdl参数发生变化时需要重新对tdl进行实现,不能应对环境的变化且不便于移植。

技术实现思路

1、针对现有抽头延迟线的时间测量精度低的问题,本发明提供一种用于时间数字转换器的抽头延时线及其编码系统。

2、本发明的一种用于时间数字转换器的抽头延时线及其编码系统,包括m+1个可编程逻辑块clb0至clbm,m为正整数;

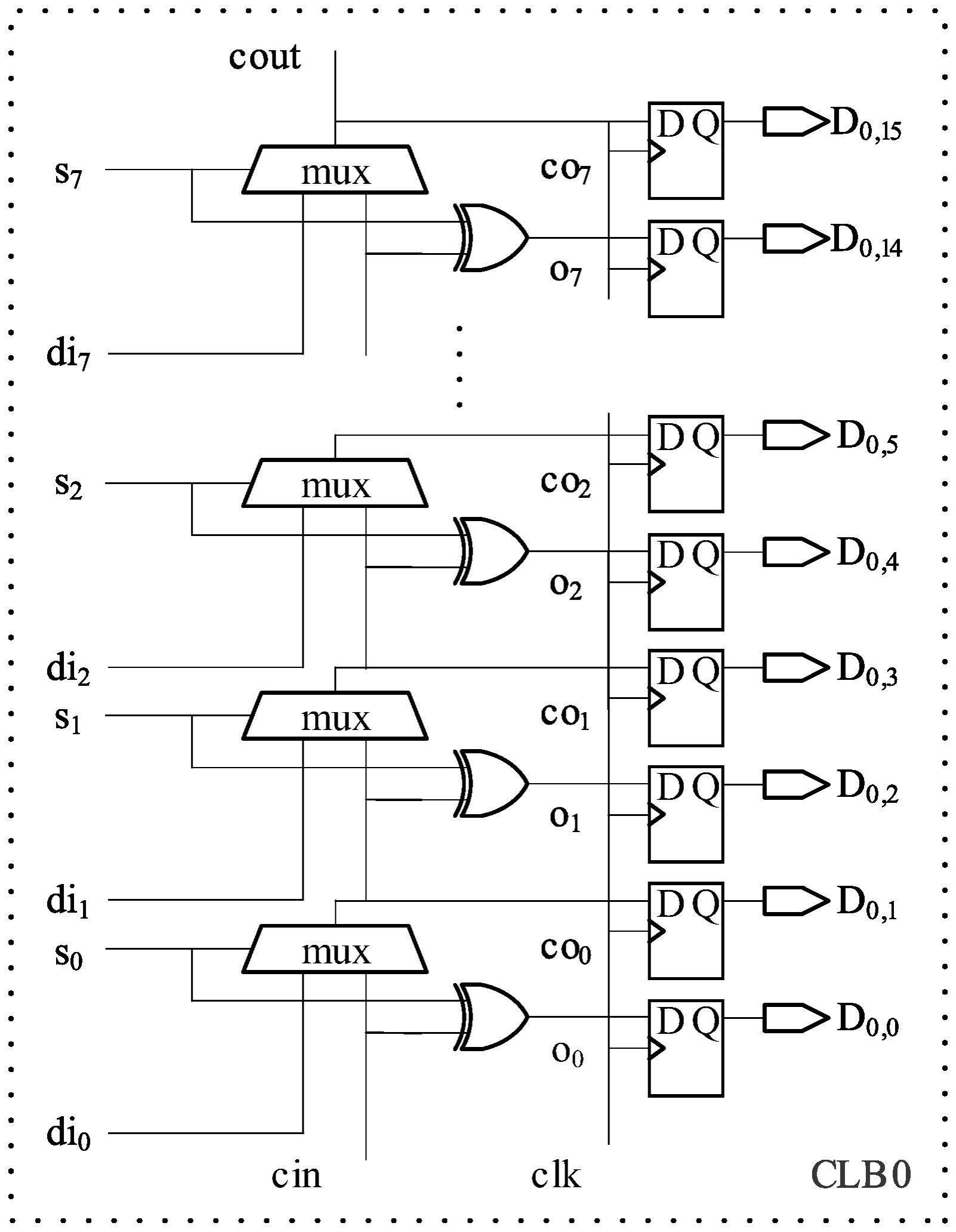

3、每个clb基于进位链carry8实现,包括8个加法器;每个加法器具有di输入端和s输入端,每个加法器的o抽头和co抽头对应连接到两个d触发器,通过d触发器输出采样信号;

4、m+1个可编程逻辑块顺次级联,相邻前一个clb的co7抽头连接相邻后一个clb的cin脚;

5、其中clb0的第一个加法器的输入端di0输入触发信号tri,输入端s0初始化为信号1;第二个加法器的输入端di1至第七个加法器的输入端di7均初始化为信号0,对应的输入端s1至s7均初始化为信号1;

6、clb1至clb3的初始化信号相同,每一个加法器的输入端di均初始化为信号0,每一个加法器的输入端s均初始化为信号1;

7、clb4的第一个加法器的输入端di0初始化为tri_n,tri_n与tri反向,输入端s0初始化为信号1;第二个加法器的输入端di1至第七个加法器的输入端di7均初始化为信号0,对应的输入端s1至s7均初始化为信号1;

8、clb5的8个加法器的输入端的初始化信号相同,每一个加法器的输入端di均初始化为信号0,每一个加法器的输入端s均初始化为信号1;

9、clb6的第一个加法器的输入端di0输入触发信号tri,输入端s0初始化为信号1;第二个加法器的输入端di1至第七个加法器的输入端di7均初始化为信号0,对应的输入端s1至s7均初始化为信号1;

10、clb7至clbm的初始化信号相同,每一个加法器的输入端di均初始化为信号0,每一个加法器的输入端s均初始化为信号1;

11、在初始阶段下,触发信号tri=0,tri_n=1,基于采样信号获得clb0至clbm输出的原始联合波形;

12、在触发阶段,当触发信号tri=1后,在最邻近的系统时钟上升沿时刻采样获得clb0至clbm输出的信号传播波形;根据所述信号传播波形确定触发信号tri=1时刻至所述系统时钟上升沿时刻之间的时长,作为触发信号tri传播对应的延时时间。

13、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,确定触发信号tri传播对应的延时时间的具体方法为:

14、在触发阶段,tri=1时,tri_n=0,在距离信号触发点最邻近的系统时钟上升沿时刻,基于采样信号获得clb0至clbm输出的信号传播波形,将信号传播波形中信号1的个数与原始联合波形中信号1的个数进行比较,将每个加法器作为一个延时单元,确定触发信号由起始时刻至系统时钟上升沿时刻所经过的延时单元的个数,根据每个延时单元的延时时间确定触发信号tri传播对应的延时时间。

15、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,信号传播波形中信号1的个数与原始联合波形中信号1的个数相减的结果,为触发信号由起始时刻至系统时钟上升沿时刻所经过的延时单元的个数。

16、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,信号传播波形中信号1的个数通过采用popcount算法计算信号1的个数的方法确定。

17、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,m为63。

18、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,将64个clb的co抽头信号和取反后的o抽头信号对应输入到64个dsp编码模块中;

19、首先将dsp编码模块配置为one48模式,使每个dsp编码模块首先并行进行8组1bit的加法运算,得到8个2bit的和;再进行4组2bit的加法运算,得到4个3bit的和;再进行2组3bit的加法运算,得到2个4bit的和;最后进行一组4bit的加法运算,得到5bit的16个抽头信号中1的个数的和;

20、然后将四个dsp编码模块组成一个dsp组;利用一个dsp组中每个dsp编码模块的7bit空位,分别将四个dsp编码模块得到的5bit的16个抽头信号中1的个数两两相加得到两个6bit的和;再将两个6bit的和相加得到一个7bit的16*4个抽头信号中1的个数的和;从而得到四个clb的co抽头信号1的个数和o抽头信号0的个数;

21、经计算,16个dsp组得到16个7bit的16*4个抽头信号中1的个数的和;

22、再选择两个dsp编码模块配置为two24模式;每个two24模式的dsp编码模块进行8个7bit的16*4个抽头信号中1的个数的并行相加,得到4个8bit的和;再将4个8bit的和两两并行相加,得到2个9bit的和;两个two24模式的dsp编码模块得到4个9bit的和;

23、最后选择一个dsp编码模块配置为two12模式,先进行4个9bit的和的两两并行相加,得到2个10bit的和,最后进行2个10bit的和的加法运算,得到信号传播波形中信号1的个数。

24、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,将信号传播波形中信号1的个数与原始联合波形中信号1的个数相减,得到延时单元的个数,从而得到距离信号触发点最邻近的系统时钟第一个上升沿所在点的位置编码。

25、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,根据系统时钟第一个上升沿所在点的位置编码,采用popcount算法得到第二个上升沿时刻所在区间的1的个数,得到第二个上升沿所在点的位置编码;将两个上升沿所在点的位置编码相加得到波形联合的最终编码,根据预先确定的编码与测量时间的对应关系得到最终编码对应的测量时间。

26、根据本发明的用于时间数字转换器的抽头延时线及其编码系统,系统时钟第二个上升沿时刻所在区间的确定方法为:

27、将信号传播波形中信号1的个数减去第一个上升沿和第一个下降沿之间设定的信号1的个数,得到第二个上升沿时刻对应的信号1的理想个数;根据信号1的理想个数确定对应的信号传播波形段,将所述信号传播波形段作为第二个上升沿时刻所在区间。

28、本发明的有益效果:本发明采用双采样方法并结合wave union对延时单元进行进一步细分,只采用一条tdl,对延时线的状态进行直接的popcount编码,忽略了非温度计码的影响;在tdl参数发生变化时可以不对tdl进行重新实现,只需要线上重新校准即可使用,可以比较方便的移植到其他平台,提高了时间测量的精度和效率。

本文地址:https://www.jishuxx.com/zhuanli/20240730/152409.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表