一种交织型高转换速率的时间数字转换器及转换方法

- 国知局

- 2024-07-30 10:30:54

本发明属于激光雷达,具体涉及一种交织型高转换速率的时间数字转换器及转换方法。

背景技术:

1、时间-数字转换器(time to digital converter,tdc)是用于测量时间间隔并将其转换为数字输出的装置。它允许以高分辨率测量非常短的时间。例如,tdc可以被用在飞行时间照相机中,以测量发射的光信号,如激光脉冲,行进至反射物体并且返回照相机所需的时间。

2、关于飞行时间测距法(time of flight,tof)飞行时间测量,时间数字转换器tdc在其中扮演着主要的角色,它的主要功能就是将待测的时间间隔转化成为数字信号通过计算得到该时间间隔,其本质就是多位计数器,但是其时间分辨率最小也是外部时钟clk的一个时钟周期,这样就不能满足测量比clk的一个时钟周期更短的时间间隔的需求,为了提高时间分辨,就增加了细计数模块,希望能测到更短的时间间隔,事实证明这样也是可行的。飞行时间测距法tof在现实生活中的应用很广泛,例如结合相机原理的tof_3d成像、材料物理中荧光材料的荧光时间的测量等。

3、近年来人们提出了一种激光雷达技术(direct time of flight,dtof),对于dtof激光雷达而言,时间数字转换器的分辨率决定了测量距离的分辨率,量化范围决定了测量距离的范围。此外,由于时间数字转换器存在死区时间,而且一般的时间数字转换器在一个激光发射周期内只能实现单次测量,这会使得dtof激光雷达系统的测量结果出现堆积失真效应,严重影响dtof激光雷达系统测量结果的准确度与可靠性。

4、因此,如何在兼顾时间数字转换器的分辨率与量化范围的同时,减少时间数字转换器的死区时间、提高时间数字转换器的转换速率、实现多事件检测功能是亟需解决的技术问题。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种交织型高转换速率的时间数字转换器及转换方法。本发明要解决的技术问题通过以下技术方案实现:

2、一种交织型高转换速率的时间数字转换器,包括:

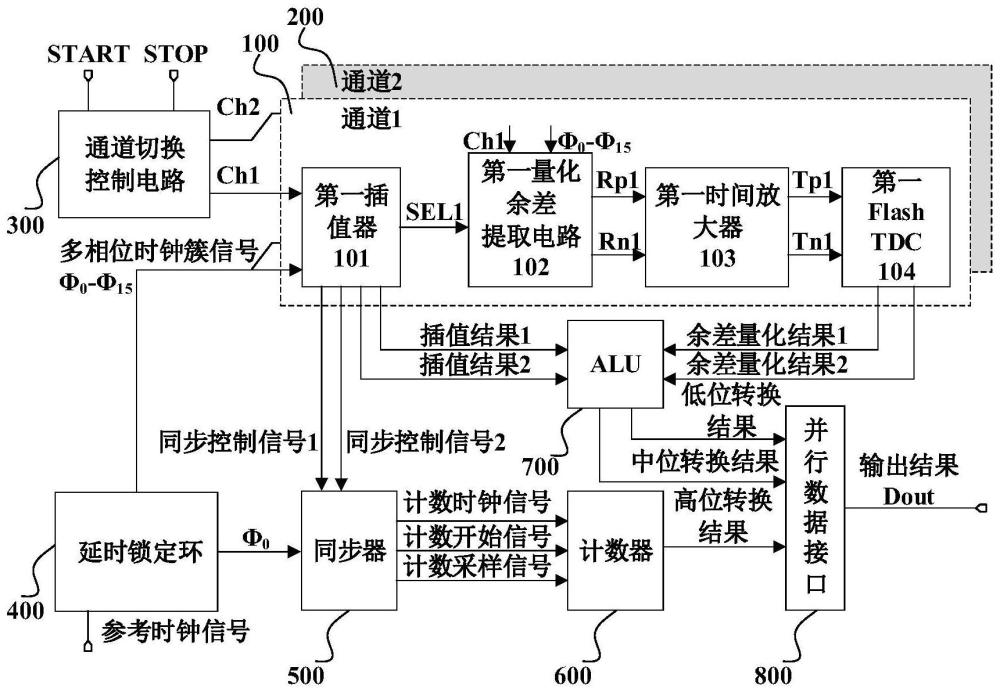

3、通道1、通道2、通道切换控制电路、延时锁定环、同步器、计数器、算术逻辑单元alu和并行数据接口;其中,

4、所述延时锁定环用于根据参考时钟信号生成间隔相等且频率相同的多相位时钟簇信号φ0-φ15,并发送至所述通道1和所述通道2;以及将所述多相位时钟簇信号φ0-φ15中的信号φ0发送至所述同步器;

5、所述通道切换控制电路用于将输入的start信号和stop信号进行交织分配,将交织分配后的ch1信号和ch2信号分别发送至所述通道1和所述通道2;

6、所述通道1采用插值结构,用于根据所述多相位时钟簇信号φ0-φ15和所述ch1信号,对所述start信号、所述stop信号和所述同步器产生的计数时钟信号之间的时间间隔采用两步法进行量化,输出同步控制信号1至所述同步器,输出插值结果1和余差量化结果1至所述算术逻辑单元alu;

7、所述通道2采用插值结构,用于根据所述多相位时钟簇信号φ0-φ15和所述ch2信号,对所述start信号、所述stop信号和所述计数时钟信号之间的时间间隔采用两步法进行量化,输出同步控制信号2至所述同步器,输出插值结果2和余差量化结果2至所述算术逻辑单元alu;

8、所述同步器用于根据所述信号φ0、所述同步控制信号1和所述同步控制信号2输出计数开始信号、计数采样信号和所述计数时钟信号至所述计数器;

9、所述计数器用于根据所述计数开始信号、所述计数采样信号和所述计数时钟信号,输出高位转换结果至所述并行数据接口;

10、所述算术逻辑单元alu用于对所述插值结果1、所述插值结果2、所述余差量化结果1和所述余差量化结果2进行运算,输出低位转换结果和中位转换结果至所述并行数据接口;

11、所述并行数据接口用于将所述高位转换结果、所述中位转换结果和所述低位转换结果进行整合,作为输出结果dout输出。

12、在本发明的一个实施例中,通道1和所述通道2的电路结构相同。

13、在本发明的一个实施例中,通道1的电路结构,包括:

14、第一插值器、第一量化余差提取电路、第一时间放大器和第一flash tdc;其中,

15、所述第一插值器的第一输入端接入所述多相位时钟簇信号φ0-φ15,所述第一插值器的第二输入端接入所述ch1信号,所述第一插值器的第一输出端与所述第一量化余差提取电路的第一输入端连接,所述第一插值器的第二输出端与所述同步器的第二输入端连接,所述第一插值器的第三输出端与所述算术逻辑单元alu的第一输入端连接;

16、所述第一量化余差提取电路的第二输入端接入所述ch1信号,所述第一量化余差提取电路的第三输入端接入所述多相位时钟簇信号φ0-φ15,所述第一量化余差提取电路的第一输出端与所述第一时间放大器的第一输入端连接,所述第一量化余差提取电路的第二输出端与所述第一时间放大器的第二输入端连接;

17、所述第一时间放大器的第一输出端与所述第一flash tdc的第一输入端连接,所述第一时间放大器的第二输出端与所述第一flash tdc的第二输入端连接;

18、所述第一flash tdc的输出端与所述算术逻辑单元alu的第三输入端连接。

19、在本发明的一个实施例中,通道2的电路结构,包括:

20、第二插值器、第二量化余差提取电路、第二时间放大器和第二flash tdc;其中,

21、所述第二插值器的第一输入端接入所述多相位时钟簇信号φ0-φ15,所述第二插值器的第二输入端接入所述ch2信号,所述第二插值器的第一输出端与所述第二量化余差提取电路的第一输入端连接,所述第二插值器的第二输出端与所述同步器的第三输入端连接,所述第二插值器的第三输出端与所述算术逻辑单元alu的第二输入端连接;

22、所述第二量化余差提取电路的第二输入端接入所述ch2信号,所述第二量化余差提取电路的第三输入端接入所述多相位时钟簇信号φ0-φ15,所述第二量化余差提取电路的第一输出端与所述第二时间放大器的第一输入端连接,所述第二量化余差提取电路的第二输出端与所述第二时间放大器的第二输入端连接;

23、所述第二时间放大器的第一输出端与所述第二flash tdc的第一输入端连接,所述第二时间放大器的第二输出端与所述第二flash tdc的第二输入端连接;

24、所述第二flash tdc的输出端与所述算术逻辑单元alu的第四输入端连接。

25、在本发明的一个实施例中,针对所述通道1或所述通道2,采用两步法进行量化的过程,包括:

26、根据自身接收到的信号利用插值器输出同步控制信号至所述同步器,利用所述插值器对自身接收到的信号进行插值,得到对应的插值结果;

27、利用量化余差提取电路对所述插值器的量化余差进行提取;

28、利用时间放大器对所述量化余差提取电路的提取结果进行放大;

29、利用flash tdc对所述时间放大器的放大结果进行量化,得到余差量化结果。

30、在本发明的一个实施例中,所述第一时间放大器和所述第二时间放大器中任意一个的电路结构,包括:

31、时间放大器控制逻辑、电容ca、电容cb、s1a信号控制的开关、s2a信号控制的开关、s3a信号控制的开关、s4a信号控制的开关、s1b信号控制的开关、s2b信号控制的开关、s3b信号控制的开关、s4b信号控制的开关、电流源ifa、电流源isa、电流源ifb、电流源isb、比较器a和比较器b;其中,

32、所述时间放大器控制逻辑的第一输入端作为时间放大器的第一输入端,所述时间放大器控制逻辑的第二输入端作为所述时间放大器的第二输入端,所述时间放大器控制逻辑的第一输出端与所述s1a信号控制的开关的控制端连接,所述时间放大器控制逻辑的第二输出端与所述s2a信号控制的开关的控制端连接,所述时间放大器控制逻辑的第三输出端与所述s3a信号控制的开关的控制端连接,所述时间放大器控制逻辑的第四输出端与所述s4a信号控制的开关的控制端连接,所述时间放大器控制逻辑的第五输出端与所述s1b信号控制的开关的控制端连接,所述时间放大器控制逻辑的第六输出端与所述s2b信号控制的开关的控制端连接,所述时间放大器控制逻辑的第七输出端与所述s3b信号控制的开关的控制端连接,所述时间放大器控制逻辑的第八输出端与所述s4b信号控制的开关的控制端连接;

33、所述电容ca的第一端与所述s4a信号控制的开关的第一端连接,所述电容ca的第二端接地;

34、所述电容cb的第一段与所述s4b信号控制的开关的第一端连接,所述电容cb的第二端接地;

35、所述s1a信号控制的开关的第一端与所述s2a信号控制的开关的第二端连接,所述s1a信号控制的开关的第二端与所述电流源ifa的第一端连接;

36、所述s2a信号控制的开关的第一端接地;

37、所述s3a信号控制的开关的第一端接地,所述s3a信号控制的开关的第二端与所述电流源isa的第一端连接;

38、所述s4a信号控制的开关的第一端与所述电流源isa的第二端连接,所述s4a信号控制的开关的第二端接入vdd;

39、所述电流源ifa的第二端与所述比较器a的负向输入端连接;

40、所述电流源isa的第二端与所述电流源ifa的第二端连接;

41、所述s1b信号控制的开关的第一端与所述s2b信号控制的开关的第二端连接,所述s1b信号控制的开关的第二段与所述电流源ifb的第一端连接;

42、所述s2b信号控制的开关的第一端接地;

43、所述s3b信号控制的开关的第一端接地,所述s3b信号控制的开关的第二端与所述电流源isb的第一端连接;

44、所述s4b信号控制的开关的第一端与所述电流源isb的第二端连接,所述s4b信号控制的开关的第二端接入所述vdd;

45、所述电流源isb的第二端与所述电流源ifb的第二端连接;

46、所述电流源ifb的第一端与所述比较器b的负向输入端连接;

47、所述比较器a的正向输入端与所述比较器b的正向输入端连接,并接入参考电压vref,所述比较器a的输出端作为所述时间放大器的第一输出端;所述比较器b的输出端作为所述时间放大器的第二输出端。

48、在本发明的一个实施例中,电流源ifa的输出电流ifa与所述电流源ifb的输出电流ifb都等于if;所述电流源isa的输出电流isa与所述电流源isb的输出电流isb都等于is。

49、在本发明的一个实施例中,第一时间放大器和第二时间放大器中任意一个的放大倍数为at;其中,at=if/is。

50、一种交织型高转换速率的时间数字转换方法,基于权利要求1至8中任一项所述的交织型高转换速率的时间数字转换器实现,所述时间数字转换方法包括:

51、获取参考时钟信号,以所述参考时钟信号为基准,生成间隔相等且频率相同的多相位时钟簇信号φ0-φ15;

52、获取start信号和stop信号,将所述start信号和所述stop信号分配至通道1、通道2;

53、采用两步法对所述通道1和所述通道2收到的信号进行量化,得到插值结果1、插值结果2、余差量化结果1和余差量化结果2;

54、对所述插值结果1、所述插值结果2、所述余差量化结果1和所述余差量化结果2进行计算,得到中位转换结果和低位转换结果;

55、对所述start信号、所述stop信号和所述多相位时钟簇信号φ0-φ15中的信号φ0进行同步处理,得到计数时钟信号、计数开始信号和计数采样信号;

56、根据所述计数时钟信号、所述计数开始信号和所述计数采样信号,得到高位转换结果;

57、对所述高位转换结果、所述中位转换结果和所述低位转换结果进行整合,得到表示所述start信号和所述stop信号之间时间间隔的数字码作为输出结果dout输出。

58、本发明的有益效果:

59、本发明实施例所提供的方案中,对两个通道都采用插值结构,兼顾了时间数字转换器的分辨率和量化范围;通过引入同步器保证了高位转换结果、中位转换结果和低位转换结果之间的匹配,提高了转换精度;借助通道切换控制电路将start信号和stop信号交织分配至通道1和通道2,将空闲的通道利用起来,提高了资源利用率,减少时间数字转换器的死区时间,同时有效提高了时间数字转换器的转换速率,并且实现了多事件检测。

本文地址:https://www.jishuxx.com/zhuanli/20240730/153163.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表