时间间隔测量方法、时间数字转换器及FPGA与流程

- 国知局

- 2024-07-30 10:33:22

本发明涉及测时领域,具体而言,涉及一种时间间隔测量方法、时间数字转换器及fpga。

背景技术:

1、在许多应用领域中,需要对时间间隔进行高精度的数字转换。不同的研究者在fpga上实现了不同的时间插值方法,以提高时间分辨率。时间数字转换器tdc的主要任务是对同时发生的事件之间的时间延迟进行高分辨率测量,同时需要高吞吐量以处理并行探测器模块的大量测量。

2、传统的tdc技术可以使用抽头延迟线(tdl)的方式进行测量,抽头延迟线通过进位传播延时来估计延迟线的长度,进而获得分辨率。然而传统方案中存在的一个问题是死区时间较长,需要两个时钟周期来重置延迟线,较长的死区时间会导致tdc的测量速率降低,会降低tdc的测量精度,特别是在需要高速连续测量的应用场景中,可能会导致数据丢失或测量不准确。

3、针对上述的问题,目前尚未提出有效的解决方案。

技术实现思路

1、本发明实施例提供了一种时间间隔测量方法、时间数字转换器及fpga,以至少解决时间数字转换器的死区时间过长导致时间精度不高的技术问题。

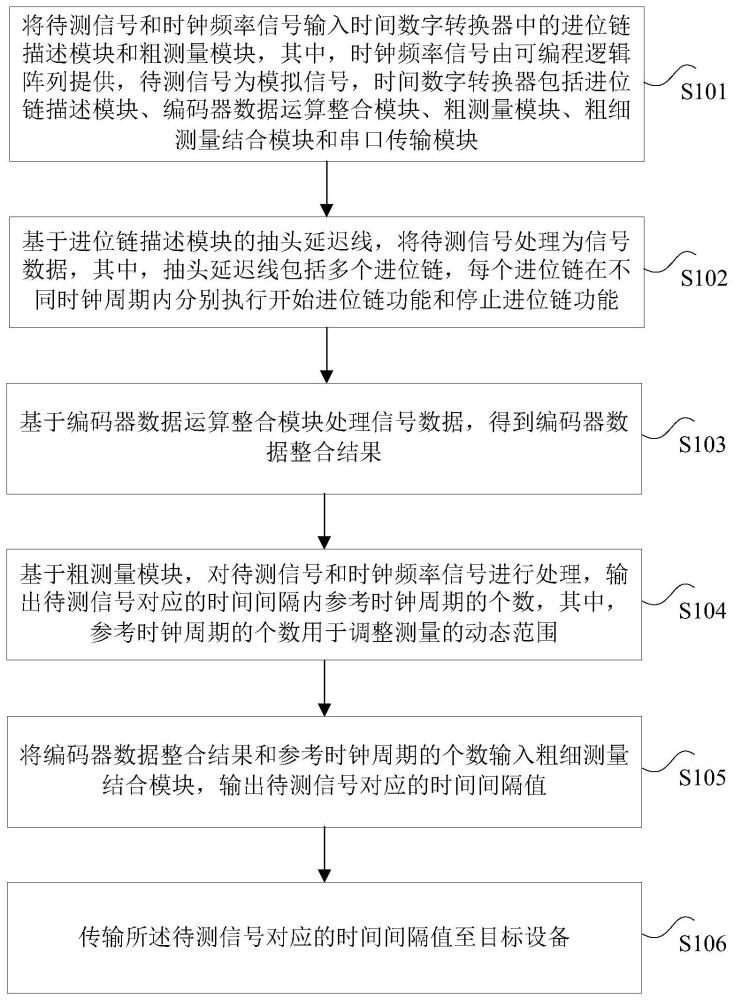

2、根据本发明实施例的一个方面,提供了一种时间间隔测量方法,包括:将待测信号和时钟频率信号输入时间数字转换器中的进位链描述模块和粗测量模块,其中,所述时钟频率信号由可编程逻辑阵列提供,所述待测信号为模拟信号,所述时间数字转换器包括所述进位链描述模块、编码器数据运算整合模块、粗细测量结合模块、粗测量模块、粗细测量结合模块和串口传输模块;基于所述进位链描述模块的抽头延迟线,将所述待测信号处理为信号数据,其中,所述抽头延迟线包括多个进位链,每个所述进位链在不同时钟周期内分别执行开始进位链功能和停止进位链功能;基于所述编码器数据运算整合模块处理所述信号数据,得到编码器数据整合结果;基于所述粗测量模块,对所述待测信号和所述时钟频率信号进行处理,输出所述待测信号对应的时间间隔内参考时钟周期的个数,其中,所述参考时钟周期的个数用于调整测量的动态范围;将所述编码器数据整合结果输入所述粗细测量结合模块,输出所述待测信号对应的时间间隔值;基于所述串口传输模块,传输所述待测信号对应的时间间隔值至目标设备。

3、可选地,在所述进位链描述模块还包括双模式组合计数器的情况下,所述方法还包括:在相邻时钟周期内,切换所述抽头延迟线的输入级,使得所述抽头延迟线在所述相邻时钟周期中分别从双模式组合计数器编码器中接收到不同的电平信号,其中,所述电平信号包括高电平和低电平,所述双模式组合计数器包括第一模式和第二模式;在所述第一模式下,所述双模式组合计数器输出的高电平指示所述进位链执行开始进位链功能,所述双模式组合计数器输出的低电平指示所述进位链执行停止进位链功能;在所述第二模式下,所述双模式组合计数器输出的低电平指示所述进位链执行开始进位链功能,所述双模式组合计数器输出的高电平指示所述进位链执行停止进位链功能;通过所述抽头延迟线的输入级,从所述双模式组合计数器中接收所述电平信号,并根据所述电平信号控制所述多个进位链执行开始进位链功能或执行停止进位链功能。

4、可选地,所述方法还包括:在每个所述进位链包括主分支和子分支的情况下,确定每个所述进位链对应的输出结果差异,所述输出结果差异为对应的进位链的主分支和子分支之间的输出结果差异;确定所述输出结果差异的平均值;根据所述平均值,校正所述时间数字转换器的非线性误差。

5、可选地,所述方法还包括:根据校准判决逻辑,对所述编码器数据运算整合模块包括的多组冗余测时链路中的回波通道的输出结果进行判读,其中,每组所述多组冗余测时链路包括一个主波通道和偶数个回波通道,所述偶数个回波通道中一半回波通道位于对应的主波通道的左侧,另一半回波通道位于对应的主波通道的右侧,所述校准判决逻辑包括:对所述多组冗余测时链路中的回波通道进行回波入波门判读,去除波门外的非合理测时值,根据所述多组冗余测时链路的优先级输出每组冗余测时链路对应的合理测时值;其中,在每组冗余测时链路的所述回波通道的输出结果中至少有两个合理测时值的情况下,按照预设的回波通道优先级输出该组冗余测时链路的合理测时值。

6、可选地,将所述编码器数据整合结果和所述参考时钟周期的个数输入所述粗细测量结合模块,输出所述待测信号对应的时间间隔值,包括:将所述编码器数据整合结果输入所述粗细测量结合模块中的细测量单元,得到所述待测信号对应的细测量时间间隔值,其中,所述细测量单元包括由多个carry4单元级联而成的延迟链;所述粗细测量结合模块根据所述参考时钟周期的个数,判断所述待测信号的时间间隔是否大于预设时间间隔阈值;在所述待测信号的时间间隔大于所述预设时间间隔阈值的情况下,将所述参考时钟周期的个数作为所述待测信号对应的时间间隔值进行输出;在所述待测信号的时间间隔小于等于所述预设时间间隔阈值的情况下,将所述细测量时间间隔值作为所述待测信号对应的时间间隔值进行输出。

7、可选地,所述将所述编码器数据整合结果输入所述粗细测量结合模块中的细测量单元,得到所述待测信号对应的细测量时间间隔值,包括:所述细测量单元采用分段延迟线技术,在停止信号的上升沿预设的偏离时间点处对所述延迟链的状态进行采样,得到采样结果;分析所述停止信号在所述延迟链上的采样结果,计算出启动信号与所述停止信号之间的时间差,得到所述细测量时间间隔值。

8、根据本发明实施例的另一方面,还提供了一种时间数字转换器,包括:进位链描述模块,用于接收待测信号和时钟频率信号,其中,所述时钟频率信号由可编程逻辑阵列提供,所述待测信号为模拟信号;所述进位链描述模块,还用于基于抽头延迟线将所述待测信号处理为信号数据,其中,所述抽头延迟线包括多个进位链,每个所述进位链在不同时钟周期内分别执行开始进位链功能和停止进位链功能;粗测量模块,用于接收所述待测信号和所述时钟频率信号,还用于对所述待测信号和所述时钟频率信号进行处理,输出所述待测信号对应的时间间隔内参考时钟周期的个数,所述参考时钟周期的个数用于调整测量的动态范围;编码器数据运算整合模块,用于处理所述信号数据,得到编码器数据整合结果;粗细测量结合模块,用于接收所述编码器数据整合结果和所述参考时钟周期的个数,输出所述待测信号对应的时间间隔值;串口传输模块,用于传输所述待测信号对应的时间间隔值至目标设备。

9、根据本发明实施例的另一方面,还提供了一种现场可编程门阵列,所述现场可编程门阵列包括上述时间数字转换器。

10、根据本发明实施例的又一方面,还提供了一种非易失性存储介质,所述非易失性存储介质包括存储的程序,其中,在所述程序运行时控制所述非易失性存储介质所在设备执行上述任意一项所述时间间隔测量方法。

11、根据本发明实施例的再一方面,还提供了一种计算机设备,所述计算机设备包括存储器和处理器,所述存储器用于存储程序,所述处理器用于运行所述存储器存储的程序,其中,所述程序运行时执行上述任意一项所述时间间隔测量方法。

12、根据本发明实施例的再一方面,还提供了一种计算机程序产品,包括计算机程序,其特征在于,所述计算机程序被处理器执行时实现上述任意一项所述时间间隔测量方法的步骤。

13、在本发明实施例中,采用在进位链描述模块中将开始进位链和停止进位链进行功能二合一的方式,控制每条进位链在不同时钟周期内交替发挥开始进位链功能和结束进位链功能,达到了将时间数字转换器的死区时间降低到一个时钟周期的目的,从而实现了提高时间数字转换器测量效率的技术效果,进而解决了时间数字转换器的死区时间过长导致时间精度不高的技术问题。

本文地址:https://www.jishuxx.com/zhuanli/20240730/153393.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。