一种高精度时间数字转换器芯片

- 国知局

- 2024-07-30 10:36:37

本发明涉及时间测量计数,具体涉及一种高精度时间数字转换器芯片。

背景技术:

1、时间数字转换器(tdc),是一种将信号的时间信息转换为数字信息并输出的器件,可以精确测量事件之间的时间差、脉冲宽度、相位差等时间相关参数,适用于粒子物理实验、雷达探测、生物医学成像等各种需要精确测量时间事件的场合。在粒子物理实验中,单个粒子在探测区域被探测器捕捉后会产生一个有效脉冲,这样使用多个探测器和时间转换器测量脉冲的间隔时间,就可以得到粒子的发射频率和分布数据。在生物医学领域,时间数字转换器在飞行时间探测中得到了广泛应用。飞行时间技术采用单一调制的红外光源照射目标物体,通过捕捉反射光获取所需的数据,而时间数字转换器可以精确测量从光源发射到反射光被接收的时间差,最终生成高度可靠的距离图像。

2、时间数字转换器有两种主流的做法,一种是基于现场可编程门阵列(fieldprogrammable gate array,fpga)的时间数字转换器,一种是全定制时间数字转换器芯片,前者依赖于高性能的fpga,有研发成本低、可重复设计和周期短的特点,而全定制的时间数字转换器芯片需要从晶体管级构筑起整个电路,不断用仿真工具验证功能和评估性能,最后还需要考虑紧密合理的版图设计,虽然制作周期长,但是可以实现更低的功耗、更轻量的大小和更高的精度。目前国内在全定制时间数字转换器芯片的设计中还缺乏一定的经验,在精度、功耗和量程等指标上还有提升空间。

3、全定制时间数字转换器芯片的常见设计方法可以分为基于延时链的时间数字转换器和基于环形振荡器的时间数字转换器。基于延时链的时间数字转换器的基本原理是让时间起始信号start进入多个延时单元组成的链状电路中,转化为若干个具有延时梯度的信号,然后时间终止信号stop通过仲裁器链对这些信号进行时间甄别,最终d触发器输出的数据就可以表达出时间终止信号stop相对于时间起始信号start的相位信息,从而完成了时间信息到数字信息的转换。基于延时链的时间数字转换器中为了突破工艺尺寸的限制,往往会采用游标型的结构,即让stop信号也通入延时链中,这样两条延时链的两组信号就形成了互相追赶的情况,从而实现更小的精度测量。但是游标链结构会增加功耗,对电源和其他形式的噪声极为敏感,量程也会受到很大的限制。因此,如何研制出高精度、宽量程的全定制时间数字转换器芯片是本领域技术人员需要解决的技术问题。

技术实现思路

1、为解决上述技术问题,本发明提供一种高精度时间数字转换器芯片,它不仅突破工艺限制达到了很高的精度,还保持了较宽量程的特性;此外,通过后期的校准,可进一步提升tdc的线性度和精度。

2、为解决上述技术问题,本发明采用如下技术方案:

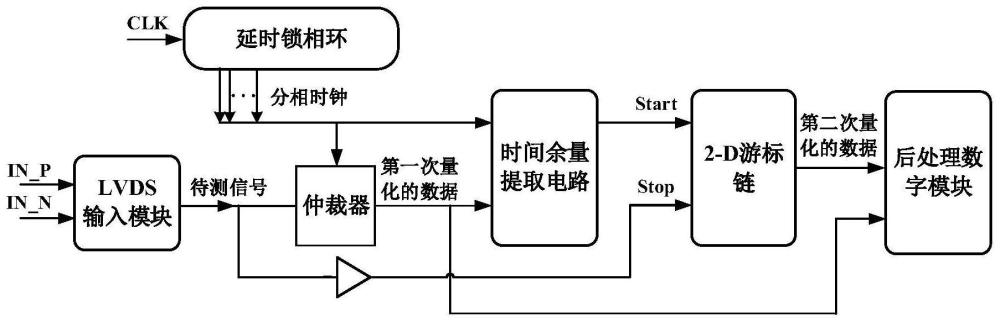

3、一种高精度时间数字转换器芯片,用于对待测信号进行量化和校准,输出量化数据;包括:

4、延时锁相环,时钟信号输入到延时锁相环,得到多个分相时钟;

5、仲裁器,待测信号和分相时钟输入到仲裁器进行第一段时间测量,得到第一次量化数据;

6、时间余量提取电路,将第一次量化数据和分相时钟输入到时间余量提取电路,将第一段时间测量中未能测量到的时间剩余部分提取出来,得到输入到第二段时间测量所需的时间开始信号start;

7、游标链,将待测信号经过固定延迟后,得到输入到第二段时间测量所需的时间结束信号stop;将时间开始信号start和时间结束信号stop输入到游标链,进行第二段时间测量,时间开始信号start和时间停止信号stop分别进入两条不同延迟的延时链,并通过校准模块处理不同延时链间的失配,得到的第二量化数据即为时间数字转换器芯片输出的量化数据。

8、进一步地,所述游标链为2-d游标链。

9、进一步地,所述延时锁相环包括鉴频鉴相器、电荷泵、线性滤波器、偏置模块和第一延时链;

10、时钟信号分别输入到鉴频鉴相器和第一延时链;鉴频鉴相器的输出与电荷泵的输入连接,电荷泵的输出与线性滤波器的输入连接,线性滤波器的输出与偏置模块的输入连接;第一延时链包括n个延时单元;偏置模块的输出与各个延时单元的偏置输入端连接;每个延时单元输出一个时钟信号,得到n个分相时钟;将第一延时链末端的输出,输入到鉴频鉴相器。

11、进一步地,所述分相时钟有n个;所述仲裁器包括两个d触发器链,分别为第一d触发器链和第二d触发器链;第一d触发器链包括n个第一d触发器,第二d触发器链包括n个第二d触发器;n个分相时钟分别输入到n个第一d触发器的数据输入端口,待测信号输入到各个第一d触发器的时钟信号输入端口;n个第一d触发器的数据输出端口分别与n个第二d触发器的数据输入端口连接,将待测信号经过固定延迟后输入到各个第二d触发器的时钟信号输入端口,第二d触发器的数据输出端口中输出所述的第一次量化数据,第一次量化数据为n位的数据,记为dff<n:1>。

12、进一步地,所述时间余量提取电路包括n个三输入与非门,以及个1级与非门、个2级或非门、个3级与非门、个4级或非门、……、个2n-1级与非门、个2n级或非门;n≥3,且22n=n;

13、或者,所述时间余量提取电路包括n个三输入与非门,以及个1级与非门、个2级或非门、个3级与非门、个4级或非门、……、个2n-1级与非门、个2n级或非门、个2n+1级与非门;n≥3,且22n+1=n;

14、n个三输入与非门的输出两两结合作为个1级与非门的输入;上一级与非门的输出两两结合,作为下一级或非门的输入,上一级或非门的输出两两结合,作为下一级与非门的输入,直至只剩下一个输出,作为整个时间余量提取电路的输出;

15、三输入与非门的输入包括第i个分相时钟clk<i>、第i-1位的第一次量化数据dff<i-1>,以及第i位的第一次量化数据dff<i>经过反相器后得到的数据。

16、上述n也可以修改为m,n和m可以相等也可以不相等,m是2的平方数,n要满足n<=m。

17、进一步地,所述游标链包括两个具有不同延迟的延时链,以及两个校准模块;两个延时链分别记为第一延时链和第二延时链,两个校准模块分别记为第一校准模块和第二校准模块;时间开始信号start进入第二延时链,时间停止信号stop进入第一延时链;第一校准模块的输入与第一控制电压vctrl1连接,输出与第一延时链中各个延时单元的偏置输入端连接;第二校准模块的输入与第二控制电压vctrl2连接,输出与第二延时链中各个延时单元的偏置输入端连接。

18、进一步地,所述校准模块包括偏置部分和校准部分;

19、第一控制电压vctrl1和第二控制电压vctrl2统称为控制电压vctrl;

20、偏置部分包括pmos管pm1、pm2、pm3和pm4,以及nmos管nm1、nm2、nm3和nm4;

21、pmos管pm1的源极与工作电压vdd连接、栅极输入偏置电压biasn并与nmos管nm4的栅极连接、漏极与pmos管pm2的源极连接;

22、pmos管pm2的栅极与接地端电压vss连接、漏极与nmos管nm1的漏极连接;

23、pmos管pm3的源极与工作电压vdd连接、栅极输入偏置电压biasp、漏极与pmos管pm4的源极连接;

24、pmos管pm4的栅极与接地端电压vss连接、漏极与nmos管nm3的漏极连接;

25、nmos管nm1的栅极与工作电压vdd连接、源极与nmos管nm2的漏极连接;nmos管nm2的栅极与控制电压vctrl连接、源极与接地端电压vss连接;

26、nmos管nm3的栅极与工作电压vdd连接、源极与nmos管nm4的漏极连接;nmos管nm4的源极与接地端电压vss连接;

27、校准部分包括pmos管pm5、pm6、pm7、pm8和pm9,以及nmos管nm5、nm6、nm7、nm8和nm9;

28、pmos管pm5、pm6、pm7、pm8和pm9的源极均与工作电压vdd连接,栅极分别与第一位pmos管数字控制字dcw<1>、第二位pmos管数字控制字dcw<2>、第三位pmos管数字控制字dcw<3>、第四位pmos管数字控制字dcw<5>、第五位pmos管数字控制字dcw<5>连接,漏极均与偏置电压biasp连接;pmos管pm5、pm6、pm7、pm8和pm9的宽度均为wp,长度分别为16lp、8lp、4lp、2lp、lp;

29、nmos管nm5、nm6、nm7、nm8和nm9的源极均与接地端电压vss连接,栅极分别与第一位nmos管数字控制字n_dcw<1>、第二位nmos管数字控制字n_dcw<2>、第三位nmos管数字控制字n_dcw<3>、第四位nmos管数字控制字n_dcw<5>、第五位nmos管数字控制字n_dcw<5>连接,漏极均与偏置电压biasp连接;nmos管nm5、nm6、nm7、nm8和nm9的宽度均为wn,长度分别为16ln、8ln、4ln、2ln、ln。

30、与现有技术相比,本发明的有益技术效果是:

31、本发明是一种通用型时间数字转换器,采用了两段量化的方法,很好地结合了每段量化的优势,在高精度的同时保留了较高的动态测量范围,也减少了设计的复杂度。

32、本发明使用了2-d游标型结构的时间数字转换器,可以在不增长延时链的情况下扩大第二段量化的动态范围,减少了功耗和面积,同时在一定程度上缓解了前一段量化中亚稳态问题的影响。

33、本发明采用的时间余量提取电路,可以准确地将第一段量化剩余的时间信息传递到下一段量化中,并且采用了跳级提取的方法,缓解了由于路径延迟和建立时间引起的时序紧张的问题。

34、本发明在游标链的延时链中额外引入了校准模块,有效解决了版图误差导致的延时链失配问题,它可以在外部实现对延时链的延时进行微小调节,再通过测量的结果反推出需要调整的参数,让时间数字转换器达到更良好的精度。

本文地址:https://www.jishuxx.com/zhuanli/20240730/153519.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表