一种基于3DIC设计的高速电路性能评估方法及系统与流程

- 国知局

- 2024-07-31 22:44:49

本发明涉及高速电路,特别涉及一种基于3dic设计的高速电路性能评估方法及系统。

背景技术:

1、随着电子设备的不断发展,高速电路设计变得越来越复杂,而信号串扰问题也变得日益突出。传统的电路设计方法往往难以有效评估和解决信号串扰所带来的性能影响,导致设计的不稳定性和可靠性问题。

2、针对这一挑战,近年来出现了基于3dic设计的高速电路设计方法,通过在垂直方向上堆叠芯片以实现更高的集成度和更短的互连路径,从而提高电路性能。然而,3dic设计也带来了新的挑战,如层间串扰、热耦合等问题,需要针对性的评估和优化。

3、目前,虽然存在一些针对电路性能评估的方法,但大多数仍采用传统的二维设计思路,无法充分考虑3dic设计的特点和问题。因此,需要一种新的评估方法,能够结合3dic设计的特点,对高速电路的性能进行全面评估和优化。

4、因此,本领域的相关技术主要包括高速电路设计、信号传输分析、串扰效应模拟等。然而,现有方法往往局限于单一方面的评估,无法全面考虑3dic设计的复杂性和多样性,因此需要一种更全面、更深入的高速电路性能评估方法。

技术实现思路

1、为了解决上述至少一个技术问题,本发明提出了一种基于3dic设计的高速电路性能评估方法及系统。

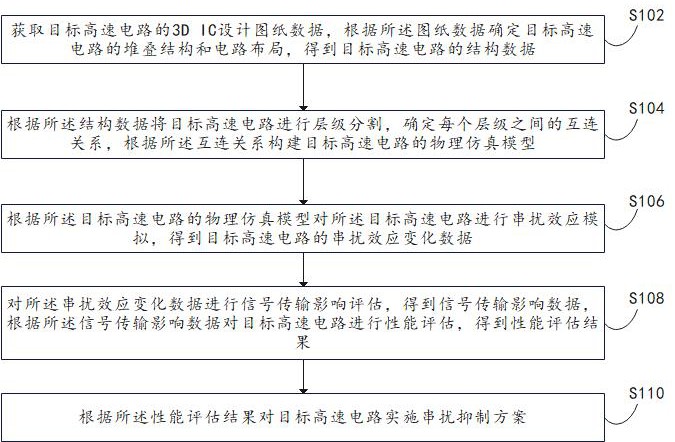

2、本发明第一方面提供了一种基于3dic设计的高速电路性能评估方法,包括:

3、获取目标高速电路的3dic设计图纸数据,根据所述图纸数据确定目标高速电路的堆叠结构和电路布局,得到目标高速电路的结构数据;

4、根据所述结构数据将目标高速电路进行层级分割,确定每个层级之间的互连关系,根据所述互连关系构建目标高速电路的物理仿真模型;

5、根据所述目标高速电路的物理仿真模型对所述目标高速电路进行串扰效应模拟,得到目标高速电路的串扰效应变化数据;

6、对所述串扰效应变化数据进行信号传输影响评估,得到信号传输影响数据,根据所述信号传输影响数据对目标高速电路进行性能评估,得到性能评估结果;

7、根据所述性能评估结果对目标高速电路实施串扰抑制方案。

8、本方案中,所述获取目标高速电路的3dic设计图纸数据,根据所述图纸数据确定目标高速电路的堆叠结构和电路布局,得到目标高速电路的结构数据,具体为:

9、获取目标高速电路的3dic设计图纸数据,将所述设计图纸数据转化为图像数据,并将所述图像数据转化为灰度图像,通过高斯滤波器对所述灰度图像进行噪声去除;

10、引入canny边缘检测算法,通过sobel算子计算噪声去除后的灰度图像的梯度幅值和方向,依次按照梯度方向检查所述灰度图像的每个像素,仅当像素在对应的梯度方向上相比其邻域像素具有最大梯度值时,将该像素保留为边缘像素,否则将该像素的值置为0,得到边缘像素集;

11、将所述边缘像素集进行顺序连接操作,得到目标高速电路的电路布局;

12、根据所述目标高速电路的电路布局确定电路布局的物理层级特征,根据所述物理层级特征对不同层次的电路堆叠结构进行识别,得到目标高速电路的结构数据,所述目标高速电路的结构数据包括目标高速电路的电路布局和堆叠结构。

13、本方案中,所述根据所述结构数据将目标高速电路进行层级分割,确定每个层级之间的互连关系,根据所述互连关系构建目标高速电路的物理仿真模型,具体为:

14、根据所述结构数据确定目标高速电路中的电路元器件连接数据,所述电路元器件连接数据包括电路元器件类型、数量、连接方式、布局信息;

15、对所述电路元器件连接数据进行分析,确定每个电路元器件在目标高速电路中的功能性质;

16、根据所述功能性质将目标高速电路进行层级分割,得到目标高速电路的功能层级,所述功能层级包括电源层、信号层、地面层;

17、获取每个功能层级之间的互连关系,所述互连关系包括电路元器件连接方式、层级间通讯关系、层级连接材料,根据所述互连关系构建每个层级之间的数据输入与输出接口;

18、基于射频eda仿真软件构建目标高速电路每个功能层级物理仿真模型,基于所述互连关系将所述目标高速电路每个功能层级进行层叠排列,确定每个功能层级之间的相对位置,并基于所述电路元器件连接数据绘制每个层级的布线路径,并根据所述互连关系对目标高速电路进行通孔设计,得到目标高速电路的物理仿真模型。

19、本方案中,所述根据所述目标高速电路的物理仿真模型对所述目标高速电路进行串扰效应模拟,得到目标高速电路的串扰效应变化数据,具体为:

20、预选多个动态串扰模型,将每个动态串扰模型与目标高速电路的物理仿真模型进行连接,对目标高速电路的运行状态进行模拟,实时记录模拟过程中的目标高速电路的信号传输波形数据;

21、将所述信号传输波形数据进行傅里叶变化,将信号传输波形数据由时域信号转化为频域信号,绘制所述频域信号的频谱图;

22、根据所述频谱图提取信号在频域上的特性,得到每个动态串扰模型在与目标高速电路的物理仿真模型连接进行运行状态模拟的特性数据,所述特性数据包括频率响应数据、频率成分数据、谐波情况;

23、根据目标高速电路的3dic设计图纸数据获取目标高速电路的理论频谱图,提取所述理论频谱图的理论特性数据,将所述特性数据与理论特性数据进行对比,计算数据之间的均方根误差;

24、根据所述均方根误差评估每个动态串扰模型的模拟准确率,根据所述模拟准确率确定优选动态串扰模型;

25、设置所述优选动态串扰模型的模拟参数,所述模拟参数包括工作频率参数、信号传输路径,根据所述模拟参数对目标高速电路不同工作状态进行串扰效应模拟,观察目标高速电路的传输信号在不同电路元器件之间的传输变化,得到目标高速电路的串扰效应变化数据。

26、本方案中,所述对所述串扰效应变化数据进行信号传输影响评估,得到信号传输影响数据,根据所述信号传输影响数据对目标高速电路进行性能评估,得到性能评估结果,具体为:

27、根据所述目标高速电路的物理仿真模型获取目标高速电路的电路元器件之间的传输线的几何形状、距离、信号频率,得到电路元器件传输数据;

28、根据所述电路元器件传输数据计算每个电路元器件之间的耦合强度,得到耦合强度数据;

29、根据所述串扰效应变化数据和耦合强度数据对信号传输完整性和传输延迟进行评估,得到信号传输影响数据;

30、根据所述信号传输影响数据对目标高速电路进行性能评估,得到性能评估结果。

31、本方案中,所述根据所述性能评估结果对目标高速电路实施串扰抑制方案,具体为:

32、根据所述性能评估结果对串扰敏感区域进行识别,将串扰敏感区域进行标记操作,得到标记区域;

33、根据所述标记区域识别串扰路径,并对所述标记区域进行串扰源和串扰影响程度确定,根据所述串扰路径、串扰源、串扰影响确定目标高速电路每个标记区域的串扰抑制策略,得到串扰抑制方案;

34、对目标高速电路实施所述串扰抑制方案,并实时监测目标高速电路的串扰抑制效果,若串扰抑制效果低于预设值,对串扰抑制方案进行调整。

35、本发明第二方面还提供了一种基于3dic设计的高速电路性能评估系统,该系统包括:存储器、处理器,所述存储器中包括基于3dic设计的高速电路性能评估方法程序,所述基于3dic设计的高速电路性能评估方法程序被所述处理器执行时,实现如下步骤:

36、获取目标高速电路的3dic设计图纸数据,根据所述图纸数据确定目标高速电路的堆叠结构和电路布局,得到目标高速电路的结构数据;

37、根据所述结构数据将目标高速电路进行层级分割,确定每个层级之间的互连关系,根据所述互连关系构建目标高速电路的物理仿真模型;

38、根据所述目标高速电路的物理仿真模型对所述目标高速电路进行串扰效应模拟,得到目标高速电路的串扰效应变化数据;

39、对所述串扰效应变化数据进行信号传输影响评估,得到信号传输影响数据,根据所述信号传输影响数据对目标高速电路进行性能评估,得到性能评估结果;

40、根据所述性能评估结果对目标高速电路实施串扰抑制方案。

41、本方案中,所述获取目标高速电路的3dic设计图纸数据,根据所述图纸数据确定目标高速电路的堆叠结构和电路布局,得到目标高速电路的结构数据,具体为:

42、获取目标高速电路的3dic设计图纸数据,将所述设计图纸数据转化为图像数据,并将所述图像数据转化为灰度图像,通过高斯滤波器对所述灰度图像进行噪声去除;

43、引入canny边缘检测算法,通过sobel算子计算噪声去除后的灰度图像的梯度幅值和方向,依次按照梯度方向检查所述灰度图像的每个像素,仅当像素在对应的梯度方向上相比其邻域像素具有最大梯度值时,将该像素保留为边缘像素,否则将该像素的值置为0,得到边缘像素集;

44、将所述边缘像素集进行顺序连接操作,得到目标高速电路的电路布局;

45、根据所述目标高速电路的电路布局确定电路布局的物理层级特征,根据所述物理层级特征对不同层次的电路堆叠结构进行识别,得到目标高速电路的结构数据,所述目标高速电路的结构数据包括目标高速电路的电路布局和堆叠结构。

46、本方案中,所述根据所述结构数据将目标高速电路进行层级分割,确定每个层级之间的互连关系,根据所述互连关系构建目标高速电路的物理仿真模型,具体为:

47、根据所述结构数据确定目标高速电路中的电路元器件连接数据,所述电路元器件连接数据包括电路元器件类型、数量、连接方式、布局信息;

48、对所述电路元器件连接数据进行分析,确定每个电路元器件在目标高速电路中的功能性质;

49、根据所述功能性质将目标高速电路进行层级分割,得到目标高速电路的功能层级,所述功能层级包括电源层、信号层、地面层;

50、获取每个功能层级之间的互连关系,所述互连关系包括电路元器件连接方式、层级间通讯关系、层级连接材料,根据所述互连关系构建每个层级之间的数据输入与输出接口;

51、基于射频eda仿真软件构建目标高速电路每个功能层级物理仿真模型,基于所述互连关系将所述目标高速电路每个功能层级进行层叠排列,确定每个功能层级之间的相对位置,并基于所述电路元器件连接数据绘制每个层级的布线路径,并根据所述互连关系对目标高速电路进行通孔设计,得到目标高速电路的物理仿真模型。

52、本方案中,所述根据所述性能评估结果对目标高速电路实施串扰抑制方案,具体为:

53、根据所述性能评估结果对串扰敏感区域进行识别,将串扰敏感区域进行标记操作,得到标记区域;

54、根据所述标记区域识别串扰路径,并对所述标记区域进行串扰源和串扰影响程度确定,根据所述串扰路径、串扰源、串扰影响确定目标高速电路每个标记区域的串扰抑制策略,得到串扰抑制方案;

55、对目标高速电路实施所述串扰抑制方案,并实时监测目标高速电路的串扰抑制效果,若串扰抑制效果低于预设值,对串扰抑制方案进行调整。

56、本发明公开了一种基于3dic设计的高速电路性能评估方法及系统,传统高速电路设计常面临信号串扰等问题,影响电路性能。本方法首先获取目标高速电路的3dic设计图纸数据,确定其堆叠结构和电路布局,并进行层级分割,建立物理仿真模型。随后,通过模拟串扰效应,获取目标高速电路的串扰效应变化数据。进一步对信号传输影响进行评估,得到性能评估结果。根据评估结果,制定串扰抑制方案,以提高高速电路的性能和稳定性。本方法能有效评估高速电路性能,并针对性提出改进方案,具有重要的实用价值和经济意义。

本文地址:https://www.jishuxx.com/zhuanli/20240730/194425.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表