一种生成多FPGA原型验证平台的片间IO布局的方法

- 国知局

- 2024-07-31 23:06:57

本发明属于fpga原型验证,具体涉及一种生成多fpga原型验证平台的片间io布局的方法。

背景技术:

1、fpga是一种可以通过编程来实现各种逻辑电路的逻辑器件。fpga在量产后并不具有任何逻辑功能,硬件设计师可以重复编程实现fpga内部的逻辑电路来满足用户的需求。使用fpga的好处有:重新配置i/o模块的高度灵活性,市场周转时间短,适用于高端控制应用等。近年来越来越受到电路设计人员的重视,广泛应用于逻辑验证和快速原型设计以及可重构的自定义计算平台等方面。

2、在现代电子系统设计中,多fpga系统的应用(如fpga原型验证)越来越广泛。fpga原型验证是一种成熟芯片验证技术,通过将rtl移植到现场可编程门阵列(fpga)来验证asic的功能。对于大型的设计,一块fpga往往容纳不下,此时必须将多块fpga互联才能验证整个设计。图1为一个多fpga原型验证平台的示意图。该原型验证平台包含4片fpga。每片fpga的i/o引脚被分成j1-j8 8组socket。不同fpga的socket可以使用线缆进行连接,从而实现fpga间的互联。连接完成之后,两个被连接的fpga之间的引脚对应关系也相应确定。

3、现有eda流程主要包含以下几个步骤来使用fpga阵列进行原型验证:

4、(1)综合,将用户rtl综合为逻辑网表。

5、(2)划分,将根据实际fpga资源,将网表上的逻辑单元划分到fpga上。以图1为例,网表上的逻辑单元将被分配到4片fpga中。如果一个线网所连的逻辑单元被分配到了不同的fpga中,这意味着该线网被“切割”了,需要使用fpga i/o进行通信。在对大型asic设计进行划分的时候,被切割的线网数量往往超过fpga之间的i/o数量。这就需要使用时分复用(tdm)技术,让多根被切割的线网使用同一对fpga i/o进行通信。一个tdm ip上承载的线网数量被称为tdm ratio,tdm ratio越大意味着该tdm ip的延迟越大。

6、(3)系统布线,将决定使用多少个tdm ip、及各个tdm ip的ratio值。同时也确定各个被切割线网使用ratio为多少的tdm ip,即为线网分配ratio值。

7、(4)io placement,将确定各被切割线网具体使用哪一个tdm ip,并确定该tdm ip具体使用哪一个fpga i/o。需要注意的是,被切割的线网必须使用相对应的tdm ip以确保信号完整性。而对应的tdm ip必须放在相连的fpga io上。io placement结果对系统性能有影响。(5)fpga后端实现,将使用上述步骤的结果,对各个fpga进行布局、布线、位流生成等后端实现。这一步骤往往使用fpga厂商提供的eda工具来完成。

8、关于解决io placement的问题,现已有方案有:

9、方法1:随机分配:将ratio相同的线网随机组合,并将tdm ip随机进行io分配。该方案没有对性能进行任何优化。

10、方法2:逐个优化:先做单片fpga的io placement,该io placement结果只针对当前fpga性能进行优化。之后根据该io placement产生的的io约束对相连的fpga进行ioplacement,通过不断传递当前fpga的io placement结果来完成整个系统的io placement。该方案通过进行局部性能优化获得一个fpga io placement结果,并基于该结果进行相连fpga io placement。该方案无法进行全局优化。对于规模日益增加的仿真系统,通过局部优化结果进行推导的方案带来的收益非常有限。而且串行的进行各个fpga io placement也使得该方案运行时间过长。

技术实现思路

1、本发明的目的在于提供一种生成多fpga原型验证平台的片间io布局方法,以实现对io placement的优化。

2、本发明提供的生成多fpga原型验证平台的片间io布局方法,根据综合后端网表结构,定义切割线网之间的逻辑距离;根据fpga结构,定义i/o之间的物理距离;最后定义一个包含逻辑距离和物理距离的目标函数;通过对目标函数的优化实现io placement的全局优化;具体步骤如下:

3、(1)计算被切割线网之间的逻辑距离:

4、根据网表连接关系定义被切割线网之间的逻辑距离。逻辑距离应能反应被切割线网之间的关系:被切割线网之间关系越强,其逻辑距离应该越小。以图2为例,其中,p1、p2、p3、p4、p5为被切割线网的端口,a~i是电路设计中的cell。可以使用p1和p2之间的最短路径来定义逻辑距离。如p1端口到p2端口所经过的最短路径为p1->c->b->d->p2,则定义logicdistance_p1_p2=4。该距离定义方式并不唯一,能反应两个被切割线网端口之间的相关性即可。

5、(2)计算fpga i/o之间的物理距离:

6、使用io tile之间的曼哈顿距离、半周线长等来估算fpga io之间的物理距离。该距离定义方法并不唯一,可以反应fpga io之间的相关性即可。

7、(3)定义目标函数:

8、distance = physicaldistance(p, q) / topodistance(u, v) , (1)

9、totaldistance = ∑distance , (2)

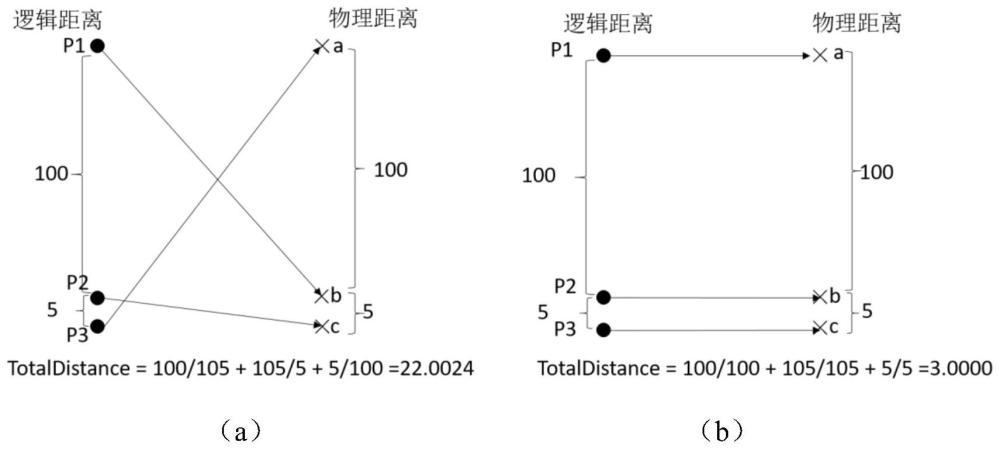

10、(1)式为包含逻辑距离和物理距离的目标函数,其中,p,q为fpga io;u、v为网表被切割线网的逻辑端口。相近的逻辑距离近的端口分配到物理距离相近的io引脚,则(1)式计算出来的distance将较小,反之将增加。(2)式为整个设计的目标函数。以图1、图2为例:右边的io布局将逻辑距离近的信号端口分配到物理距离相近的io引脚,将逻辑距离远的信号端口分配到物理距离较远的io引脚,使其totaldistance小于右边的io布局。

11、(4)优化目标函数:

12、使用模拟退火、线性规划等算法对目标函数进行优化。优化目标为降低totaldistance,从而获得优化后的io布局结果。

13、本发明通过定义网表被切割线网间的逻辑距离和fpga io之间的物理距离,定义了一个目标函数,通过对目标函数的优化来获得多fpga系统中的io布局方案。相较于随机io分配的方案,本发明能带来性能提升。相较于逐片fpga进行io placement的方案,本方案性能也较优,且可以并行的进行后端实现。

技术特征:1.一种生成多fpga原型验证平台的片间io布局方法;其特征在于根据综合后端网表结构,定义切割线网之间的逻辑距离;根据fpga结构,定义i/o之间的物理距离;最后定义一个包含逻辑距离和物理距离的目标函数;通过对目标函数的优化实现io placement的全局优化;具体步骤如下:

技术总结本发明属于FPGA原型验证技术领域,具体为一种生成多FPGA原型验证平台的片间IO布局方法。本发明方法根据综合后端网表结构,定义切割线网之间的逻辑距离;根据FPGA结构,定义I/O之间的物理距离;最后定义一个包含逻辑距离和物理距离的目标函数;通过对目标函数的优化实现IO Placement的全局优化。相较于随机IO分配方案,本发明能带来性能提升;相较于逐片FPGA进行IO Placement的方案,本发明性能较优,且可以并行的进行后端实现。技术研发人员:吴昌,张青青受保护的技术使用者:复旦大学技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240730/196029.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表