一种基于RISC-V的可伸缩Posit向量扩展方法

- 国知局

- 2024-07-31 23:22:20

本发明主要涉及计算机体系结构设计和处理器架构领域,特别是涉及一种在risc-v处理器架构上实现可伸缩posit向量扩展的方法。

背景技术:

1、近几十年来,ieee 754标准几乎被所有计算机所采用,然而,这个标准仍存在许多不足之处,例如舍入和再现性问题、带符号零和非数字(nan)表示过剩问题等等,为了解决这些问题,posit浮点数标准于2017年被john l. gustafson提出,其在动态范围和精度之间提供了很好的权衡,在操作时遇到的异常更少,具有锥形精度,并且支持融合计算,从而大大提高乘法和累加的运算精度。

2、risc-v向量扩展(v扩展)是开源指令集risc-v架构的一个扩展,主要用于数据级并行。其标准文档规定了32个向量寄存器,其指令不包含控制信息,故增加了向量控制状态寄存器,并通过向量配置指令配置向量寄存器长度(vlen)和相应寄存器状态,引入向量架构可以提高数据的并行运算速率,减少多条标量指令加载和存储带来的额外开销。

3、目前在学术界通过risc-v指令集架构设计posit运算处理单元的研究项目主要有马德里康如斯顿大学的percival、big-percival,印度孟买理工学院的clarinet,亚琛工业大学的perc,印度马德拉斯印度理工学院的peri,新加坡国立大学的posar,以及意大利比萨大学的ppu-light等。

4、在risc-v指令集架构设计的原理上,当前这些方案都是在基本标量指令集的基础上,稍加修改以支持posit数运算,并以协处理器的形式加载至已有的开源risc-v处理器上。

5、在支持posit数运算的原理上,部分方案是将浮点数直接转换为posit数,部分方案则是在ieee 754数的基础上再转换为posit数。

6、他们的共同特点都是以sisd的形式对posit数运算进行扩展,将部分标量寄存器设置为posit操作数寄存器和结果寄存器,在运算前从内存中加载操作数至寄存器,运算后把寄存器中数据存储至内存中,并单独设置一个寄存器作为融合乘加减操作寄存器(quire寄存器)。

7、但是当前基于risc-v的posit数运算方案时间开销都较大,其原因在于所有数据处理均是标量形式,目前浮点数数据的长度愈发变长,需处理的数据量愈发增多,而标量指令在同一时刻只能处理一个数据元素,处理多个数据项则需要多条指令,由此在处理海量数据时引入了大量开销。

技术实现思路

1、本发明的目的在于针对目前posit数运算并行度较低的现状,提出一种基于risc-v的可伸缩posit向量扩展方法,通过引入risc-v向量架构(v扩展),将posit数和融合乘加减运算数扩展为向量格式,并根据posit位宽将其分为三种精度(即可伸缩),自适应配置向量寄存器长度vlen,以simd的形式进行posit运算,从指令格式和数据流源头上实现posit数并行运算,减少时间开销。

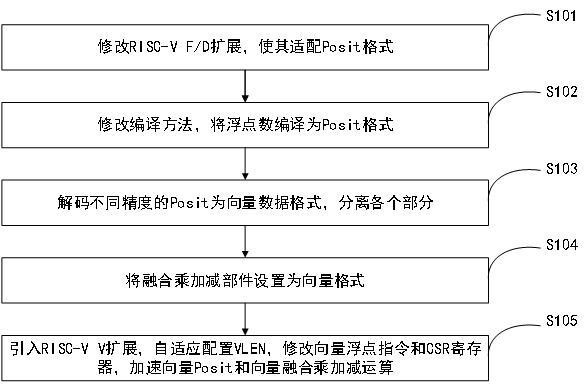

2、本发明从risc-v指令集架构入手,修改其单/双精度浮点扩展和向量架构扩展指令,从而支持不同精度posit数(即可伸缩)以向量格式存储并运算,具体步骤如下:

3、步骤一、修改risc-v f/d扩展,使其适配posit格式;

4、步骤二、修改编译方法,将浮点数编译为posit格式;

5、步骤三、解码不同精度的posit为向量数据格式,分离各个部分;

6、步骤四、将融合乘加减部件设置为向量格式;

7、步骤五、引入risc-v v扩展,自适应配置vlen,修改向量浮点指令和csr寄存器,加速向量posit运算和向量融合乘加减运算。

8、进一步,所述的步骤一在risc-v f/d扩展基础上,修改部分指令字段和csr寄存器,使其适配posit格式而非ieee 754格式。

9、进一步,所述的步骤二修改浮点数编译方法,使其生成posit数而非ieee 754数。

10、进一步,所述的步骤三用向量寄存器存储不同精度posit数,并将符号位(sign)、指数位(regime、es)和分数位(frac)分离。

11、进一步,所述的步骤四用一个足够大的向量寄存器存储定点累加器。

12、进一步,步骤五所述的引入risc-v v扩展,加速向量posit和向量融合乘加减运算的具体步骤如下:

13、步骤一、根据posit数据位宽pl,通过向量配置指令,自适应配置向量寄存器长度vlen,vlen越大,单条向量指令(如加载指令、存储指令、运算指令)处理的数据量越大,但其硬件开销和功耗也相应增加;

14、步骤二、修改向量浮点指令及csr寄存器,使其支持posit数而非ieee 754数;

15、步骤三、根据向量浮点融合乘加指令和修改后的向量浮点指令,自定义浮点融合乘加指令。

16、本发明的有益效果如下:

17、(1)本发明从指令和数据流源头上支持posit数向量运算,通过单指令多数据对多个posit操作数同时进行运算,减少了posit数的运算时间开销,提高了整体计算速率;

18、(2)本发明支持不同精度的posit数向量运算,并通过自定义向量融合乘加减指令,支持了quire运算功能,使得多次乘后加减仅进行一次舍入,提高了posit数的运算精度;

19、(3)本发明可以在不同risc-v平台上实现可伸缩posit向量运算,适用于多种编译平台,具有通用性。

技术特征:1.一种基于risc-v的可伸缩posit向量扩展方法,其特征在于,所述的运用risc-v指令集对posit进行向量扩展的方法包括如下步骤:

2.如权利要求1所述的一种基于risc-v的可伸缩posit向量扩展方法,其特征在于,所述的步骤一在risc-v f/d扩展基础上,修改部分指令字段和csr寄存器,使其适配posit格式而非ieee 754格式。

3.如权利要求1所述的一种基于risc-v的可伸缩posit向量扩展方法,其特征在于,所述的步骤二修改浮点数编译方法,使其生成posit数而非ieee 754数。

4.如权利要求1所述的一种基于risc-v的可伸缩posit向量扩展方法,其特征在于,所述的步骤三用向量寄存器存储不同精度posit数,并将符号位(sign)、指数位(regime、es)和分数位(frac)分离。

5.如权利要求1所述的一种基于risc-v的可伸缩posit向量扩展方法,其特征在于,所述的步骤四用一个足够大的向量寄存器存储定点累加器。

6.如权利要求1所述的一种基于risc-v的可伸缩posit向量扩展方法,其特征在于,所述的步骤五通过修改risc-v v扩展,自适应配置vlen,加速向量posit运算和向量融合乘加减运算的具体步骤如下:

技术总结本发明公开了一种基于RISC‑V的可伸缩Posit向量扩展方法,该方法包括如下步骤:修改RISC‑V F/D扩展,使其适配Posit格式;修改编译方法,将浮点数编译为Posit格式;解码Posit为不同精度的向量数据格式,分离各个部分;将融合乘加减部件设置为向量格式;引入RISC‑V V扩展,自适应配置VLEN,修改向量浮点指令和CSR寄存器,加速向量Posit和向量融合乘加减运算。本发明的目的在于针对Posit具有精度高范围广且运算可再现等优点但其运算并行度较低的现状,将RISC‑V和Posit集成起来,修改单/双精度浮点数扩展(F/D扩展)将浮点数用Posit格式表示,来克服IEEE 754缺点,修改相应编译器使其支持Posit格式,最后引入向量架构扩展(V扩展),修改并自定义相应指令,加速Posit和融合乘加减运算。技术研发人员:王耀彬,吴欣宇,唐苹苹,欧洪余,刘基宏受保护的技术使用者:西南科技大学技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240730/197252.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表