一种用于高速高精度ADC的升压开关电路的制作方法

- 国知局

- 2024-07-31 17:29:15

本发明属于高速通信,具体涉及一种用于高速高精度adc的升压开关电路。

背景技术:

1、随着国家对国产化军用航天芯片需求和要求的逐步提高,运用于军工领域的高速高精度adc(analog to digital converter,模数转换器)作为核心电路之一,高速高精度adc的核心技术的国产化需求日益紧迫。

2、目前,高速高精度adc使用的工艺愈发先进,沟道长度逐渐减小,电源电压逐渐降低,为了能够发挥先进工艺的速度优势,满足高速高精度adc的设计需求,通常需要在关键路径上使用核心器件(也可称之为“core器件”)。但是,在使用现有技术过程中,发明人发现现有技术中至少存在如下问题:

3、核心器件的超压问题将很大程度地影响电路的寿命以及可靠性问题,传统的升压开关电路难以在解决超压问题的同时,满足电路的速度以及精度要求。

4、因此,目前迫切地需要一种新型的用于高速高精度adc的升压开关电路。

技术实现思路

1、本发明旨在至少在一定程度上解决上述技术问题,本发明提供了一种用于高速高精度adc的升压开关电路。

2、为了实现上述目的,本发明采用以下技术方案:

3、本发明提供了一种用于高速高精度adc的升压开关电路,包括电荷泵升压电路、升压时钟生成电路和电压缓冲电路;其中,所述电荷泵升压电路,用于接收初始时钟信号clkin,并对所述初始时钟信号clkin进行升压处理,以便得到时钟控制信号clk_boost;所述升压时钟生成电路,用于接收初始时钟信号clkin,并对所述时钟控制信号clk_boost进行二次升压处理,以便得到目标时钟信号clk_bst;所述电压缓冲电路,用于接收可修调的偏置电流ibias,并基于所述偏置电流ibias为所述电荷泵升压电路和所述升压时钟生成电路输入偏置电压。

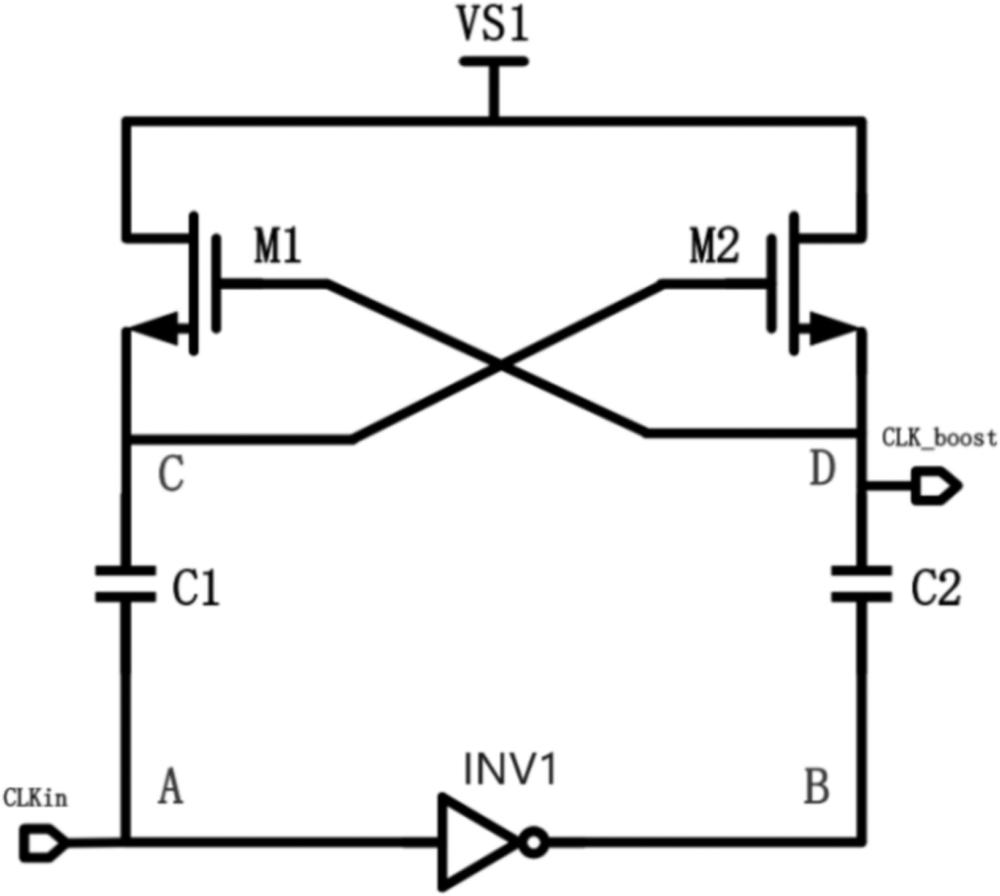

4、在一个可能的设计中,所述电荷泵升压电路包括第一反相器、第一电容、第二电容、第一mos管和第二mos管;所述第一反相器的输入端与所述第一电容的下极板连接,所述第一反相器的输入端与所述第一电容的下极板的结合点作为所述电荷泵升压电路的输入端接收初始时钟信号clkin,所述第一反相器的输出端与所述第二电容的下极板连接,所述第一电容的上极板分别与所述第一mos管的输出端和所述第二mos管的受控端连接,所述第二电容的上极板分别与所述第一mos管的受控端和所述第二mos管的输出端连接,所述第二电容、所述第一mos管和所述第二mos管的结合点作为所述电荷泵升压电路的输出端输出时钟控制信号clk_boost,所述第一mos管的输入端和所述第二mos管的输入端均与所述电压缓冲电路的vs1输出端连接。

5、在一个可能的设计中,所述第一mos管采用第一n型mos管,所述第二mos管采用第二n型mos管;所述第一n型mos管的栅极作为所述第一mos管的受控端,所述第一n型mos管的源极作为所述第一mos管的输出端,所述第一n型mos管的漏极作为所述第一mos管的输入端;所述第二n型mos管的栅极作为所述第二mos管的受控端,所述第二n型mos管的源极作为所述第二mos管的输出端,所述第二n型mos管的漏极作为所述第二mos管的输入端。

6、在一个可能的设计中,所述第一mos管采用第一p型mos管,所述第二mos管采用第二p型mos管;所述第一p型mos管的栅极作为所述第一mos管的受控端,所述第一p型mos管的漏极作为所述第一mos管的输出端,所述第一p型mos管的源极作为所述第一mos管的输入端;所述第二p型mos管的栅极作为所述第二mos管的受控端,所述第二p型mos管的漏极作为所述第二mos管的输出端,所述第二p型mos管的源极作为所述第二mos管的输入端。

7、在一个可能的设计中,所述升压时钟生成电路包括第二反相器、第三反相器、第三电容、第四电容、第五电容、第三p型mos管、第三n型mos管、第四n型mos管、第四p型mos管和第五n型mos管;所述第二反相器的输入端和所述第三p型mos管的栅极均作为所述升压时钟生成电路的输入端接收初始时钟信号clkin,所述第二反相器的输出端分别与所述第三反相器的输入端和所述第三电容的下极板连接,所述第三电容的上极板分别与所述第三p型mos管的漏极和所述第四p型mos管的栅极连接,所述第三反相器的输出端分别与所述第四电容的下极板和所述第五n型mos管的源极连接,所述第五n型mos管的漏极分别与所述第五电容的下极板和所述第四p型mos管的源极连接,所述第四电容的上极板分别与所述第三n型mos管的源极和所述第四p型mos管的漏极连接,所述第三n型mos管的漏极、所述第三p型mos管的源极和所述第五n型mos管的栅极均接入电源电压avdd1,所述第五电容的上极板与所述第四n型mos管的源极连接,所述第四n型mos管的漏极与所述电压缓冲电路的vs1输出端连接,所述第三n型mos管的栅极和所述第四n型mos管的栅极均与所述电荷泵升压电路的输出端连接,所述第三n型mos管的栅极和所述第四n型mos管的栅极从所述电荷泵升压电路接收的时钟控制信号clk_boost分别为vboost1信号和vboost2信号,所述第四n型mos管和所述第五电容的结合点作为所述升压时钟生成电路的输出端输出目标时钟信号clk_bst。

8、在一个可能的设计中,所述升压时钟生成电路包括第一传输门、第二传输门、第六电容、第六n型mos管、第七n型mos管、第八n型mos管、第九n型mos管、第十n型mos管、第十一n型mos管、第五p型mos管和第六p型mos管;所述第一传输门的输入端和所述第二传输门的输入端作为所述升压时钟生成电路的输入端接收初始时钟信号clkin,所述第一传输门的控制信号输入端和所述第二传输门的控制信号输入端均与所述电荷泵升压电路的输出端连接,所述第一传输门的两个控制信号输入端以及所述第二传输门的两个控制信号输入端从所述电荷泵升压电路接收的时钟控制信号clk_boost均分别为clk1信号和clk2信号,且clk1信号和clk2信号互补且不交叠;所述第二传输门的输出端分别与所述第六电容的上极板和所述第六n型mos管的源极连接,所述第六n型mos管的漏极与所述电压缓冲电路的vs1输出端连接,所述第六电容的下极板分别与所述第七n型mos管的源极和所述第六p型mos管的源极连接,所述第六n型mos管的栅极和所述第七n型mos管的栅极均接收clk2信号,所述第七n型mos管的漏极与所述电压缓冲电路的vs2输出端连接,所述第一传输门的输出端分别与所述第五p型mos管的漏极和所述第六p型mos管的栅极连接,所述第五p型mos管的栅极接收clk1信号,所述第五p型mos管的漏极与所述电压缓冲电路的vs2输出端连接,所述第六p型mos管的漏极分别与所述第九n型mos管的源极和所述第十n型mos管的漏极连接,且所述第六p型mos管、所述第九n型mos管和所述第十n型mos管的结合点作为所述升压时钟生成电路的输出端输出目标时钟信号clk_bst,所述第九n型mos管的栅极和所述第十n型mos管的栅极均接收预设的常高电平,所述第九n型mos管的漏极与所述第八n型mos管的源极连接,所述第八n型mos管的漏极与所述电压缓冲电路的vs3输出端连接,所述第八n型mos管的栅极接收clk2信号,所述第十n型mos管的源极与所述第十一n型mos管的漏极连接,所述第十一n型mos管的源极接地,所述第十一n型mos管的栅极接收预设的pwd外界控制信号。

9、在一个可能的设计中,所述电压缓冲电路设置有多个,多个所述电压缓冲电路的输出端分为vs1输出端、vs2输出端和vs3输出端。

10、在一个可能的设计中,所述电压缓冲电路包括电阻和运算放大器,所述运算放大器的同相输入端作为所述电压缓冲电路的输入端接收可修调的偏置电流ibias,所述运算放大器的同相输入端还通过所述电阻接地,所述运算放大器的反向相输入端与所述运算放大器的输出端连接,且所述运算放大器的输出端为所述电压缓冲电路的输出端输出偏置电压。

11、本发明的有益效果为:

12、本发明公开了一种用于高速高精度adc的升压开关电路,可以提高高速高精度adc关键路径上的采样开关线性度与采样率,同时可提高高速高精度adc电路的可靠性以及寿命。本发明相较于传统的升压开关电路,额外引入了电荷泵升压电路和电压缓冲电路,能够满足高速高精度adc宽摆幅的输入范围,避免与输入信号直接相连的采样开关等关键路径上出现超压问题。具体地,本发明通过电荷泵升压电路根据收初始时钟信号clkin产生用于升压时钟生成电路的时钟控制信号clk_boost,同时引入电压缓冲电路对电荷泵升压电路和升压时钟生成电路进行供电,在此过程中,由于电压缓冲电路使用了可修调的偏置电流,可以根据电荷泵升压电路和升压时钟生成电路的需求,自主地调节时钟高低电平的大小来解决超压问题,满足高速高精度adc的速度和精度要求,同时可以达到的速度以及线性度灵活可调,利于提高高速高精度adc电路的可靠性以及寿命。

13、本发明的其他有益效果将在具体实施方式中进一步进行说明。

本文地址:https://www.jishuxx.com/zhuanli/20240731/175739.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表