电力电子器件的终端结构及其制备方法与流程

- 国知局

- 2024-07-31 18:09:28

本发明属于半导体器件,具体涉及一种电力电子器件的终端结构及其制备方法。

背景技术:

1、除了有源区的元胞设计外,电力电子芯片的耐压设计还必须考虑终端区结构。电力电子芯片的终端通常为球面结或柱面结,如果不进行特殊的终端结构设计,曲率效应会导致终端区的击穿电压远低于元胞区平行平面结的击穿电压,致使器件的实际耐压远低于设计值。

2、电力电子器件常用的终端结构包括场限环、场板和结终端延展结构等。场限环由于其较为简单的设计与制造工艺,在不同电压等级的电力电子芯片中已得到广泛使用。然而该结构占用芯片面积很大,且对界面电荷较为敏感。

3、现有的沟槽终端结构如图3所示,在终端区设置填有介质并间隔分布的n个沟槽,该结构可以大幅降低终端结构占用的芯片面积,然而终端区沟槽侧壁或底部的介质层与半导体界面处的等势线分布往往不够均匀,以致于该区域容易提前击穿。单一沟槽终端结构的击穿电压远低于理想平行平面结击穿电压的问题限制了该结构的应用。

技术实现思路

1、针对上述电力电子器件终端结构的不足,本发明提供一种电力电子器件的终端结构及其制备方法。本发明的目的是在尽量减小终端区芯片面积的同时,解决沟槽终端结构容易提前击穿的问题,确保器件的耐压能力。

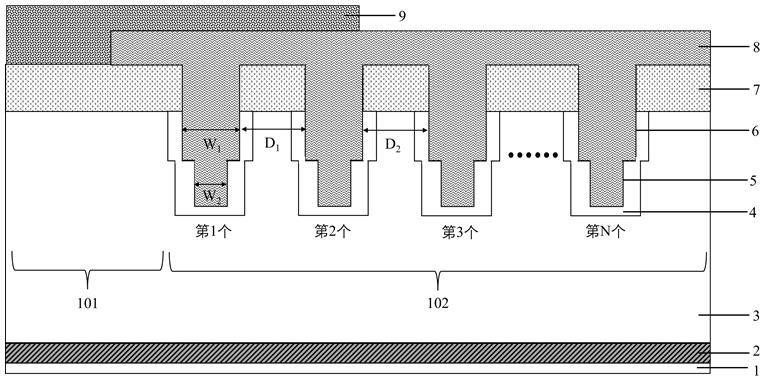

2、电力电子器件的终端结构,包括,

3、阴极电极;

4、第一导电类型衬底,位于所述阴极电极之上;

5、第一导电类型外延层,位于所述第一导电类型衬底之上;

6、第二导电类型结区,位于所述第一导电类型外延层之中;

7、第一沟槽,位于所述第一导电类型外延层之中,贯穿所述第二导电类型结区,共n个;

8、第二沟槽,位于所述第一导电类型外延层之中,与所述第一沟槽底部相连通,共n个,第二沟槽的宽度小于第一沟槽的宽度;

9、第二导电类型扩展区,位于第一沟槽的侧壁、第二沟槽的侧壁及底部;

10、钝化层,位于所述第一导电类型外延层之上以及第一沟槽、第二沟槽之中,完全填覆第一沟槽和第二沟槽;

11、阳极电极,位于所述钝化层的一侧及之上。

12、电力电子器件的终端结构的制备方法,包括以下步骤:

13、步骤1.在第一导电类型衬底之上通过外延工艺形成第一导电类型外延层;

14、步骤2.在第一导电类型外延层之中形成第二导电类型结区;

15、步骤3.对第一导电类型外延层进行刻蚀,形成间隔分布的第一沟槽;

16、步骤4.对第一沟槽的底部进行刻蚀,形成第二沟槽;第二沟槽的宽度小于第一沟槽的宽度;

17、步骤5.在第一沟槽的侧壁、第二沟槽的侧壁及底部形成第二导电类型扩展区;

18、步骤6. 于第一导电类型外延层之上、第一沟槽和第二沟槽之中形成钝化层;

19、步骤7. 于钝化层的一侧及之上形成阳极电极,于第一导电类型衬底的底部形成阴极电极。

20、本发明采用上述技术方案,具有如下有益效果:

21、本发明提出的电力电子器件的终端结构及其制备方法,于终端区形成n个间隔分布、各自连通的第一沟槽和第二沟槽,并于第一沟槽和第二沟槽的周围形成完全包裹第一沟槽和第二沟槽的第二导电类型扩展区,大幅延展了主结耗尽区,显著改善了沟槽附近等势线的均匀程度,进而减小了终端区的峰值电场。在具备沟槽终端结构占用芯片面积较小的优势的同时,解决了介质层和半导体界面提前击穿的问题,确保了器件耐压符合设计目标。

技术特征:1.电力电子器件的终端结构,其特征在于,包括,

2.根据权利要求1所述的电力电子器件的终端结构,其特征在于,

3. 根据权利要求1所述的电力电子器件的终端结构,其特征在于,所述第一沟槽的宽度为w1,w1的范围为0.5µm ~ 2.0µm,所述第二沟槽的宽度为w2,w2的范围为0.3µm ~ 1.6µm,w1大于w2,二者之差不小于0.2µm。

4.根据权利要求1所述的电力电子器件的终端结构,其特征在于,n的数值范围为5~60。

5.根据权利要求1所述的电力电子器件的终端结构,其特征在于,距离有源区最近的第一沟槽为第一个第一沟槽,距离有源区次近的第一沟槽为第二个第一沟槽,以此类推,距离有源区最远的第一沟槽为第n个第一沟槽;第一个第一沟槽和第二个第一沟槽的间距为d1,第二个第一沟槽和第三个第一沟槽的间距为d2,以此类推,第n-1个第一沟槽和第n个第一沟槽的间距为dn-1,d1、d2、乃至dn-1的数值相同或不同。

6.根据权利要求1所述的电力电子器件的终端结构,其特征在于,距离有源区最近的第一沟槽为第一个第一沟槽,距离有源区次近的第一沟槽为第二个第一沟槽,以此类推,距离有源区最远的第一沟槽为第n个第一沟槽;距离有源区最近的第二沟槽为第一个第二沟槽,距离有源区次近的第二沟槽为第二个第二沟槽,以此类推,距离有源区最远的第二沟槽为第n个第二沟槽;在第一个第一沟槽和第二个第一沟槽之间,以及第二个第一沟槽和第三个第一沟槽之间,阳极电极的深度增大,集成场板结构。

7.根据权利要求1-6任一所述的电力电子器件的终端结构的制备方法,其特征在于,包括以下步骤:

8.根据权利要求7所述的电力电子器件的终端结构的制备方法,其特征在于,步骤3和步骤4中,采用icp刻蚀工艺,采用的刻蚀气体是sf6、hbr、cl2、o2、ar气体中的一种或多种组合。

9.根据权利要求7所述的电力电子器件的终端结构的制备方法,其特征在于,步骤5中,采用倾斜离子注入工艺形成第二导电类型扩展区。

技术总结本发明公开了一种电力电子器件的终端结构及其制备方法。该电力电子器件的终端结构包括第一导电类型衬底、第一导电类型外延层,第二导电类型结区、第二导电类型扩展区,第一沟槽、第二沟槽,钝化层,阳极电极,阴极电极。于器件终端区形成N个间隔分布的第一沟槽和第二沟槽,于第一沟槽和第二沟槽的周围形成完全包裹第一沟槽和第二沟槽的第二导电类型扩展区,在具备较小的终端芯片面积的同时,显著提升了终端区等势线的均匀程度,大幅提高了终端结构的效率,有效确保了器件的耐压能力。本发明同时公开了所述器件结构的制备方法。技术研发人员:张跃,杨晓磊,陈谷然,张泽宇,黄润华,柏松,杨勇受保护的技术使用者:南京第三代半导体技术创新中心有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178090.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

热反应腔室的制作方法

下一篇

返回列表