一种集成双PMOS自适应控制SOILIGBT

- 国知局

- 2024-07-31 18:52:19

本发明属于功率半导体,涉及一种集成双pmos自适应控制soi ligbt(lateral insulated gate bipolar transistor,横向绝缘栅双极型晶体管)。

背景技术:

1、igbt是电能变换和传输的核心器件,结合了双极bjt和单极mosfet器件的优势,具有开通损耗小、输入阻抗大、控制电路简单和工作频率高等优点,被广泛应用在通信技术、电动汽车、新能源装备、智能电网、轨道交通和军工航天等领域。soi基ligbt具有埋氧层,可以隔离衬底层与器件有源层,其具有泄漏电流小,寄生电容小,抗辐照能力强,便于集成的优势,促使soi ligbt成为单片功率集成芯片的核心元器件。

2、igbt得益于导通时漂移区内的电导调制效应,可以在保证低的导通压降的同时也能保证高击穿电压。然而关断时,存储在漂移区的大量载流子会使器件出现较长的拖尾电流,特别是漂移区内电子缺少释放通道,造成较大的关断损耗,限制igbt的高频应用。因此,导通压降和关断损耗的矛盾仍是igbt的基本问题。缓解二者矛盾关系的典型技术有以下三种。其一,寿命控制技术可使漂移区内的载流子复合速度变快,减小器件关断损耗。然而,此种技术亦会使器件导通时漂移区内非平衡载流子浓度减小,导通压降上升。其二,在阴极端引入具有空穴阻挡作用的存储层,使靠近阴极端一侧的漂移区载流子浓度升高,减小导通压降,但其非平衡载流子仍需通过复合消失,关断速度依旧较慢。其三,短路阳极技术可提供一条电子抽取通道,大大缓解长拖尾电流的现象,获得导通压降和关断损耗的良好折衷。但短路阳极结构带来的snapback效应会影响电流分布的均匀性,不利于器件并联应用。

3、此外,igbt由于工作在饱和区的强电流能力,会使其在短路发生时的高压大电流状态下产生大的功耗,从而发生闩锁、提前热击穿甚至失效,因此igbt的高饱和电流与短路时间的矛盾关系也是igbt需要解决的问题。缓解二者的矛盾关系的典型技术有以下三种。其一,在阴极端引入高掺杂的p型埋层,降低与阴极寄生二极管并联的等效电阻值,抑制寄生二极管开启从而抑制闩锁。然而当igbt电导调制效应较强时,该技术依然有发生闩锁的风险。其二,在阴极端引入空穴旁路,抽取阴极附近的空穴使电导调制效应被削弱,降低饱和电流,从而降低器件在发生短路时的功耗,提高短路能力。由于该技术削弱了器件导通时的电导调制效应,又会使器件的导通压降升高。其三,使n+阴极远离空穴路径,空穴电流在水平方向上直接到达阴极区p+被收集,不会流经阴极区n+,有效降低了闩锁风险。但由于电子电流路径增大,在关断的时候对过剩非平衡电子的移除要花费更多的时间。

技术实现思路

1、针对上述问题,本发明提出一种集成双pmos自适应控制soi ligbt,实现低泄漏电流,低导通压降,低关断损耗,高饱和电流以及长短路耐受时间。

2、本发明的技术方案是:

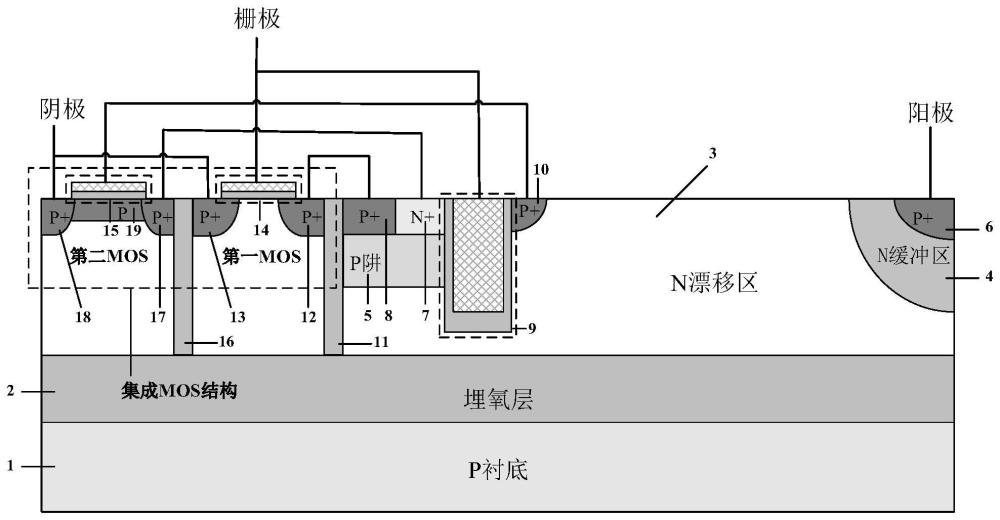

3、一种集成双pmos自适应控制soi ligbt,包括自下而上依次层叠设置的p衬底1、埋氧层2和n漂移区3;沿器件横向方向,所述n漂移区3的上层从一侧到另一侧依次具有集成mos结构、阴极结构、栅极结构和阳极结构;

4、其特征在于,所述集成mos结构包括第一mos和第二mos;所述第一mos和第二mos通过第二介质隔离槽16隔离,所述第一mos与阴极结构通过第一介质隔离槽11隔离,且第一介质隔离槽11和第二介质隔离槽16从表面沿器件垂直方向向下贯穿n漂移区3后与埋氧层2接触;所述第一mos/第二mos包括第一p+源区12/第二p+源区17、第一p+漏区13/第二p+漏区18、p沟道区19、第一p+源区12/第二p+源区17和第一p+漏区13/第二p+漏区18之间n漂移区3上方的第一平面栅14/第二平面栅15;所述第一p+源区12和第一p+漏区13位于第一介质隔离槽11和第二介质隔离槽16之间的n漂移区3上层两端;所述第二p+源区17和第二p+漏区18位于第二介质隔离槽16远离第一介质隔离槽11一侧的n漂移区3上层两端;所述沟道区19位于第二平面栅15下方,其两侧分别与第二p+源区17和第二p+漏区18接触;所述第一p+源区12/第二p+源区17与第一介质隔离槽11/第二介质隔离槽16接触;所述第一p+漏区13与第二介质隔离槽16接触;

5、所述阴极结构包括p阱区5、p+区8和n+区7;所述p阱区5和第一介质隔离槽11接触,且位于n漂移区3上层;所述p+区8和n+区7相互接触并列位于p阱区5上表面,所述p+区8和第一介质隔离槽11接触,所述n+区7在靠近n漂移区3的一侧;

6、所述栅极结构包括槽栅结构9和第一p型体接触区10;所述槽栅结构9从表面沿器件垂直方向向下延伸至n漂移区3中,所述槽栅结构9和第一p型体接触区10相互接触并列位于n漂移区3上层,所述槽栅结构9远离n漂移区3一侧与p阱区5和n+区7接触,所述第一p型体接触区10在靠近n漂移区3的一侧;

7、所述阳极结构包括n型缓冲层4和p+阳极区6;所述n型缓冲层4位于n漂移区3上层另一端,所述p+阳极区6位于n型缓冲层4上层,p+阳极区6的引出端为阳极;

8、所述槽栅结构9和第一平面栅14的共同引出端为栅极;所述第一p+漏区13、第二p+漏区18共同引出端为阴极;所述n+区7和第二p+源区17的引出端用浮空欧姆接触连接;所述p+区8和第一p+源区12的引出端用浮空欧姆接触连接;所述第一p型体接触区10和第二平面栅15的引出端用浮空欧姆接触连接。

9、本发明的有益效果为,相比于传统的soi ligbt,本发明可实现更低的正向导通压降,更低的关断损耗,更长的短路耐受时间,且能与功率集成电路的高低压器件工艺兼容,制备成本低。

技术特征:1.一种集成双pmos自适应控制soiligbt,包括自下而上依次层叠设置的p衬底(1)、埋氧层(2)和n漂移区(3);沿器件横向方向,所述n漂移区(3)的上层从一侧到另一侧依次具有集成mos结构、阴极结构、栅极结构和阳极结构;

技术总结本发明属于功率半导体技术领域,涉及一种集成双PMOS自适应控制SOI LIGBT。本发明的主要特征在于:在SOI LIGBT阴极侧集成2个MOS管,且通过氧化隔离槽互相隔离。MOS管通过电气连接可实现自适应控制SOI LIGBT。正向导通时,集成MOS自适应控制SOI LIGBT寄生二极管开启,增强电导调制效应,有效降低器件的导通压降,提高器件的驱动能力;正向关断时,集成MOS结构的第一MOS导通降低阴极P+电位,控制SOI LIGBT寄生二极管截止,退出电导调制。随着耗尽区扩展,集成MOS结构的第二MOS关闭使阴极N+电位升高,控制SOI LIGBT槽栅沟道的电子注入迅速降低;短路状态下,随着阳极电压升高,集成MOS结构的第二MOS夹断P沟道,阴极N+电位升高,降低阴极N+电子电流,抑制闩锁效应,提高器件的抗短路能力。技术研发人员:魏杰,赵凯,卢金龙,魏雨夕,刘人宽,朱鹏臣,王俊楠,罗小蓉受保护的技术使用者:电子科技大学技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/180876.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表