一种抗辐射双端口16管存储单元阵列的制作方法

- 国知局

- 2024-07-31 19:21:16

本发明涉及存储器,特别涉及一种抗辐射双端口16管存储单元阵列。

背景技术:

1、抗辐照双端口sram电路采用两套独立的地址、数据和控制总线,允许两个独立的实体(如两个处理器)同时对其进行存取访问,双端口存储单元为抗seu(single eventupset,单粒子翻转)加固的dice结构包含16个mos管。

2、随着半导体技术的不断发展,不断更新的电子产品对存储器的性能提出了更高的要求,包括更大的容量、更高的读写速度等。同一工艺节点下,存储容量的提升意味着芯片面积的增大。同时,由于存储单元阵列规模的增大,使得单元的字线和位线等长导线寄生rc阻抗增加,影响存储阵列的读写速度;为了降低信号传输路径阻抗,一般会通过增加译码层次来缩减字线位线长度、通过适量增加线宽降低寄生电阻,但是这些操作也会导致芯片面积增加。

3、为了解决容量、速度与面积之间的矛盾,同一工艺节点下,在满足设计规则的条件下通常采用缩减存储阵列器件尺寸、传输线间距方式来实现面积缩减,然而这种方式会导致器件驱动能力减弱、同一层相邻字线、相邻位线之间耦合电容增加。对于抗辐射双端口16管单元阵列来说,由于其单元器件数量较多,阵列面积大,这一问题会更加严重。当执行一端口写操作而另一端口同时对相同列、相邻行的单元执行读操作时,较强的写入数据信号受到位线间耦合电容的影响,会串扰薄弱的读取数据信号,最终导致读取失效,甚至会修改正在执行读取操作的单元内存储的数值。

技术实现思路

1、本发明的目的在于提供一种抗辐射双端口16管存储单元阵列,在不增加额外层次的基础上,解决存储容量、存取速度与阵列面积之间的矛盾,避免双端口同时执行读写操作时发生位线信号串扰现象。

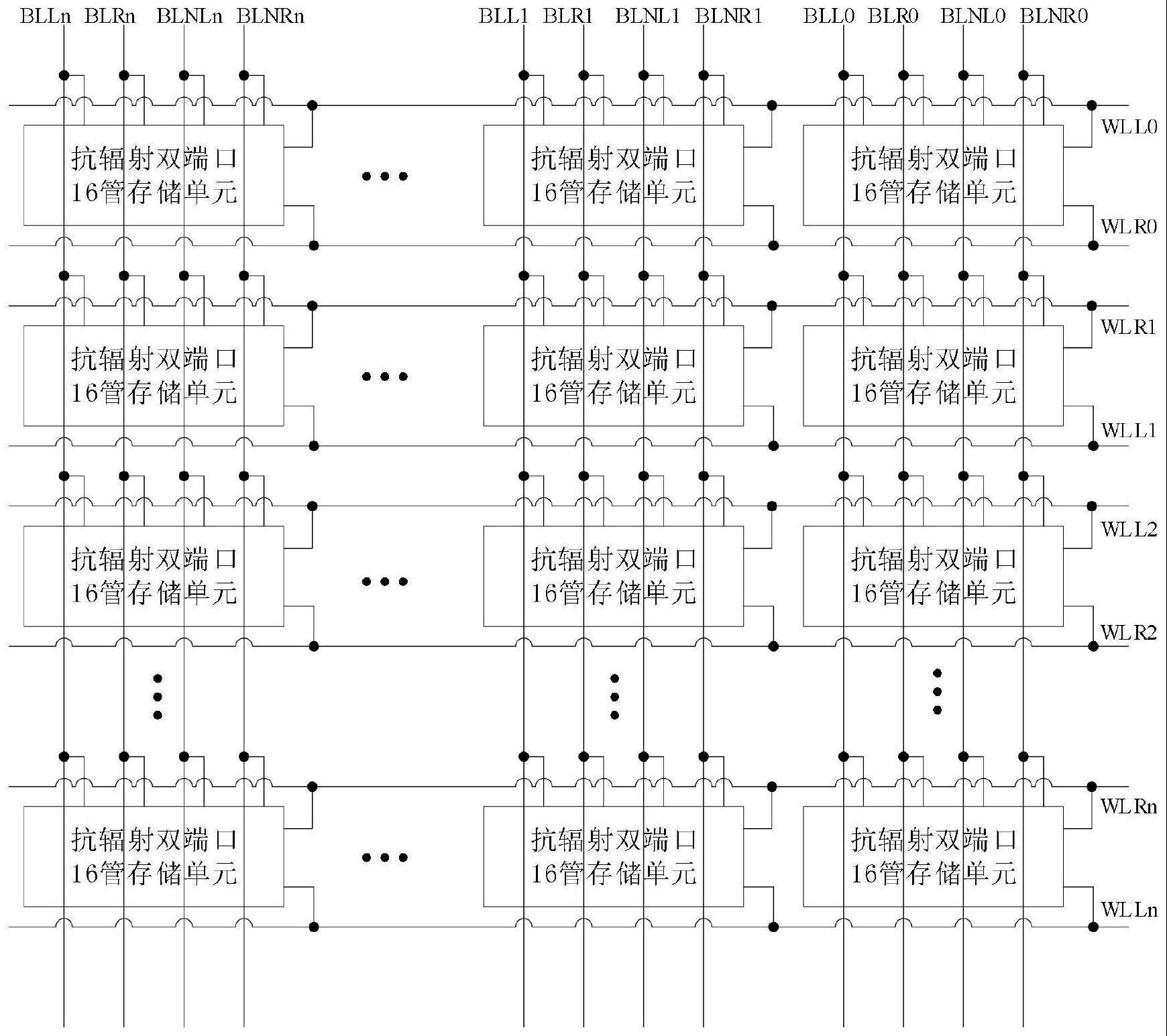

2、为解决上述技术问题,本发明提供了一种抗辐射双端口16管存储单元阵列,包括:

3、dice结构抗辐射双端口16管存储单元、左端口字线wlln、右端口字线wlrn、左端口位线blln和blnln、右端口位线blrn和blnrn;其中n=0、1、2、3…;

4、所述dice结构抗辐射双端口16管存储单元包含用于存储数据信息的单元管和用于开启存储单元的选择门管;

5、所述左端口位线blln和blnln用于左端口操作时传输一对相反数据信号,其连接一列存储单元左端口选择门管的源端;

6、所述右端口位线blrn和blnrn用于右端口操作时传输一对相反数据信号,其连接一列存储单元右端口选择门管的源端;

7、所述左端口字线wlln用于左端口操作时选择一行存储单元,其连接该行存储单元左端口选择门管的栅端;

8、所述右端口字线wlrn用于右端口操作时选择一行存储单元,其连接该行存储单元右端口选择门管的栅端。

9、在一种实施方式中,所述单元管包括pmos管mp0、pmos管mp1、pmos管mp2、pmos管mp3、nmos管mn4、noms管mn5、nmos管mn6和nmos管mn7;所述选择门管包括nmos管mn8、nmos管mn9、nmos管mn10、nmos管mn11、nmos管mn12、nmos管mn13、nmos管mn14和nmos管mn15;

10、pmos管mp0的源端接电源电压,pmos管mp0的漏端同时接nmos管mn8的漏端、nmos管mn4的漏端、pmos管mp1的栅端、nmos管mn12的漏端和nmos管mn7的栅端,pmos管mp0的栅端同时接nmos管mn11的漏端、pmos管mp3的漏端、nmos管mn7的漏端、nmos管mn15的漏端和nmos管mn6的栅端;

11、pmos管mp1的源端接电源电压,pmos管mp1的漏端同时接nmos管mn9的漏端、pmos管mp3的mp2的栅端、nmos管mn5的漏端、nmos管mn4的栅端和nmos管mn13的漏端,pmos管mp1的栅端同时接nmos管mn8的漏端、pmos管mp0的漏端、nmos管mn4的漏端、nmos管mn12的漏端和nmos管mn7的栅端;

12、pmos管mp2的源端接电源电压,pmos管mp2的漏端接nmos管mn10的漏端、pmos管mp3的栅端、nmos管mn6的漏端、nmos管mn5的栅端和nmos管mn14的漏端,pmos管mp2的栅端同时接nmos管mn9的漏端、pmos管mp1的漏端、nmos管mn5的漏端、nmos管mn4的栅端和nmos管mn13的漏端;

13、pmos管mp3的源端接电源电压,pmos管mp3的漏端同时接nmos管mn11的漏端、pmos管pm0的栅端、nmos管mn7的漏端、nmos管mn6的栅端和nmos管mn15的漏端,pmos管mp3的栅端同时接nmos管mn10的漏端、pmos管mp2的漏端、nmos管mn6的漏端、nmos管mn5的栅端和nmos管mn14的漏端;

14、nmos管mn4的源端接地,nmos管mn4的漏端同时接nmos管mn8的漏端、pmos管mp0的漏端、pmos管mp1的栅端、nmos管mn12的漏端和nmos管mn7的栅端,nmos管mn4的栅端同时接nmos管mn9的漏端、pmos管mp2的栅端、nmos管mn5的漏端、pmos管mp1的漏端和nmos管mn13的漏端;

15、nmos管mn5的源端接地,nmos管mn5的漏端同时接nmos管mn9的漏端、pmos管mp2的栅端、pmos管mp1的漏端、nmos管mn4的栅端和nmos管mn13的漏端,nmos管mn5的栅端同时接nmos管mn10的漏端、pmos管mp3的栅端、nmos管mn6的漏端、pmos管mp2的漏端和nmos管mn14的漏端;

16、nmos管mn6的源端接地,nmos管mn6的漏端同时接nmos管mn10的漏端、pmos管mp3的栅端、pmos管mp2的漏端、nmos管mn5的栅端和nmos管mn14的漏端,nmos管mn6的栅端同时接nmos管mn11的漏端、pmos管pm0的栅端、nmos管mn7的漏端、pmos管mp3的源端和nmos管mn15的漏端;

17、nmos管mn7的源端接地,nmos管mn7的漏端同时接nmos管mn11的漏端、pmos管pm0的栅端、pmos管mp3的漏端、nmos管mn6的栅端和nmos管mn15的漏端,nmos管mn7的栅端同时接nmos管mn8的漏端、nmos管mn4的漏端、pmos管mp1的栅端、nmos管mn12的漏端和pmos管mp0的漏端;

18、nmos管mn8的栅端接字线wll,nmos管mn8的源端接位线bll,nmos管mn8的漏端同时接pmos管mp0的漏端、nmos管mn4的漏端、pmos管mp1的栅端、nmos管mn12的漏端和nmos管mn7的栅端;

19、nmos管mn9的栅端接字线wll,nmos管mn9的源端接位线blnl,nmos管mn9的漏端同时接pmos管mp1漏端、pmos管mp2的栅端、nmos管mn5的漏端、nmos管mn4的栅端和nmos管mn13的漏端;

20、nmos管mn10的栅端接字线wll,nmos管mn10的源端接位线bll,nmos管mn10的漏端同时接pmos管mp2的漏端、pmos管mp3的栅端、nmos管mn6的漏端、nmos管mn5的栅端和nmos管mn14的漏端;

21、nmos管mn11的栅端接字线wll,nmos管mn11的源端接位线blnl,nmos管mn11的漏端同时接pmos管mp3的漏端、pmos管pm0的栅端、nmos管mn7的漏端、nmos管mn6的栅端和nmos管mn15的漏端;

22、nmos管mn12的栅端接字线wlr,nmos管mn12的源端接位线blr,nmos管mn12的漏端同时接nmos管mn8的漏端、pmos管mp0的漏端、pmos管mp1的栅端、nmos管mn4的漏端和nmos管mn7的栅端;

23、nmos管mn13的栅端接字线wlr,nmos管mn13的源端接位线blnr,nmos管mn13的漏端同时接nmos管mn9漏端、pmos管mp2的栅端、pmos管mp1的漏端、nmos管mn4的栅端和nmos管mn5的漏端;

24、nmos管mn14的栅端接字线wlr,nmos管mn14的源端接位线blr,nmos管mn14的漏端同时接nmos管mn10的漏端、pmos管mp3的栅端、pmos管mp2的漏端、nmos管mn5的栅端和nmos管mn6的漏端;

25、nmos管mn15的栅端接字线wlr,nmos管mn15的源端接位线blnr,nmos管mn15的漏端接nmos管mn11的漏端、pmos管pm0的栅端、pmos管mp3的漏端、nmos管mn6的栅端和nmos管mn7的漏端。

26、在一种实施方式中,一列存储单元的四条位线采用blln\blrn\blnln\blnrn排列方式,其中位线blln和blnln采用同一层金属层m3布线,位线blrn和blnrn采用同一层金属层m4布线,金属层m3和金属层m4为相邻的金属层。

27、在一种实施方式中,所述左端口字线wlln采用金属层m2布线;所述右端口字线wlrn采用金属层m2布线。

28、本发明提供的一种抗辐射双端口16管存储单元阵列,执行双端口操作时,左右端口位线采用相邻金属层布线可以保障左、右端口通路信号传输的延时差较小。当执行一端口写操作而另一端口同时对相同列、相邻行的单元执行读操作时,左右端口位线采用相邻金属层布线,可以避免写通路位线上的强数据信号通过金属长导线间耦合电容串扰相邻的读通路位线上的弱数据信号而导致读取失效的现象。同一工艺节点在限定芯片面积的条件下,解决存储容量、存取速度与阵列面积之间的矛盾,避免双端口同时执行读写操作时发生位线信号串扰现象。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182368.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表