一种利用卤族钙钛矿阻变存储器件实现逻辑运算的方法与流程

- 国知局

- 2024-07-31 19:38:56

本发明属于非易失性半导体存储器领域,具体地,涉及一种利用阻变存储器件的制备及12种逻辑运算的实现方法。

背景技术:

1、阻变存储器(rram)因其架构简单、运行速度快、集成密度高、功耗低、阻变材料来源广泛而成为下一代非易失性存储器的有力竞争者。卤族钙钛矿因其明显的迟滞效应在阻变存储器件中的应用引起了极大的关注[j. phys. chem. lett. 2021, 12, 11673−11682]。

2、rram工作原理主要是在高低阻态之间切换实现“0”和“1”的互相转变,这个转变过程即为set和reset过程,set过程是指器件在外场激励下(如偏压)由高阻态(hrs)转变为低阻态(lrs),能使rram器件从hrs转变为lrs的电压为vset,reset过程是指器件在外场激励下(如偏压)由低阻态转变为高阻态,能使rram器件从lrs转变为hrs的电压为vreset,根据vset和vreset的极性可将器件分为单极性器件和双极性器件,即vset和vreset极性相同为单极性器件,vset和vreset极性相反为双极性器件。

3、利用rram的阻变特性可以用来设计逻辑电路,通过将输入信号转变为电信号,再通过电阻或者电流信号的变化可以体现阻态的变化,由此可以通过多个rram串联或者并联、搭配其他电子元件、合理设计外围辅助电路等方法即可实现特定的逻辑功能[phys.status solidi rrl 2023, 2300342]。然而,目前将rram用来设计逻电路大多需要多输入源(热、光、应力等)或者需要通过外围电路辅助实现逻辑运算[adv. electron. mater.2021, 2100366]。这将导致rram在实现逻辑操作时会面临着逻辑操作能耗高、步骤多、操作复杂、需要其他电子元件辅助、需要额外设计电路等问题。

4、近年,互补型阻变存储器(complementary resistive switch,crs)结构被提出[ieee transactions on nanotechnology, vol. 22, 2023],它由两个双极性阻变存储器背靠背串联为一个存储单元。互补型阻变存储器具有对称的iv曲线,器件的“0”和“1”都为高阻态,所以能够有效避免串扰电流,互补型阻变存储器没有外加整流器件,所以能够保持最小理论单元面积4f2。但是典型互补型阻变存储器是具有五层的存储单元结构,对制备工艺要求较高。另外,其具有破坏性且较为复杂的读取方式也影响了互补型阻变存储器的大规模应用。

技术实现思路

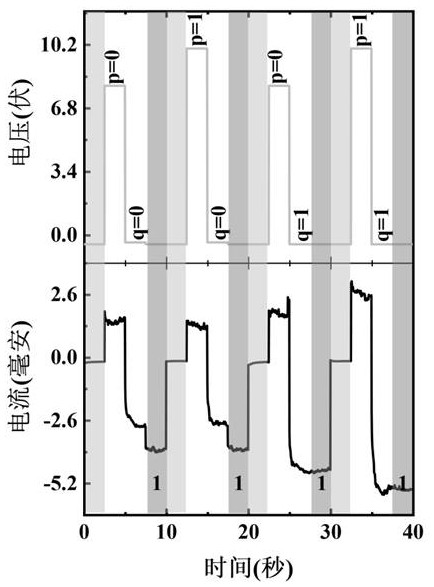

1、本发明目的在于提出一种利用卤族钙钛矿阻变存储器件实现逻辑运算的方法,通过单个rram器件实现12种逻辑运算。为实现这个目的,本发明通过在卤族钙钛矿rram器件基础上,通过界面调控得到一种具有类互补阻变特性的器件,它的特征在于一个存储单元内有两个背靠背的界面势垒串联,其典型i-v曲线如图1所示,i-v曲线不交叉,在正负两端都出现对称负微分阻变行为,基于具有这种特性的rram器件本发明使用电压信号作为唯一输入信号源实现12种逻辑运算操作。本发明所述的12种逻辑运算的实现仅依赖于电压操作而不需要外加物理场,仅需电信号作为输入源,且这些逻辑操作至多只需要两步逻辑操作,这将极大地简化逻辑电路、提高电路集成度、降低设计成本、拓展rram的应用领域,并将降低器件的功耗。

2、本发明是通过以下技术方案实现的。

3、本发明所述的卤族钙钛矿阻变存储器结构为电极ⅰ/卤族钙钛矿/电极ⅱ,通过界面调控使器件内存在两个对称的界面势垒,得到具有类互补阻变存储器,其i-v曲线表现出对称的负微分阻变现象。

4、所述的调控方法包括以下任意一种或其组合:(1)选择合适的材料组合:相邻结构选择两种能带结构差异较大的材料;(2)改变材料的晶格匹配度:相邻结构的两种材料选择晶格不匹配的材料;(3)改变界面的化学性质:在相邻结构的两种材料界面上引入化学修饰剂改变界面的化学性质;(4)控制材料的掺杂:在半导体材料中,通过控制相邻结构的两种材料掺杂水平,改变电子浓度;(5)插入界面调控材料:通过在相邻结构的两种材料之间插入界面调控材料控制界面的电子特性。

5、本发明所述的一种利用卤族钙钛矿阻变存储器件实现逻辑运算的方法,如下所述:设定逻辑运算信号p和q,p表示第一逻辑运算信号,q表示第二逻辑运算信号,p、q均为电压信号,根据电平高低区分为高电平“1”,低电平“0”,p、q可设定为不同幅值的“0”、“1”逻辑运算信号,p、q可设定为不同极性的逻辑运算信号。使用p0表示第一输入逻辑运算信号的低电平,使用p1表示第一输入逻辑运算信号的高电平,使用q0表示第二输入逻辑运算信号的低电平,使用q1表示第二输入逻辑运算信号的高电平。使用(p,q)来表示一对逻辑运算信号,具体如下。

6、(0,0)表示第一输入逻辑运算信号p为低电平,第二输入逻辑运算信号q为低电平。

7、(1,0)表示第一输入逻辑运算信号p为高电平,第二输入逻辑运算信号q为低电平。

8、(0,1)表示第一输入逻辑运算信号p为低电平,第二输入逻辑运算信号q为高电平。

9、(1,1)表示第一输入逻辑运算信号p为高电平,第二输入逻辑运算信号q为高电平。

10、将所述的卤族钙钛矿阻变存储器的电极ⅰ、电极ⅱ作为接入端口接入电路中,输入逻辑运算信号施加在电极ⅰ与电极ⅱ两电极端,读取信号为两电极端之间的电阻或电流幅值,读取信号即为逻辑运算结果。

11、依次输入合适的(0,0),(1,0),(0,1),(1,1),每次操作前都将卤族钙钛矿阻变存储器初始化为高阻态,设置一读取电压vread值,如0.4v~0.6v之间,每次操作结束后读取两电极端之间的电阻或电流幅值,读取电压的极性与q的极性一致,定义读取信号高阻态(小电流)为逻辑“0”,低阻态(大电流)为逻辑“1”。逻辑步骤计数表示完成该操作所需的步骤计数。按照以上操作即可完成以下逻辑运算:ture、false、p、notp、q、not q、and、rimp、nimp、nor、xor、xnor。

12、所述的ture逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0、p1极性相同,q0、q1极性相同,p、q极性相反。施加与q极性相同的读取信号,运算结果为“1”、“1”、“1”、“1”。即:

13、p0 ture q0 = 1;

14、p1 ture q0 = 1;

15、p0 ture q1 = 1;

16、p1 ture q1 = 1;

17、逻辑步骤计数为2。

18、所述的false逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0、p1极性相同,q0、q1极性相同,p、q极性相同。施加与q极性相同的读取信号,运算结果为“0”、“0”、“0”、“0”。即:

19、p0 false q0 = 0;

20、p1 false q0 = 0;

21、p0 false q1 = 0;

22、p1 false q1 = 0;

23、逻辑步骤计数为1。

24、所述的p逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值小于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0与p1极性相反,q0与q1极性相同,p0与q极性相同。施加与q极性相同的读取信号,运算结果为“0”、“1”、“0”、“1”。即:

25、p0 p q0 = 0;

26、p1 p q0 =1;

27、p0 p q1 = 0;

28、p1 p q1 = 1;

29、逻辑步骤计数为2。

30、所述的not p逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0与p1极性相反,q0与q1极性相同,p0与q极性相反。施加与q极性相同的读取信号,运算结果为“1”、“0”、“1”、“0”。即:

31、p0 not p q0 = 1;

32、p1 not p q0 = 0;

33、p0 not p q1 = 1;

34、p1 not p q1 = 0;

35、逻辑步骤计数为2。

36、所述的q逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0与p1极性相同,q0与q1极性相反,p0与q0极性相同。施加与q极性相同的读取信号,运算结果为“0”、“0”、“1”、“1”。即:

37、p0 q q0 = 0;

38、p1 q q0 = 0;

39、p0 q q1 = 1;

40、p1 q q1 = 1;

41、逻辑步骤计数为2。

42、所述的not q逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值大于vset的电压,p0与p1极性相同,q0与q1极性相同,p0与q0极性相反。施加与q极性相同的读取信号,运算结果为“1”、“1”、“0”、“0”。即:

43、p0 not q q0 = 1;

44、p1 not q q0 = 1;

45、p0 not q q1 = 0;

46、p1 not q q1 = 0;

47、逻辑步骤计数为2。

48、所述的and逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值小于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0与p1极性相反,q0与q1极性相反,p0与q0极性相反。施加与q极性相同的读取信号,运算结果为“0”、“0”、“0”、“1”。即:

49、p0 and q0 = 0;

50、p1 and q0 = 0;

51、p0 and q1 = 0;

52、p1 and q1 = 1;

53、逻辑步骤计数为2。

54、所述的rimp逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0与p1极性相反,q0与q1极性相同,p0与q0极性相同。施加与q极性相同的读取信号,运算结果为“0”、“1”、“0”、“1”。即:

55、p0 rimp q0 = 0;

56、p1 rimp q0 = 1;

57、p0 rimp q1 = 0;

58、p1 rimp q1 = 1;

59、逻辑步骤计数为2。

60、所述的nimp逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值小于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值大于vset的电压,p0与p1极性相反,q0与q1极性相同,p0与q0极性相同。施加与q极性相同的读取信号,运算结果为“0”、“1”、“0”、“0”。即:

61、p0 nimp q0 = 0;

62、p1 nimp q0 = 1;

63、p0 nimp q1 = 0;

64、p1 nimp q1 = 0;

65、逻辑步骤计数为2。

66、所述的nor逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值大于vset的电压,p0与p1极性相反,q0与q1极性相同,p0与q0极性相反。施加与q极性相同的读取信号,运算结果为“1”、“0”、“0”、“0”。即:

67、p0 nor q0 = 1;

68、p1 nor q0 = 0;

69、p0 nor q1 = 0;

70、p1 nor q1 = 0;

71、逻辑步骤计数为2。

72、所述的xor逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0与p1极性相反,q0与q1极性相反,p0与q0极性相同。施加与q极性相同的读取信号,运算结果为“0”、“1”、“1”、“0”。即:

73、p0 xor q0 = 0;

74、p1 xor q0 = 1;

75、p0 xor q1 = 1;

76、p1 xor q1 = 0;

77、逻辑步骤计数为2。

78、所述的xnor逻辑运算实现方法:依次输入(0,0)(1,0)(0,1)(1,1),其中p0为幅值大于vset的电压,p1为幅值大于vset的电压,q0为幅值小于vset的电压,q1为幅值小于vset的电压,p0与p1极性相反,q0与q1极性相反,p0与q0极性相反。施加与q极性相同的读取信号,运算结果为“1”、“0”、“0”、“1”。即:

79、p0 xnor q0 = 1;

80、p1 xnor q0 = 0;

81、p0 xnor q1 = 0;

82、p1 xnor q1 = 1;

83、逻辑步骤计数为2。

84、本发明的有益效果是:现有技术中利用阻变存储器实现逻辑运算的操作,大多需要通过加入其他电子元件、外围电路、其他物理场(光、热等)辅助实现,这样增加了设计复杂度及成本、降低了器件的集成度,同时也增加了器件运行的功耗。本发明只需两个输入信号,无需引入其他电子元件、外围电路及其他物理场(光、热等),通过单一器件实现12种逻辑运算,所有逻辑运算至多两步,因而本发明能够促进阻变存储器的实用化进程,极大丰富其应用场景,对阻变存储器实现存算一体具有重要意义。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183402.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表