一种高稳定性的低功耗SRAM电路

- 国知局

- 2024-07-31 19:51:28

本发明涉及集成电路设计和存储,具体地,涉及一种高稳定性的低功耗sram电路。

背景技术:

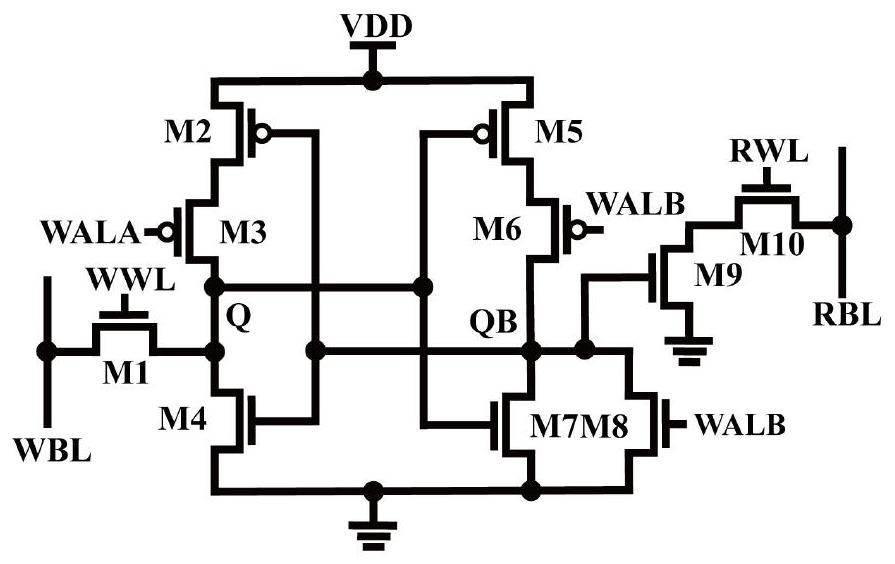

1、静态随机存储器(static random access memory,sram)是一种常见的半导体存储器类型,用于集成电路中存储和读取数据。如图1,sram的基本存储单元通常由六个晶体管构成,每个存储单元可以存储一个比特(0或1),sram的读写操作是通过控制各个晶体管的通断状态来实现的,相比其他存储器,sram具有较快的访问速度与较高的稳定性,且无需刷新操作。

2、近年来,便携式设备的热度急速增长,导致对系统级芯片(system on a chip,soc)的需求显著增加。soc具有功耗低、体积小的特点,可以延长便携式设备的使用时间和电池的使用寿命,这对于户外设备和可植入的生物医学仪器等应用至关重要。sram具有读写速度快、功耗低等优点,已成为soc的重要组成部分。目前,传统的六个晶体管的存储单元结构中,读取和写入操作会引起位线的充电和放电,消耗较多的功耗,通过降低供电电压,可以减少充放电过程中的能量消耗,然而,降低供电电压也会引入一些挑战,如:稳定性问题和读写性能下降。因此,如何在降低功耗的同时保证sram的性能与稳定性是目前急需解决的问题。

技术实现思路

1、针对现有技术中存在的问题,本发明提供了一种高稳定性的低功耗sram电路,弥补sram电路在低功耗应用场景下性能与稳定性较差的情况。

2、为实现上述技术目的,本发明采用如下技术方案:一种高稳定性的低功耗sram电路,由第一nmos晶体管m1、第二nmos晶体管m4、第三nmos晶体管m7、第一pmos晶体管m2、第二pmos晶体管m5、功率门控结构、辅助放电nmos晶体管m8、读解耦电路、写字线wwl、读字线rwl、写位线wbl、读位线rbl、第一写辅助线wala和第二写辅助线walb组成,所述功率门控结构分别与第一写辅助线wala、第二写辅助线walb、第一nmos晶体管m1、第一pmos晶体管m2、第二pmos晶体管m5、第二nmos晶体管m4、第三nmos晶体管m7、辅助放电nmos晶体管m8、读解耦电路连接,所述辅助放电nmos晶体管m8还分别与第二写辅助线walb、读解耦电路连接,所述读解耦电路还与读位线rbl连接;所述第一nmos晶体管m1还分别与写字线wwl、写位线wbl连接。

3、进一步地,所述功率门控结构由第三pmos晶体管m3和第四nmos晶体管m6组成,所述第三pmos晶体管m3的栅极与第一写辅助线wala连接,所述第三pmos晶体管m3的源极与第一pmos晶体管m2的漏极连接,所述第三pmos晶体管m3的漏极分别与第二nmos晶体管m4漏极、第一nmos晶体管m1的源极、第二pmos晶体管m5的栅极、第三nmos晶体管m7的栅极连接;所述第四nmos晶体管m6的栅极与第二辅助线walb连接,所述第四nmos晶体管m6的源极与第二pmos晶体管m5的漏极连接,所述第四nmos晶体管m6的漏极分别与第三nmos晶体管m7的漏极、第一pmos晶体管m2的栅极、第二nmos晶体管m4的栅极、辅助放电nmos晶体管m8的漏极、读解耦电路连接。

4、进一步地,所述第一pmos晶体管m2的源极、第二pmos晶体管m5的源极均与供电电压vdd连接。

5、进一步地,所述供电电压vdd设置为近阈值。

6、进一步地,所述第二nmos晶体管m4的源极、第三nmos晶体管m7的源极、辅助放电nmos晶体管m8的源极均接地。

7、进一步地,所述第一nmos晶体管m1的栅极与写字线wwl连接,所述第一nmos晶体管m1的漏极与写位线wbl连接。

8、进一步地,所述读解耦电路由第五nmos晶体管m9和第六nmos晶体管m10组成,所述第五nmos晶体管m9的栅极分别与第一pmos晶体管m2的栅极、第二nmos晶体管m4的栅极、第四nmos晶体管m6的漏极、第三nmos晶体管m7的漏极、辅助放电nmos晶体管m8的漏极连接,所述第五nmos晶体管m9的源极接地,所述第五nmos晶体管m9的漏极与第六nmos晶体管m10的源极连接,所述第五nmos晶体管m9的栅极与读字线rwl连接,所述第五nmos晶体管m9的源极与读位线rbl连接。

9、进一步地,当低功耗sram电路的控制信号为写“0”时,将写字线wwl的信号、读位线rbl的信号、第一写辅助线wala的信号均置于高电平,读字线rwl的信号、写位线wbl的信号、第二写辅助线walb的信号均置于低电平;当低功耗sram电路的控制信号为写“1”时,将写字线wwl的信号、写位线wbl的信号、读位线rbl的信号、第二写辅助线walb的信号均置于高电平,读字线rwl的信号、第一写辅助线wala的信号均置于低电平。

10、进一步地,当低功耗sram电路的控制信号为读时,对读位线rbl的信号进行预充电至高电平,将读字线rwl的信号、写位线wbl的信号置于高电平,将写字线wwl的信号、第一写辅助线wala的信号、第二写辅助线walb的信号置于低电平。

11、进一步地,当低功耗sram电路的控制信号为保持时,将写位线wbl的信号置于高电平,将写字线wwl的信号、读字线rwl的信号、第一写辅助线wala的信号、第二写辅助线walb的信号置于低电平。

12、与现有技术相比,本发明具有如下有益效果:本发明高稳定性的低功耗sram电路在功率门控结构与放电nmos晶体管m8的帮助下优化了存储单元的综合性能与稳定性,解决了性能与稳定性不可兼得的问题,同时降低了sram电路的复杂度,避免晶体管数量过多的问题;此外,本发明还通过将供电电压vdd设置为近阈值以及单端读/写电路,有效降低了读/写过程中的能源损耗;此外,本发明的控制信号简单、功耗低,避免信号延时对读、写速率产生不必要的影响,且无需额外的外围电路辅助读/写操作。

技术特征:1.一种高稳定性的低功耗sram电路,其特征在于,由第一nmos晶体管m1、第二nmos晶体管m4、第三nmos晶体管m7、第一pmos晶体管m2、第二pmos晶体管m5、功率门控结构、辅助放电nmos晶体管m8、读解耦电路、写字线wwl、读字线rwl、写位线wbl、读位线rbl、第一写辅助线wala和第二写辅助线walb组成,所述功率门控结构分别与第一写辅助线wala、第二写辅助线walb、第一nmos晶体管m1、第一pmos晶体管m2、第二pmos晶体管m5、第二nmos晶体管m4、第三nmos晶体管m7、辅助放电nmos晶体管m8、读解耦电路连接,所述辅助放电nmos晶体管m8还分别与第二写辅助线walb、读解耦电路连接,所述读解耦电路还与读位线rbl连接;所述第一nmos晶体管m1还分别与写字线wwl、写位线wbl连接。

2.根据权利要求1所述的一种高稳定性的低功耗sram电路,其特征在于,所述功率门控结构由第三pmos晶体管m3和第四nmos晶体管m6组成,所述第三pmos晶体管m3的栅极与第一写辅助线wala连接,所述第三pmos晶体管m3的源极与第一pmos晶体管m2的漏极连接,所述第三pmos晶体管m3的漏极分别与第二nmos晶体管m4漏极、第一nmos晶体管m1的源极、第二pmos晶体管m5的栅极、第三nmos晶体管m7的栅极连接;所述第四nmos晶体管m6的栅极与第二辅助线walb连接,所述第四nmos晶体管m6的源极与第二pmos晶体管m5的漏极连接,所述第四nmos晶体管m6的漏极分别与第三nmos晶体管m7的漏极、第一pmos晶体管m2的栅极、第二nmos晶体管m4的栅极、辅助放电nmos晶体管m8的漏极、读解耦电路连接。

3.根据权利要求2所述的一种高稳定性的低功耗sram电路,其特征在于,所述第一pmos晶体管m2的源极、第二pmos晶体管m5的源极均与供电电压vdd连接。

4.根据权利要求3所述的一种高稳定性的低功耗sram电路,其特征在于,所述供电电压vdd设置为近阈值。

5.根据权利要求2所述的一种高稳定性的低功耗sram电路,其特征在于,所述第二nmos晶体管m4的源极、第三nmos晶体管m7的源极、辅助放电nmos晶体管m8的源极均接地。

6.根据权利要求2所述的一种高稳定性的低功耗sram电路,其特征在于,所述第一nmos晶体管m1的栅极与写字线wwl连接,所述第一nmos晶体管m1的漏极与写位线wbl连接。

7.根据权利要求2所述的一种高稳定性的低功耗sram电路,其特征在于,所述读解耦电路由第五nmos晶体管m9和第六nmos晶体管m10组成,所述第五nmos晶体管m9的栅极分别与第一pmos晶体管m2的栅极、第二nmos晶体管m4的栅极、第四nmos晶体管m6的漏极、第三nmos晶体管m7的漏极、辅助放电nmos晶体管m8的漏极连接,所述第五nmos晶体管m9的源极接地,所述第五nmos晶体管m9的漏极与第六nmos晶体管m10的源极连接,所述第五nmos晶体管m9的栅极与读字线rwl连接,所述第五nmos晶体管m9的源极与读位线rbl连接。

8.根据权利要求1所述的一种高稳定性的低功耗sram电路,其特征在于,当低功耗sram电路的控制信号为写“0”时,将写字线wwl的信号、读位线rbl的信号、第一写辅助线wala的信号均置于高电平,读字线rwl的信号、写位线wbl的信号、第二写辅助线walb的信号均置于低电平;当低功耗sram电路的控制信号为写“1”时,将写字线wwl的信号、写位线wbl的信号、读位线rbl的信号、第二写辅助线walb的信号均置于高电平,读字线rwl的信号、第一写辅助线wala的信号均置于低电平。

9.根据权利要求1所述的一种高稳定性的低功耗sram电路,其特征在于,当低功耗sram电路的控制信号为读时,对读位线rbl的信号进行预充电至高电平,将读字线rwl的信号、写位线wbl的信号置于高电平,将写字线wwl的信号、第一写辅助线wala的信号、第二写辅助线walb的信号置于低电平。

10.根据权利要求1所述的一种高稳定性的低功耗sram电路,其特征在于,当低功耗sram电路的控制信号为保持时,将写位线wbl的信号置于高电平,将写字线wwl的信号、读字线rwl的信号、第一写辅助线wala的信号、第二写辅助线walb的信号置于低电平。

技术总结本发明公开了一种高稳定性的低功耗SRAM电路,由第一NMOS晶体管、第二NMOS晶体管、第三NMOS晶体管、第一PMOS晶体管、第二PMOS晶体管、功率门控结构、辅助放电NMOS晶体管、读解耦电路、写字线、读字线、写位线、读位线、第一写辅助线和第二写辅助线组成,功率门控结构分别与第一写辅助线、第二写辅助线、第一NMOS晶体管、第一PMOS晶体管、第二PMOS晶体管、第二NMOS晶体管、第三NMOS晶体管、辅助放电NMOS晶体管、读解耦电路连接,辅助放电NMOS晶体管还分别与第二写辅助线、读解耦电路连接,读解耦电路还与读位线连接;第一NMOS晶体管还分别与写字线、写位线连接。本发明弥补SRAM电路在低功耗应用场景下性能与稳定性较差的情况。技术研发人员:王佑,徐叶帆,刘伟强受保护的技术使用者:南京航空航天大学技术研发日:技术公布日:2024/4/24本文地址:https://www.jishuxx.com/zhuanli/20240731/184375.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。