多数据块联合LDPC编码的数据存储方法与系统与流程

- 国知局

- 2024-07-31 19:53:05

本发明涉及数据存储,具体而言,涉及一种多数据块联合ldpc编码的数据存储方法与系统。

背景技术:

1、在大数据时代,存储系统中的数据呈爆炸式增长。另一方面,为了提升存储效率,存储介质尺寸在逐渐减小,单位面积内的比特密度在逐渐增加。因此,数据存储的可靠性问题日益突出,影响存储系统的使用寿命。

2、纠错编码技术为提高数据存储系统可靠性的有效手段之一。ldpc码是一类由稀疏校验矩阵定义的纠错编码。在码长较长的条件下,ldpc码具有接近香农理论极限的纠错性能,在数据存储中得到了广泛应用。

3、对于数据存储系统,不同数据块所在的存储区域(例如闪存的不同页) 通常具有不同的数据错误率。这一数据错误率的不平衡性对存储系统性能造成严重影响,然而现有技术在设计纠错编码方案时通常没有考虑这一影响。

技术实现思路

1、本发明的主要目的在于提供一种多数据块联合ldpc编码的数据存储方法与系统,以至少解决现有技术中在设计纠错编码方案时没有考虑数据错误率的不平衡性对存储系统的可靠性造成影响的问题。

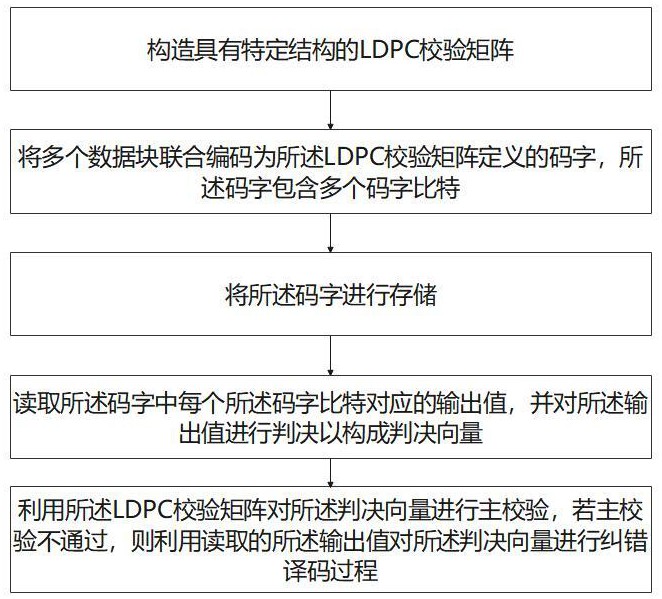

2、为了实现上述目的,根据本发明的一个方面,提供了一种多数据块联合ldpc编码的数据存储方法,包括:构造具有特定结构的ldpc校验矩阵;将多个数据块联合编码为ldpc校验矩阵定义的码字,码字包含多个码字比特;将码字进行存储;读取码字中每个码字比特对应的输出值,并对输出值进行判决以构成判决向量;利用ldpc校验矩阵对判决向量进行主校验,若主校验不通过,则利用读取的输出值对判决向量进行纠错译码过程。

3、进一步地,具有特定结构的ldpc校验矩阵由第一子矩阵和第二子矩阵构成;第一子矩阵为分块对角矩阵,第一子矩阵由多个位于对角线上的非零子块构成,非零子块的数目等于联合编码的数据块的数目,每个非零子块对应于一个数据块编码后得到的码字比特;第二子矩阵对应于多个数据块联合编码后得到的码字。

4、进一步地,判决向量为二进制向量,判决向量由多个码字比特的判决值构成,对输出值进行判决的方法为将每个码字比特对应的输出值与一个预先设定的门限值进行比较,若输出值大于门限值,则码字比特的判决值为1,若输出值不大于门限值,则码字比特的判决值为0。

5、进一步地,利用ldpc校验矩阵对判决向量进行主校验的方法为将ldpc校验矩阵与判决向量进行模2乘法以得到主校验向量,若主校验向量为全零向量,则校验通过,若主校验向量不为全零向量,则校验不通过。

6、进一步地,纠错译码过程包括:设置主最大迭代次数;对判决向量进行第一子迭代过程以进行第一阶段纠错;对判决向量进行第二子迭代过程以进行第二阶段纠错;重复第一子迭代过程和第二子迭代过程直到纠错后的判决向量通过主校验或者纠错译码过程的迭代次数达到主最大迭代次数。

7、进一步地,第一子迭代过程包括:设置第一子最大迭代次数,对每个数据块均设置一个标志位,初始时每个标志位都置为1;利用第一子矩阵中的非零子块对数据块对应的判决值进行第一子校验,若通过第一子校验则将数据块的标志位置为0;对未通过第一子校验的判决值进行纠错;直到纠错后的判决值通过第一子校验或第一子迭代过程的迭代次数达到第一子最大迭代次数。

8、进一步地,第一子校验的方法为将非零子块与数据块对应的判决值进行模2乘法以得到第一子校验向量,若第一子校验向量为全零向量,则校验通过,若第一子校验向量不为全零向量,则校验不通过。

9、进一步地,第二子迭代过程包括:设置第二子最大迭代次数;利用第二子矩阵对判决向量进行第二子校验,若第二子校验不通过则对判决向量进行纠错,直到纠错后的判决向量通过第二子校验或第二子迭代过程的迭代次数达到第二子最大迭代次数。

10、进一步地,第二子校验的方法为将第二子矩阵与判决向量进行模2乘法以得到第二子校验向量,若第二子校验向量为全零向量,则校验通过,若第二子校验向量不为全零向量,则校验不通过。

11、根据本发明的另一方面,还提供了一种多数据块联合ldpc编码的数据存储系统,多数据块联合ldpc编码的数据存储系统应用于多数据块联合ldpc编码的数据存储方法,多数据块联合ldpc编码的数据存储系统包括:矩阵构造模块、数据编码模块、数据存储模块、数据读取模块、数据判决模块、数据校验模块和纠错译码模块;矩阵构造模块用于构造具有特定结构的ldpc校验矩阵;数据编码模块用于将多个数据块联合编码为ldpc校验矩阵定义的码字,码字包含多个码字比特;数据存储模块用于将码字进行存储;数据读取模块用于读取码字中每个码字比特对应的输出值;数据判决模块用于对输出值进行判决以构成判决向量;数据校验模块用于利用ldpc校验矩阵对判决向量进行主校验;纠错译码模块用于利用读取的输出值对判决向量进行纠错译码过程。

12、本发明技术方案提供了一种多数据块联合ldpc编码的数据存储方法与系统,多数据块联合ldpc编码的数据存储方法,包括:构造具有特定结构的ldpc校验矩阵;将多个数据块联合编码为ldpc校验矩阵定义的码字,码字包含多个码字比特;将码字进行存储;读取码字中每个码字比特对应的输出值,并对输出值进行判决以构成判决向量;利用ldpc校验矩阵对判决向量进行主校验,若主校验不通过,则利用读取的输出值对判决向量进行纠错译码过程。本发明给出的方法可以有效抑制存储系统不同数据块所在存储区域具有不同数据错误率造成的影响,译码收敛速度快,译码后错误平台低,是实际数据存储的良好选择。

技术特征:1.一种多数据块联合ldpc编码的数据存储方法,其特征在于,包括:

2.根据权利要求1所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述具有特定结构的ldpc校验矩阵由第一子矩阵和第二子矩阵构成;所述第一子矩阵为分块对角矩阵,所述第一子矩阵由多个位于对角线上的非零子块构成,所述非零子块的数目等于联合编码的所述数据块的数目,每个所述非零子块对应于一个所述数据块编码后得到的所述码字比特;所述第二子矩阵对应于多个所述数据块联合编码后得到的所述码字。

3.根据权利要求2所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述判决向量为二进制向量,所述判决向量由多个所述码字比特的判决值构成,对所述输出值进行判决的方法为将每个所述码字比特对应的输出值与一个预先设定的门限值进行比较,若所述输出值大于所述门限值,则所述码字比特的判决值为1,若所述输出值不大于所述门限值,则所述码字比特的判决值为0。

4.根据权利要求1所述的多数据块联合ldpc编码的数据存储方法,其特征在于,利用所述ldpc校验矩阵对所述判决向量进行主校验的方法为将所述ldpc校验矩阵与所述判决向量进行模2乘法以得到主校验向量,若所述主校验向量为全零向量,则校验通过,若所述主校验向量不为全零向量,则校验不通过。

5.根据权利要求3所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述纠错译码过程包括:

6.根据权利要求5所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述第一子迭代过程包括:

7.根据权利要求6所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述第一子校验的方法为将所述非零子块与所述数据块对应的所述判决值进行模2乘法以得到第一子校验向量,若所述第一子校验向量为全零向量,则校验通过,若所述第一子校验向量不为全零向量,则校验不通过。

8.根据权利要求5所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述第二子迭代过程包括:

9.根据权利要求8所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述第二子校验的方法为将所述第二子矩阵与所述判决向量进行模2乘法以得到第二子校验向量,若所述第二子校验向量为全零向量,则校验通过,若所述第二子校验向量不为全零向量,则校验不通过。

10.一种多数据块联合ldpc编码的数据存储系统,所述多数据块联合ldpc编码的数据存储系统应用于如权利要求1至9任一项所述的多数据块联合ldpc编码的数据存储方法,其特征在于,所述多数据块联合ldpc编码的数据存储系统包括:

技术总结本发明提供了一种多数据块联合LDPC编码的数据存储方法与系统,涉及数据存储技术领域,多数据块联合LDPC编码的数据存储方法包括:构造具有特定结构的LDPC校验矩阵;将多个数据块联合编码为LDPC校验矩阵定义的码字,码字包含多个码字比特;将码字进行存储;读取码字中每个码字比特对应的输出值,并对输出值进行判决以构成判决向量;利用LDPC校验矩阵对判决向量进行主校验,若主校验不通过,则利用读取的输出值对判决向量进行纠错译码过程。本发明给出的方法可以有效抑制存储系统不同数据块所在存储区域具有不同数据错误率造成的影响,译码收敛速度快,译码后错误平台低,是实际数据存储的良好选择。技术研发人员:吴福,徐斌受保护的技术使用者:陕西中安数联信息技术有限公司技术研发日:技术公布日:2024/5/8本文地址:https://www.jishuxx.com/zhuanli/20240731/184500.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表