设备阵列的数据同步传输方法、装置和可读存储介质与流程

- 国知局

- 2024-07-31 22:36:54

本技术涉及电子,尤其涉及一种设备阵列的数据同步传输方法、装置和可读存储介质。

背景技术:

1、随着电子技术的不断发展,在不同设备(或者模块)之间进行大规模数据传输的需求越来越多,同时在大规模数据传输的工业应用场景中存在数据分布在多个设备进行先期处理,然后汇聚到某个设备进行集中处理的情况,通常在这种情况的数据处理中需要对数据同步有高精度的要求。然而,在大规模设备阵列(一般为数字阵列)的数据传输与控制过程中,由于时钟、物理链路、控制信号等诸多因素的影响,大规模设备阵列的数据传输中多通道传输的数据之间存在着大小不一的延时,这些延时造成的偏移可能达到毫秒甚至秒级,远远超出数据传输的接收设备进行数据处理的同步需求,当设备阵列中设备的数量达到一定数量(如百甚至万级别)时,多通道之间的数据同步变成亟待解决的难题之一。

2、本技术的发明人在研究和实践过程中发现,现有技术中,为了在数据传输的接收端去掉多通道传输时通道之间的延时差(即去偏斜),通常是在每一条通道的数据流中周期性地插入了对齐标记,这些对齐标记在同一时刻插入所有的通道。在接收端,接收设备通过状态机对对齐标记进行锁定后,在多通道之间消除延时差(即去偏斜操作)。然而,通常接收设备对多通道之间进行去偏斜操作时是在每条通道的接收端加入缓存,并在每个缓存都有有效数据后,开始输出所有通道的数据。然而,现有技术通过去偏斜操作的方法消除多通道之间的延时差,需要在接收端的每个接收设备中做复杂的状态机,并且用缓存吸收不同通道之间的延时,当通道数量达到万级时,做状态机以及用缓存吸收延时的功能实现将占用相当大的电路面积,操作复杂且接收设备的体积大,适用性差。

技术实现思路

1、本技术提供了一种设备阵列的数据同步传输方法、装置和可读存储介质,可提高数据同步传输的控制便捷性,结构简单,适用性强。

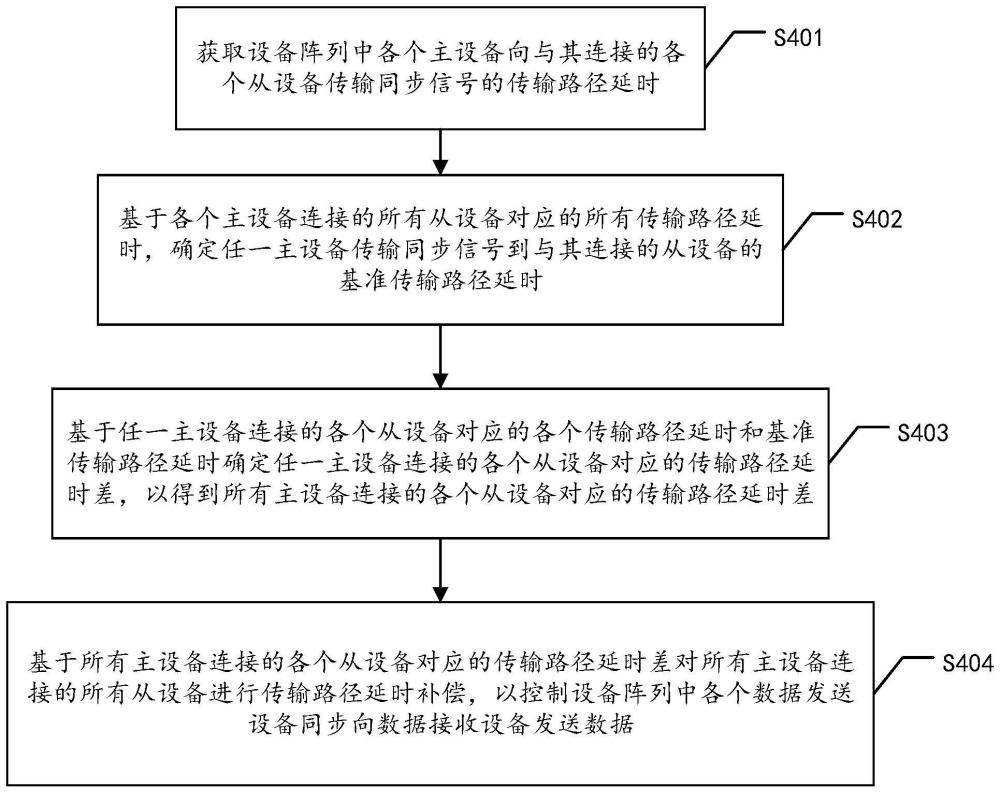

2、第一方面,本技术提供了一种设备阵列的数据同步传输方法,该设备阵列中主设备和从设备构成多层树状结构,在该多层树状结构中每一层的设备作为主设备连接下一层的多个从设备,该多层树状结构中最后一层的设备为数据发送设备。该方法包括:获取设备阵列中各个主设备向与其连接的各个从设备传输同步信号的传输路径延时,其中,任一主设备传输同步信号至与其连接的一个从设备对应一个传输路径延时;基于各个主设备连接的所有从设备对应的所有传输路径延时,确定任一主设备传输同步信号到与其连接的从设备的基准传输路径延时,并基于任一主设备连接的各个从设备对应的各个传输路径延时和基准传输路径延时确定任一主设备连接的各个从设备对应的传输路径延时差,以此得到所有主设备连接的各个从设备对应的传输路径延时差。进一步的,基于所有主设备连接的各个从设备对应的传输路径延时差可对所有主设备连接的所有从设备进行传输路径延时补偿,从而可以控制上述设备阵列中各个上述数据发送设备同步向数据接收设备发送数据。在本技术中,通过主设备和从设之间的传输路径的延时补偿可控制作为数据发送设备的最后一层从设备同步向数据接收设备发送数据,可提高数据同步传输的控制便捷性,结构简单,适用性强。

3、结合第一方面,在第一种可能的实施方式中,获取设备阵列中各个主设备向与其连接的各个从设备传输同步信号的传输路径延时包括:获取设备阵列中任一主设备向与其连接的任一从设备传输第一同步信号的线路延时,并获取任一主设备和任一从设备使用同频时钟对第一同步信号进行信号检测的时钟相位差;基于上述时钟相位差和上述线路延时获得任一主设备向任一从设备传输第一同步信号的传输路径延时,以得到设备阵列中各个主设备向与其连接的各个从设备传输同步信号的传输路径延时。在本技术中,基于各个主设备和从设备的线路延时和时钟相位差可以获得各个主设备和从设备之间的同步信号传输的传输路径延时,从而可基于该传输路径延时实现主设备和从设备之间的传输路径的延时补偿,每个主设备和从设备之间的传输路径的延时均可得以补偿,从而可实现设备阵列中数据发送设备发送数据的同步触发,延时补偿的精度控制准确率高,操作简单,适用性强。

4、结合第一方面第一种可能的实现方式,在第二种可能的实现方式中,获取设备阵列中任一主设备向与其连接的任一从设备传输第一同步信号的线路延时的过程中可首先获取设备阵列中任一主设备向与其连接的任一从设备输出第一同步信号的第一输出延时,并获取第一同步信号传输至任一从设备并从任一从设备回传至上述任一主设备的第一时长。其次,可获取任一从设备向任一主设备回传第一同步信号的第二输出延时和第一同步信号在任一从设备中停留的第二时长。最后,可基于上述第一输出延时、上述第一时长、上述第二输出延时和上述第二时长获得上述任一主设备和上述任一从设备之间的线路延时。在本技术中,基于任一主设备输出同步信号的延时和任一从设备输出同步信号的延时,结合同步信号在任一主设备和任一从设备之间传输和停留的时长来计算任一主设备和任一从设备之间的线路延时,可兼顾不同主设备和不同从设备之间信号传输的差异性,提高设备阵列中数据发送设备同步传输数据的控制精度,操作简单,适用性强。

5、结合第一方面第二种可能的实现方式,在第三种可能的实现方式中,设备阵列中主设备中包括同步信号传输单元、第一输出接口、第一输入接口和时钟计数器;获取设备阵列中任一主设备向与其连接的任一从设备输出第一同步信号的第一输出延时包括:首先通过任一主设备中的同步信号传输单元同时向时钟计数器和任一主设备连接的任一从设备发送第一测量同步信号,触发时钟计数器开始计数并获取第一测量同步信号通过第一输入接口返回并触发时钟计数器停止计数时时钟计数器的第一计数。此外,可按照第一延时步进调整同步信号传输单元通过第一输出接口输出同步信号的输出延时并向任一从设备发送第二测量同步信号,同时触发时钟计数器开始计数(其中第二测量同步信号传输到时钟计数器时,时钟计数器开始计数),并在监测到第二测量同步信号返回并触发时钟计数器停止计数时且时钟计数器的计数比上述第一计数增加1时,获得调整后的同步信号传输单元通过第一输出接口输出同步信号的输出延时,以作为上述任一主设备向上述任一从设备输出第一同步信号的第一输出延时。在本技术中,可以以极小的延时步调整主设备输出同步信号的延时,使得时钟计数器的计数比未调整主设备输出同步信号的延时之前计数增加1,可以使得从设备接收的同步信号沿与从设备检测同步信号的时钟沿基本对齐(从设备接收的同步信号沿和时钟沿相差小于或者等于延时步进的时间),可提高主设备和从设备之间信号传输的线路延时的控制精度,适用性强。

6、结合第一方面第三种可能的实现方式,在第四种可能的实现方式中,上述获取任一从设备向任一主设备回传上述第一同步信号的第二输出延时包括:首先,按照上述第一输出延时配置上述任一主设备向上述任一从设备输出同步信号的输出延时,并通过任一主设备的第一输出接口向上述任一从设备发送第一同步信号,同时触发上述任一主设备中时钟计数器开始计数并记录时钟计数器的计数为第二计数。此外,按照第二延时步进调整上述任一从设备向上述任一主设备回传同步信号的输出延时并通过上述任一从设备的第二输出接口向上述任一主设备回传上述第一同步信号,在监测到上述时钟计数器的上述第二计数增加1时,获得调整后上述任一从设备向上述任一主设备输出同步信号的输出延时,以作为上述任一从设备向上述任一主设备回传上述第一同步信号的第二输出延时。在本技术中,同样的,针对从设备的同步信号输出,也可以以极小的延时步调整从设备输出同步信号的延时,使得时钟计数器的计数比未调整从设备输出同步信号的延时之前计数增加1,可以提高主设备和从设备之间信号传输的线路延时的控制精度,适用性强。

7、结合第一方面第四种可能的实现方式,在第五种可能的实现方式中,上述获取第一同步信号传输至任一从设备并从任一从设备回传至任一主设备的第一时长包括:首先,通过任一主设备中的同步信号传输单元向时钟计数器发送第一同步信号以触发时钟计数器开始计数,同时通过第一输出接口基于第一输出延时向任一从设备发送第一同步信号。进一步的,可获取第一同步信号通过任一从设备和第一输入接口返回并触发时钟计数器停止计数时时钟计数器的第三计数,将第三计数对应的时钟周期确定为第一同步信号传输至任一从设备并从任一从设备回传至任一主设备的第一时长。在本技术中,同步信号从主设备的同步信号传输单元发出,同步信号达到从设备之后分为两路,一路经由从设备返回主设备,另一路作为同步信号传输至下一层从设备。通过主设备中的时钟计数器的计数可获得同步信号从主设备发出到返回主设备之间的时长,可用于计算主设备和从设备之间的同步信号传输的线路延时,操作简单,可行性强。

8、结合第一方面第五种可能的实现方式,在第六种可能的实现方式中,设备阵列中从设备中包括第二输入接口、同步信号检测单元、多个寄存器和第二输出接口;上述获取第一同步信号在任一从设备中停留的第二时长,包括:当同步信号检测单元检测到通过第二输入接口输入的第一同步信号时,通过多个寄存器打拍后通过第二输出接口向任一主设备回传第一同步信号,并将上述多个寄存器打拍对应的时钟周期确定为第一同步信号在任一从设备中停留的第二时长。在本技术中,通过从设备中的多个寄存器打拍之后回传同步信号至主设备,可提高同步信号在从设备中停留的时长的计算准确性,操作简单,适用性强。

9、结合第一方面第一种可能的实现方式至第一方面第六种可能的实现方式中任一种,在第七种可能的实现方式中,上述获取任一主设备和任一从设备使用同频时钟对第一同步信号进行信号检测的时钟相位差包括:首先,基于任一主设备向任一从设备传输第一同步信号的线路延时和上述同频时钟的时钟周期获得参考线路延时;之后,基于上述参考线路延时、任一主设备向任一从设备输出第一同步信号的第一输出延时和上述时钟周期的周期时长,获得任一主设备和任一从设备使用同频时钟对第一同步信号进行信号检测的时钟相位差。在本技术中,任一主设备和任一从设备使用同频时钟对第一同步信号进行信号检测的时钟相位差的计算简单,提高了任一主设备和任一从设备之间传输同步信号的传输路径延时的操作便捷性。

10、结合第一方面第一种可能的实现方式至第一方面第七种可能的实现方式中任一种,在第八种可能的实现方式中,上述基于任一主设备连接的所有从设备对应的所有传输路径延时,确定任一主设备传输同步信号到与其连接的从设备的基准传输路径延时时,可将任一主设备连接的所有从设备对应的所有传输路径延时中取值最大的传输路径延时确定为任一主设备传输同步信号到与其连接的从设备的基准传输路径延时;或者将任一主设备所属树状结构中同一层的主设备连接的所有从设备对应的所有传输路径延时中取值最大的传输路径延时确定为任一主设备传输同步信号到与其连接的从设备的基准传输路径延时。在本技术中,将传输路径延时中取值最大的传输路径延时作为基准延传输路径延时,从而可提高各个主设备和各个从设备的传输路径延时差的计算便捷性,操作简单,适用性强。

11、结合第一方面第八种可能的实现方式,在第九种可能的实现方式中,上述基于任一主设备连接的各个从设备对应的各个传输路径延时和基准传输路径延时确定任一主设备连接的各个从设备对应的传输路径延时差时,可将基准传输路径延时和任一主设备连接的任一从设备对应的传输路径延时的差值确定为任一从设备对应的传输路径延时差,以得到任一主设备连接的各个从设备对应的传输路径延时差,可提高各个主设备和各个从设备的传输路径延时差的计算便捷性,操作简单,适用性强。

12、结合第一方面至第一方面第九种可能的实现方式中任一种,在第十种可能的实现方式中,上述设备阵列中一个主设备与一个从设备之间的信号传输路径中部署有一个延时补偿模块;上述基于所有主设备连接的各个从设备对应的传输路径延时差对所有主设备连接的所有从设备进行传输路径延时补偿,包括:当任一主设备向其连接的任一从设备传输的同步信号进入任一主设备和任一从设备之间部署的任一延时补偿模块时,通过任一延时补偿模块基于任一从设备对应的传输路径延时差进行系统时钟计数;当任一延时补偿模块的系统时钟计数完成时,通过任一从设备发出同步信号或者发送数据以完成对任一主设备连接的任一从设备的传输路径延时补偿,以此可以实现对所有主设备连接的所有从设备进行传输路径延时补偿。在本技术中,基于延时补偿模块对各个主设备和各个从设备之间的同步信号的传输路径延时进行补偿,可实现传输线路延时的粗补偿,操作简单,可行性高。

13、结合第一方面至第一方面第九种可能的实现方式中任一种,在第十一种可能的实现方式中,上述基于所有主设备连接的各个从设备对应的传输路径延时差对所有主设备连接的所有从设备进行传输路径延时补偿,包括:通过任一主设备的输入输出(inputoutput,io)接口或者任一主设备连接的任一从设备的io接口,配置任一主设备向任一从输出传输的同步信号的输入输出延时等于任一从设备对应的传输路径延时差以完成对任一主设备连接的任一从设备的传输路径延时补偿,以此可以实现对所有主设备连接的所有从设备进行传输路径延时补偿。在本技术中,基于主设备或者从设备的io接口进行传输路径延时的补偿可适配不同的io接口的性能,操作简单,可行性强。

14、结合第一方面至第一方面第九种可能的实现方式中任一种,在第十二种可能的实现方式中,上述数据发送设备的数据输出接口前端部署有延时补偿模块;上述基于所有主设备连接的各个从设备对应的传输路径延时差对所有主设备连接的所有从设备进行传输路径延时补偿,包括:当上述设备阵列中任一数据发送设备输出的数据进入上述任一数据发送设备前端部署的任一延时补偿模块时,通过上述任一延时补偿模块基于上述任一从设备对应的传输路径延时差进行系统时钟计数;当上述任一延时补偿模块的系统时钟计数完成时,通过上述任一数据发送设备向上述数据接收设备发送数据以完成对上述任一主设备连接的上述任一从设备的传输路径延时补偿,以实现对上述所有主设备连接的所有从设备进行传输路径延时补偿。在本技术中,在数据发送设备的数据输出的接口前端部署延时补偿模块,通过对数据输出的延时补偿同样可解决各个主设备到从设备的传输路径延时的补偿,形式多样,从而提高了数据同步传输的操作灵活性,适用性强。

15、结合第一方面第十二种可能的实现方式,在第十三种可能的实现方式中,上述设备阵列中各个上述数据发送设备通过多个串行接串接口向上述数据接收设备发送数据;上述基于所有主设备连接的各个从设备对应的传输路径延时差对所有主设备连接的所有从设备进行传输路径延时补偿,包括:对任一从设备对应的任一数据发送设备输出的串行数据进行移位输出,通过上述任一数据发送设备的io接口配置上述任一数据发送设备移位输出的数据的输入输出延时等于上述任一从设备对应的传输路径延时差,以完成对上述任一主设备连接的上述任一从设备的传输路径延时补偿,以实现对上述所有主设备连接的所有从设备进行传输路径延时补偿。在本技术中,通过数据发送设备的io接口实现对数据输出的延时补偿,同样可解决各个主设备到从设备的传输路径延时的补偿,形式多样,从而提高了数据同步传输的操作灵活性,适用性强。

16、结合第一方面至第一方面第十三种可能的实现方式中任一种,在第十四种可能的实现方式中,上述设备阵列中各个上述数据发送设备通过多个串行接串接口向数据接收设备发送数据,在该方法中还可以基于串行时钟恢复对上述数据接收设备从各个上述数据发送设备接收的数据进行串并转换,以获得多组并行数据,上述多组并行数据中一组并行数据对应一个相位并行时钟。检测任意两组并行数据中多组并行数据的数据边界,并在检测到任意两组并行数据之间的第一数据边界时获得上述第一数据边界到上述任意两组并行数据的第二数据边界的差值以作为上述任意两组并行数据对应的两个相位并行时钟的相位差,基于上述相位差选择目标相位并行时钟,以使上述目标相位并行时钟的时钟沿与上述多组并行数据的数据边界对齐同步。在本技术中,通过对数据接收设备接收的数据进行并行时钟相位的调整可进一步保证不同数据接收通道具有较小的延时差,减少设备阵列中多个数据发送设备向数据接收设备发送数据时各个通道的并行数据之间的偏斜,提高数据同步传输的控制精度,结构简单,适用性强。

17、第二方面,本技术提供了一种设备阵列的数据同步传输装置,该设备阵列中主设备和从设备构成多层树状结构,该多层树状结构中每一层的设备作为主设备连接下一层的多个从设备,该多层树状结构中最后一层的设备为数据发送设备;上述数据同步传输装置包括:获取模块,用于获取设备阵列中各个主设备向与其连接的各个从设备传输同步信号的传输路径延时,其中,任一主设备传输同步信号至与其连接的一个从设备对应一个传输路径延时。延时计算模块,用于基于获取模块获取的任一主设备连接的所有从设备对应的所有传输路径延时,确定任一主设备传输同步信号到与其连接的从设备的基准传输路径延时,并基于任一主设备连接的各个从设备对应的各个传输路径延时和基准传输路径延时确定任一主设备连接的各个从设备对应的传输路径延时差,以得到所有主设备连接的各个从设备对应的传输路径延时差。延时补偿模块,用于基于延时计算模块确定的所有主设备连接的各个从设备对应的传输路径延时差对所有主设备连接的所有从设备进行传输路径延时补偿,以控制设备阵列中各个上述数据发送设备同步向数据接收设备发送数据。

18、结合第二方面,在第一种可能的实施方式中,上述获取模块包括:数据获取单元,用于获取设备阵列中任一主设备向与其连接的任一从设备传输第一同步信号的线路延时,并获取任一主设备和任一从设备使用同频时钟对第一同步信号进行信号检测的时钟相位差。延时获取单元,用于基于数据获取单元获取的时钟相位差和线路延时获得任一主设备向任一从设备传输第一同步信号的传输路径延时,以得到设备阵列中各个主设备向与其连接的各个从设备传输同步信号的传输路径延时。

19、结合第二方面第一种可能的实施方式,在第二种可能的实施方式中,上述数据获取单元包括:第一数据获取子单元,用于获取设备阵列中任一主设备向与其连接的任一从设备输出第一同步信号的第一输出延时,并获取第一同步信号传输至任一从设备并从任一从设备回传至任一主设备的第一时长。第二数据获取子单元,用于获取任一从设备向任一主设备回传第一同步信号的第二输出延时和第一同步信号在任一从设备中停留的第二时长。第三数据获取子单元,用于基于第一数据获取子单元获取的第一输出延时和第一时长,以及第二数据获取子单元获取的第二输出延时和第二时长获得任一主设备和任一从设备之间的线路延时。

20、结合第二方面第二种可能的实施方式,在第三种可能的实施方式中,设备阵列中主设备中包括同步信号传输单元、第一输出接口、第一输入接口和时钟计数器;上述第一数据获取子单元用于:通过任一主设备中的同步信号传输单元同时向时钟计数器和任一主设备连接的任一从设备发送第一测量同步信号,触发时钟计数器开始计数并获取第一测量同步信号通过第一输入接口返回并触发时钟计数器停止计数时时钟计数器的第一计数;按照第一延时步进调整同步信号传输单元通过第一输出接口输出同步信号的输出延时并通过同步信号传输单元向任一从设备发送第二测量同步信号,同时触发时钟计数器开始计数,并在监测到第二测量同步信号返回并触发时钟计数器停止计数时上述时钟计数器的计数比第一计数增加1时,获得调整后的同步信号传输单元通过第一输出接口输出同步信号的输出延时,以作为任一主设备向任一从设备输出第一同步信号的第一输出延时。

21、结合第二方面第三种可能的实施方式,在第四种可能的实施方式中,上述第二数据获取子单元用于:按照上述第一输出延时配置任一主设备向任一从设备输出同步信号的输出延时,通过第一输出接口向任一从设备发送第一同步信号,同时触发时钟计数器开始计数并记录时钟计数器的计数为第二计数;按照第二延时步进调整任一从设备向任一主设备回传同步信号的输出延时并通过第二输出接口向任一主设备回传第一同步信号,在监测到时钟计数器的第二计数增加1时,获得调整后任一从设备向任一主设备输出同步信号的输出延时,以作为任一从设备向任一主设备回传第一同步信号的第二输出延时。

22、结合第二方面第四种可能的实施方式,在第五种可能的实施方式中,上述第一数据获取子单元用于:通过任一主设备中的同步信号传输单元向时钟计数器发送第一同步信号以触发时钟计数器开始计数,同时通过第一输出接口基于第一输出延时向任一从设备发送上述第一同步信号;获取第一同步信号通过任一从设备和第一输入接口返回并触发时钟计数器停止计数时时钟计数器的第三计数,将第三计数对应的时钟周期确定为第一同步信号传输至任一从设备并从任一从设备回传至任一主设备的第一时长。

23、结合第二方面第五种可能的实施方式,在第六种可能的实施方式中,设备阵列中从设备中包括第二输入接口、同步信号检测单元、多个寄存器和第二输出接口;上述第二数据获取子单元用于:当通过同步信号检测单元检测到通过第二输入接口输入的第一同步信号时,通过多个寄存器打拍后通过第二输出接口向任一主设备回传第一同步信号,并将多个寄存器打拍对应的时钟周期确定为第一同步信号在任一从设备中停留的第二时长。

24、结合第二方面第一种可能的实施方式至第二方面第六种可能的实现方式中任一种,在第七种可能的实施方式中,上述数据获取单元用于:基于任一主设备向任一从设备传输第一同步信号的线路延时和上述同频时钟的时钟周期获得参考线路延时;基于参考线路延时、任一主设备向任一从设备输出第一同步信号的第一输出延时和上述时钟周期的周期时长,获得任一主设备和任一从设备使用同频时钟对第一同步信号进行信号检测的时钟相位差。

25、结合第二方面第一种可能的实施方式至第二方面第七种可能的实现方式中任一种,在第八种可能的实施方式中,上述延时计算模块用于:将任一主设备连接的所有从设备对应的所有传输路径延时中取值最大的传输路径延时确定为任一主设备传输同步信号到与其连接的从设备的基准传输路径延时;或者将任一主设备所属树状结构中同一层的主设备连接的所有从设备对应的所有传输路径延时中取值最大的传输路径延时确定为任一主设备传输同步信号到与其连接的从设备的基准传输路径延时。

26、结合第二方面第一种可能的实施方式至第二方面第八种可能的实现方式中任一种,在第九种可能的实施方式中,上述延时计算模块用于:将基准传输路径延时和任一主设备连接的任一从设备对应的传输路径延时的差值确定为任一从设备对应的传输路径延时差,以得到任一主设备连接的各个从设备对应的传输路径延时差。

27、结合第二方面至第二方面第九种可能的实现方式中任一种,在第十种可能的实施方式中,上述延时补偿模块包括部署于设备阵列中各个主设备与一个从设备之间的信号传输路径中的多个延时补偿单元;上述延时补偿模块用于:当任一主设备向其连接的任一从设备传输的同步信号进入任一主设备和任一从设备之间部署的任一延时补偿单元时,通过任一延时补偿单元基于任一从设备对应的传输路径延时差进行系统时钟计数;当任一延时补偿模块的系统时钟计数完成时,通过任一从设备发出同步信号或者发送数据以完成对任一主设备连接的任一从设备的传输路径延时补偿,以实现对所有主设备连接的所有从设备进行传输路径延时补偿。

28、结合第二方面第一种可能的实施方式至第二方面第九种可能的实现方式中任一种,在第十一种可能的实施方式中,上述延时补偿模块用于:通过任一主设备的输入输出io接口或者任一主设备连接的任一从设备的io接口,配置任一主设备向任一从输出传输的同步信号的输入输出延时等于任一从设备对应的传输路径延时差以完成对任一主设备连接的任一从设备的传输路径延时补偿,以实现对所有主设备连接的所有从设备进行传输路径延时补偿。

29、结合第二方面第一种可能的实施方式至第二方面第九种可能的实现方式中任一种,在第十二种可能的实施方式中,上述延时补偿模块包括部署于数据发送设备的数据输出接口前端的多个延时补偿单元;上述延时补偿模块用于:当设备阵列中任一数据发送设备输出的数据进入任一数据发送设备前端部署的任一延时补偿单元时,通过上述任一延时补偿单元基于上述任一从设备对应的传输路径延时差进行系统时钟计数;当上述任一延时补偿单元的系统时钟计数完成时,通过上述任一数据发送设备向数据接收设备发送数据以完成对任一主设备连接的任一从设备的传输路径延时补偿,以实现对所有主设备连接的所有从设备进行传输路径延时补偿。

30、结合第二方面至第二方面第十二种可能的实施方式中任一种,在第十三种可能的实施方式中,上述设备阵列中各个上述数据发送设备通过多个串行接串接口向上述数据接收设备发送数据;上述延时补偿模块用于:对任一从设备对应的任一数据发送设备输出的串行数据进行移位输出,通过任一数据发送设备的io接口配置任一数据发送设备移位输出的数据的输入输出延时等于任一从设备对应的传输路径延时差,以完成对任一主设备连接的任一从设备的传输路径延时补偿,以实现对所有主设备连接的所有从设备进行传输路径延时补偿。

31、结合第二方面第十种可能的实施方式至第二方面第十三种可能的实现方式中任一种,在第十四种可能的实施方式中,上述设备阵列中各个上述数据发送设备通过多个串行接串接口向上述数据接收设备发送数据,上述数据同步传输装置还包括:数据转换模块,用于基于串行时钟恢复对数据接收设备从各个数据发送设备接收的数据进行串并转换,以获得多组并行数据,上述多组并行数据中一组并行数据对应一个相位并行时钟;数据检测模块,用于检测数据转换模块获得的任意两组并行数据的数据边界,并在检测到任意两组并行数据之间的第一数据边界时获得第一数据边界到上述任意两组并行数据的第二数据边界的差值以作为上述任意两组并行数据对应的两个相位并行时钟的相位差;相位补偿模块,用于基于上述数据检测模块得到的上述相位差选择目标相位并行时钟,以使上述目标相位并行时钟的时钟沿与上述多组并行数据的数据边界对齐同步。

32、第三方面,本技术提供了一种数据传输设备,包括:处理器和存储器;上述存储器用于存储指令;上述处理器用于执行上述指令,以使第一方面及其任一种可能的实施方式提供的方法被执行。

33、第四方面,本技术提供了一种计算机可读存储介质,上述计算机可读存储介质用于存储计算机程序,当上述计算机程序被执行时,第一方面及其任一种可能的实施方式提供的方法被执行。

本文地址:https://www.jishuxx.com/zhuanli/20240731/193851.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表